### Some pages of this thesis may have been removed for copyright restrictions.

If you have discovered material in AURA which is unlawful e.g. breaches copyright, (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please read our <u>Takedown Policy</u> and <u>contact the service</u> immediately

#### TWO WAY POWER FLOW USING GTO THYRISTORS

#### MOHAMAD HUSSEIN TAHA

Doctor of Philosophy

#### THE UNIVERSITY OF ASTON IN BIRMINGHAM

August 1992

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the author's prior, written consent.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks to my supervisor the late Mr. B. James and to my adviser Mr. L. Babad for all their advice, suggestions and help. I would also like to thank Professor W. T. Norris who has recently assisted with the supervision of the project.

I am grateful to Mr. B. Harrison and Mr. L. Radford for all their help with the laboratory work.

A special mention must go to my sponsors the Hariri Foundation who are entirely responsible for the funding of this project.

I would like to express my thanks and love to my wife Sonia for her help, encouragement and support. My love and thanks also to my children Sophia, Miriam and Hussein. Finally, my thanks and love to all my family in Lebanon for their moral support throughout my studies.

## LIST OF CONTENTS.

|               |                                    | page |

|---------------|------------------------------------|------|

| SUMMARY.      |                                    | 1    |

| ACKNOWLEDGE   | MENTS.                             | 2    |

| LIST OF CONTE | NTS.                               | 3    |

| LIST OF SYMBO | LS.                                | 6    |

| CHAPTER ONE:  | LITERATURE SURVEY AND              |      |

|               | RESEARCH LAYOUT.                   |      |

| 1-2           | Introduction.                      | 8    |

| 1-2           | A bi-directional AC-DC power flow. | 11   |

| 1-3           | A bi-directional AC-AC power flow. | 13   |

| 1-4           | Research layout.                   | 16   |

| CHAPTER TWO:  | GTO THYRISTOR                      |      |

| 2-1           | Introduction.                      | 22   |

| 2-2           | Turn-on characteristics.           | 25   |

| 2-3           | Turn-off characteristics.          | 25   |

| 2-4           | Snubber circuit.                   | 29   |

| 2-5           | GTO gate drive circuit.            | 31   |

| 2-5-1         | Delay circuit.                     | 38   |

| 2-5-2         | MOSFET1 drive stage.               | 42   |

| 2-5-3         | MOSFET2 drive stage.               | 42   |

| 2-5-4         | MOSFET3 drive stage.               | 43   |

| 2-6           | GTO testing circuit.               | 49   |

# CHAPTER THREE: PRELIMINARY INVESTIGATION FOR TWO WAY POWER FLOW.

|      | 3-1       | Introduction.                             | 56  |

|------|-----------|-------------------------------------------|-----|

|      | 3-2       | System operation                          | 56  |

|      | 3-3       | Centre tap inverter.                      | 57  |

|      | 3-3-1     | Thyristor firing circuit.                 | 59  |

|      | 3-3-2     | Thyristor turn-off time.                  | 64  |

|      | 3-4       | GTO inverter/rectifier drive pulses.      | 70  |

|      | 3-5       | Transistor drive circuit.                 | 70  |

|      | 3-6       | Control circuit.                          | 75  |

|      | 3-7       | Power flow in two directions.             | 78  |

|      |           |                                           |     |

| CHAI | PTER FOUR | : SINGLE PHASE TWO WAY                    |     |

|      |           | POWER FLOW.                               |     |

|      |           |                                           |     |

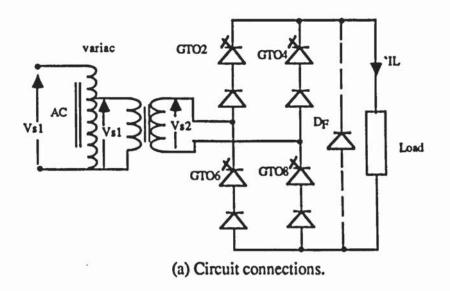

|      | 4-1       | Introduction.                             | 80  |

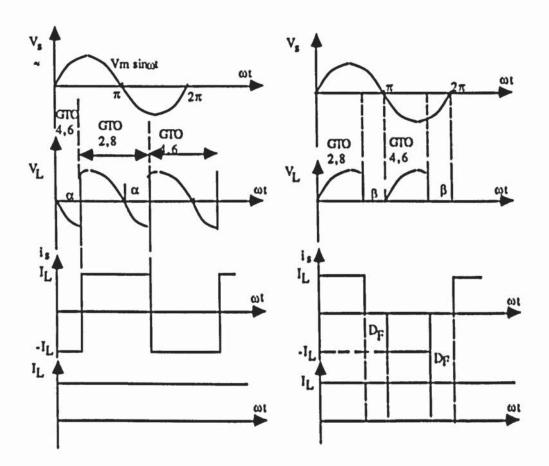

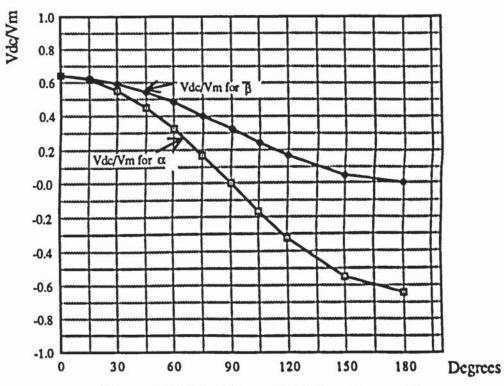

|      | 4-2       | System operation                          | 80  |

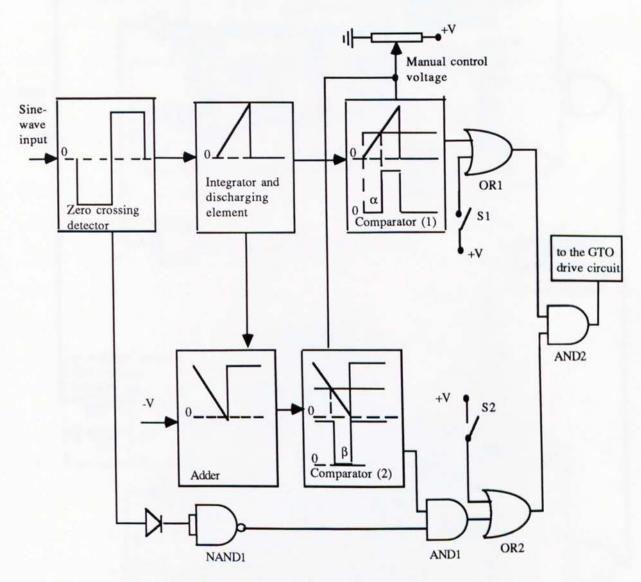

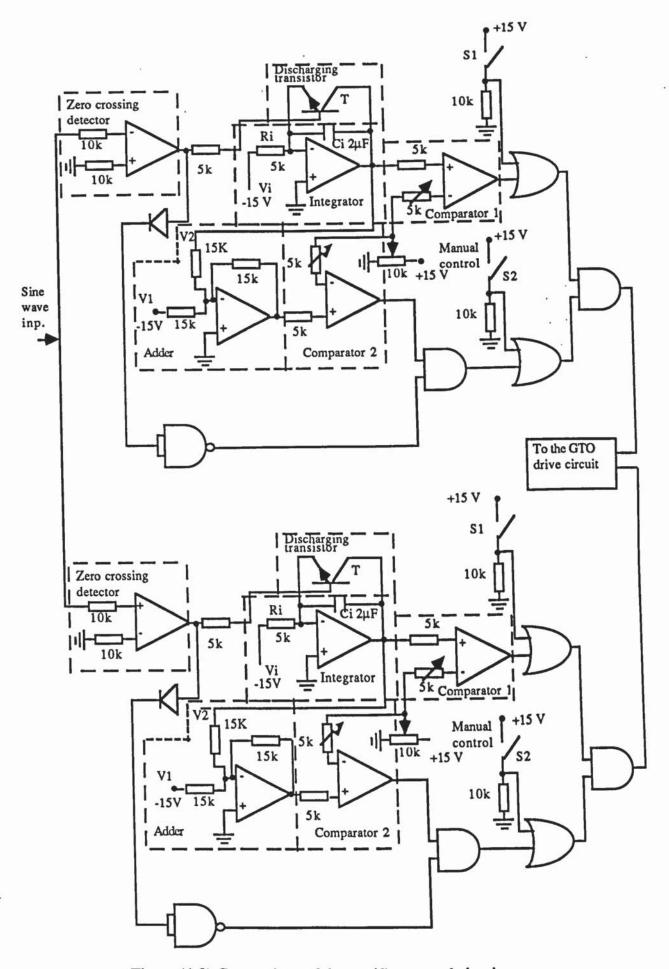

|      | 4-3       | System control circuit                    | 89  |

|      | 4-4       | Rectifier control circuit.                | 89  |

|      | 4-4-1     | Zero crossing detector.                   | 92  |

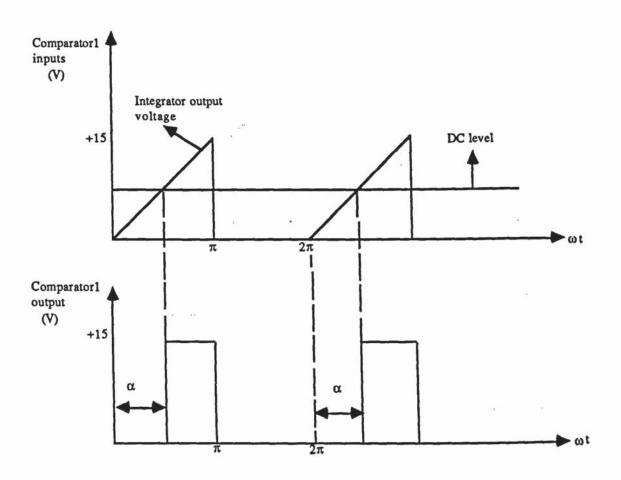

|      | 4-4-2     | Integrator.                               | 92  |

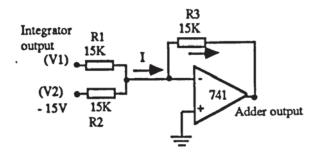

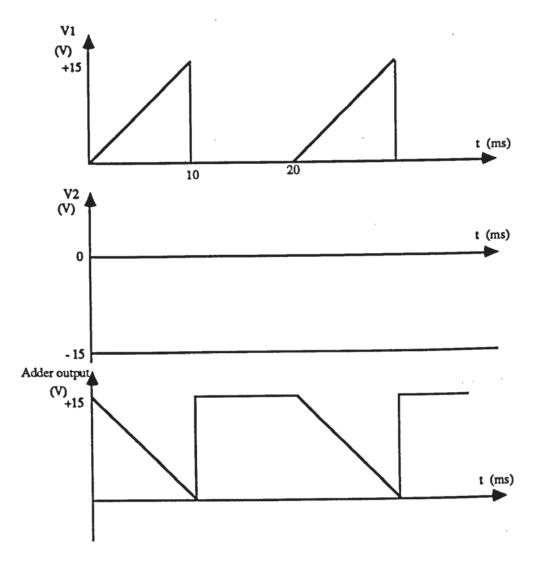

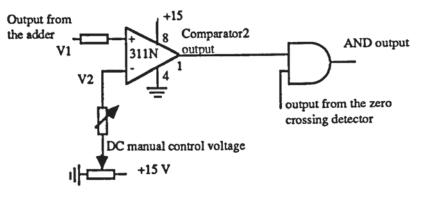

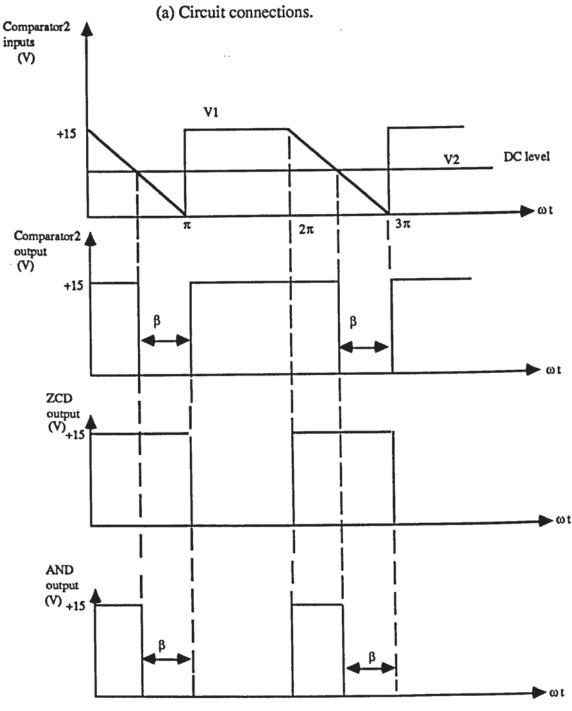

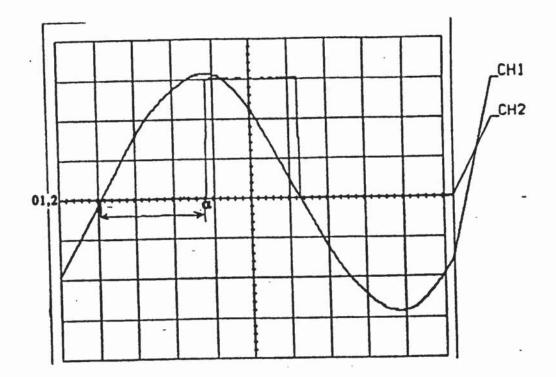

|      | 4-4-3     | Controlling angles $\alpha$ and $\beta$ . | 92  |

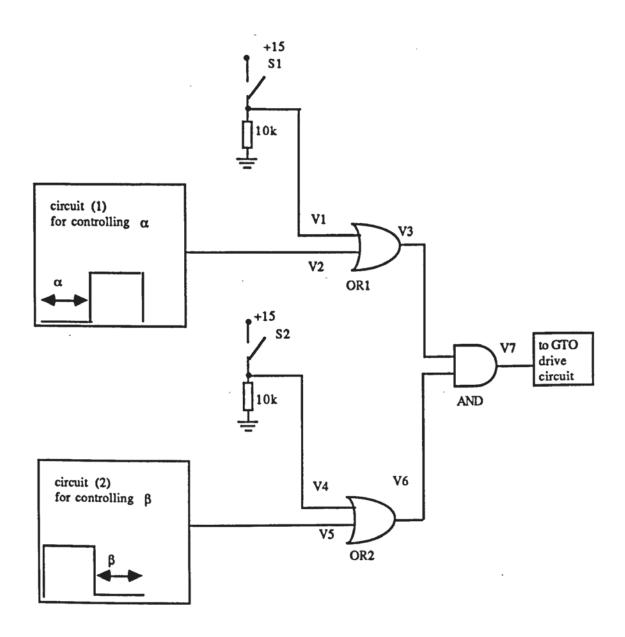

|      | 4-5       | Inverter drive pulses.                    | 101 |

|      | 4-6       | Transistors base drives.                  | 101 |

|      | 4-7       | Overall operation of the systems          | 104 |

## CHAPTER FIVE: EXPERIMENTAL RESULTS

| 5-1          | Introduction.                                            | 109 |

|--------------|----------------------------------------------------------|-----|

| 5-2          | Voltage transient of the switching transistor.           | 109 |

| 5-3          | Reduction of the capacitor inrush current.               | 116 |

| 5-4          | Experimental results with a resistive load.              | 120 |

| 5-5.         | Experimental results with an inductive load.             | 130 |

| 5-6          | Power factor improvement.                                | 139 |

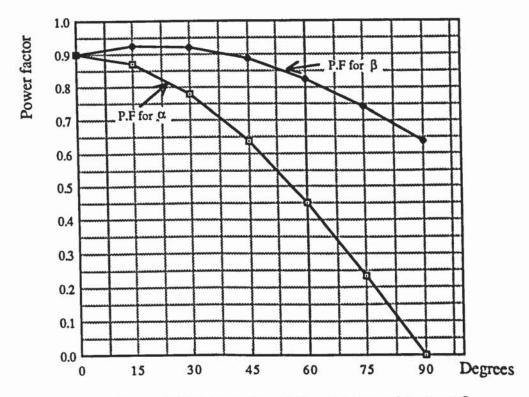

| 5-6-1        | Rectifier power factor for variation of angle $\alpha$ . | 140 |

| 5-6-2        | Rectifier power factor for variation of angle $\beta$ .  | 141 |

|              | *                                                        |     |

| CHAPTER SIX. | CONCLUSIONS AND SUGGESTIO                                | NS  |

|              | FOR FURTHER WORK.                                        |     |

|              |                                                          |     |

| 6-1          | Conclusions.                                             | 151 |

| 6-2          | Suggestions for further work.                            | 153 |

|              |                                                          |     |

| REFERENCES   |                                                          | 155 |

| APPENDIX A.  | GTO DATA SHEET.                                          | 161 |

| APPENDIX B.  | INVERTER OPERATION WITH A PURE                           | LY  |

|              | INDUCTIVE LOAD                                           | 164 |

| APPENDIX C.  | DELAY CIRCUIT FOR AN INVERTER                            |     |

|              | DEVICES.                                                 | 167 |

| APPENDIX D.  | INVERTER CIRCUIT WITH RL LOAD.                           | 169 |

| APPENDIX E.  | THYRISTOR TURN OFF TIME                                  | 173 |

| APPENDIX F.  | HEAT SINK REQUIREMENT FOR GTO.                           | 178 |

| APPENDIX G.  | HIGH FREQUENCY SHUNT DATA                                |     |

|              | SHEET.                                                   | 183 |

|              |                                                          |     |

#### LIST OF SYMBOLS

$\alpha, \beta$  Rectifier firing angles.

$\alpha(pnp),(\alpha npn)$  Transistor current amplifications.

CSI Current source inverter.

C<sub>S</sub> Snubber capacitor

D<sub>F</sub> Free-wheeling diode.

D<sub>S</sub> Snubber diode.

E<sub>d</sub> Centre tap inverter input voltage.

I<sub>A</sub> GTO anode current.

I<sub>DC</sub> Rectifier output current.

I<sub>FG</sub> GTO forward gate current.

I<sub>CO</sub> GTO reverse gate current.

I<sub>G(on)</sub> GTO on-state gate current.

I<sub>L</sub> Mean load current.

I<sub>T</sub> GTO on-state current

I<sub>TAIL</sub> GTO tail current.

f Frequency.

L<sub>x</sub> Stray inductance.

P.F. Power factor.

P<sub>mean</sub> Mean power.

P.S U. Power supply unit.

R<sub>S</sub> Snubber resistor.

Q<sub>CO</sub> GTO turn-off gate charge.

V<sub>AK</sub> GTO anode-cathode voltage.

V<sub>D</sub> GTO continuous direct off-state voltage.

V<sub>DC</sub> Rectifier output voltage.

V<sub>DM</sub> GTO turn-off voltage.

V/F Voltage to frequency converter.

V<sub>m</sub> AC maximum voltage.

V<sub>DP</sub> GTO peak forward transient voltage.

| $V_{RG}$         | GTO reverse gate voltage.                         |  |

|------------------|---------------------------------------------------|--|

| $W_S$            | Snubber energy.                                   |  |

| $t_d$            | Delay time.                                       |  |

| $t_{gf}$         | Fall time                                         |  |

| t <sub>gs</sub>  | Storage time                                      |  |

| t <sub>r</sub>   | Rise time.                                        |  |

| T,TR             | Transistor.                                       |  |

| $t_{\mathbf{q}}$ | Thyristor turn-off time.                          |  |

| μ                | Operational amplifier gain.                       |  |

| η                | Efficiency.                                       |  |

| 01               | Zero level of the oscilloscope Channel 1.         |  |

| 02               | Zero level of the oscilloscope Channel 2.         |  |

| 03               | Zero level of the oscilloscope Channel 3.         |  |

| 04               | Zero level of the oscilloscope Channel 4.         |  |

| 01,2             | Common zero of the oscilloscope Channels 1 and 2. |  |

| 03,4             | Common zero of the oscilloscope Channels 3 and 4. |  |

#### CHAPTER ONE

#### LITERATURE SURVEY AND RESEARCH LAYOUT

#### 1-1 INTRODUCTION.

There are many industrial applications that require bidirectional power transfer between two systems and there are a number of methods by which this is currently performed. Before starting with a survey of these methods, it is important to give a simple explanation of reversal of power flow within the power electronics area.

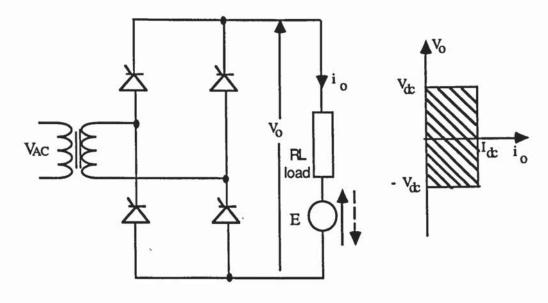

The simplest system to demonstrate the idea of bidirectional power flow is perhaps the single phase fully controlled line commutated thyristor converter. This type of converter has the advantage that its power control switching devices can be commutated by its own voltage supply without any additional external circuit or commutation function (1). Figure (1-1-a) shows a single phase fully controlled thyristor converter with a highly inductive load. The converter also contains a voltage source (E) which may be reversed, depending upon the required operation of the converter.

The DC output voltage equals:

$$V_{dc} = \frac{1}{\pi} \int_{\alpha}^{\alpha + \pi} V_{m} \sin\omega t \, d(\omega t)$$

(1-1)

Where  $\alpha$  is the firing-angle of the thyristor, measured from the natural commutation point. For a single phase system,  $\alpha$  measured from the zero crossing of each half cycle of the input supply voltage. The firing angle  $\alpha$  can be varied from a small value to almost 180 degrees. Up to a delay of 90 degrees, the voltage source is connected in the direction of the full arrow (refer to figure (1-1), the converter operates in rectification mode and the power flows from the supply to the load. The DC output voltage and current are positive. If the firing angle increases beyond 90 degrees and

the voltage source is reversed as shown by the dotted arrow, the DC output voltage will be negative but the current remains positive. There will be a reverse power flow from the load to the supply and the converter will operate in the inversion mode (1-8).

If a DC machine is used as the load element, it acts as a motor while the converter is rectifying. When the firing angle increases beyond 90 degrees, the DC machine acts as a generator, but since the current direction cannot reverse, the machine can only generate by having its armature or field connections reversed (2).

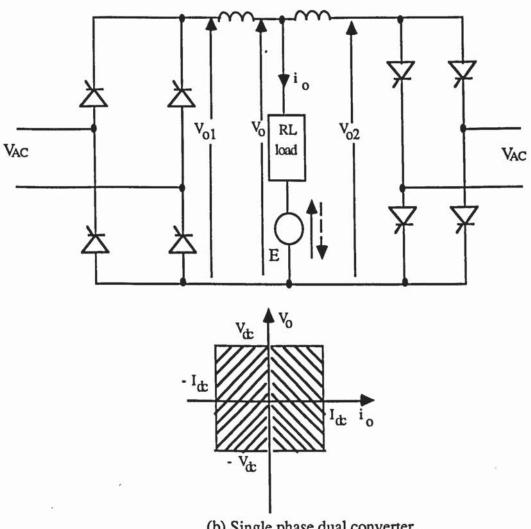

If two full converter bridges are connected back to back as shown in figure (1-1-b), the output voltage and current can be reversed. The system will provide four-quadrant operation and is called a dual (3) or double (4) converter. The firing angles are controlled so that one converter operates as a rectifier and the other operates as an inverter. Dual converters are normally used in high power variable drives and in HVDC.

There are several problems in the use of this type of converter (1,9-12):

- a) The power factor decreases as the firing angle increases.

- b) The harmonics of the line current are relatively high.

In this chapter some of the published work for tackling the above problems is discussed. The advantages and layout of the author's research is presented at the end of the chapter.

(a) Single phase converter.

(b) Single phase dual converter.

Figure (1-1)Fully controlled bridge converters.

#### 1-2 A BI-DIRECTIONAL AC-DC POWER CONVERTER.

A forced commutated AC-DC converter is able to draw nearly sinusoidal current at unity power factor and power exchange between the AC line and DC load or viceversa by reversal of the direct current (10-13).

Recent evolution of power devices with high frequency switching such as the bipolar transistor, MOSFET and GTO have made possible the use of PWM to serve the above purposes. A number of papers on the three-phase controlled current PWM rectifier have reported on its capability for fast power reversal while feeding near sinusoidal input current with unity power factor (14,15).

In the past decade, great progress has been made in switching mode converters (16,17). Among these, the conventional and most widely used is perhaps the sinusoidal PWM switching mode converter (16). This converter is simple in construction, but has the disadvantage of having high voltage switching transients and losses (18).

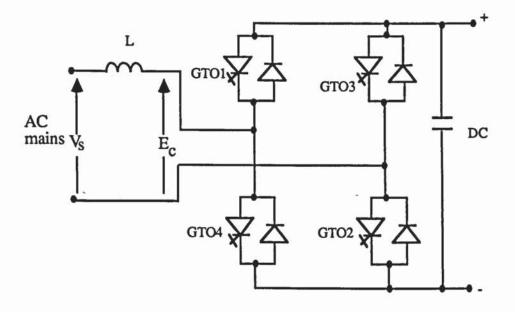

Recently, converters based on the current forced switching control technique have been developed (19,20), in which the device can be operated with a sinusoidal line current, unity power factor and a regulated busbar voltage in the converter mode. In references (10) and (11-13) respectively, single-phase and three-phase converters have been presented. PWM is employed for rectification and inversion modes. Figure (1-2) shows a single phase GTO converter; between the mains and the input of the converter there is an inductor. The fundamental component of the AC voltage waveform developed by the converter (E<sub>C</sub>) is adjustable in magnitude and phase with respect to the AC mains (V<sub>S</sub>) (10). The direction of the power flow is dependent on the magnitude and phase between the two voltages (13). The detail of the control circuit is not explained here, however the above references reported that with PWM control techniques for rectification and inversion modes, reversal of power flow

between AC and DC side can be achieved with unity power factor and a sinusoidal input current.

In references (18-21), a current-forced hystereris switching control technique with a forced commutated converter has been used. The configuration is similar to figure (1-2). In the rectifier mode of operation, the input AC current is forced to track a sinusoidal reference waveform. When the input current is less than the reference current, the magnetic energy in the inductor must increase and this can be achieved by circulating the input current between a diode and a controlled device. When the input current is higher than the reference current, the incremental magnetic energy stored in the inductor is released to the load via the antiparallel diodes. The reference current is synchronised with the utility voltage source and this always gives a unity power factor. In the case of inverter operation, the devices will operate differently to the rectifier mode. Thus a sinusoidal output voltage waveform can be obtained. The above references reported reversal of power flow between the AC mains and DC load with unity power factor.

In reference (22), simulation of a three phase bi-directional power flow system using GTOs has also been reported. The authors of the paper concentrated their study on the system harmonics. Reference (22) reports that the use of a forced commutated converter creates a harmonic spectrum better than the line commutated one.

In references (23) and (24), a three phase PWM AC to DC converter using thyristors as switching devices has been discussed. The main disadvantage of this system is the requirement of a commutation circuit for each thyristor.

However the main disadvantage of the work described in the above references is that, it is difficult to control the power factor in cases when the system needs to operate at leading or lagging power factors.

#### 1-3 BI-DIRECTIONAL AC-AC POWER FLOW.

In any AC-AC system, static power converters constitute an interface between the mains and the load, usually an induction machine is used as the load element. The static power converters adapt and control the energy flow to provide AC power at the input of the machine. The conversion of AC-AC could be passed through two stages AC-DC and DC-AC converters (AC/DC/AC) or one stage AC-AC converter, some applications of these types of conversions are presented in the following sections.

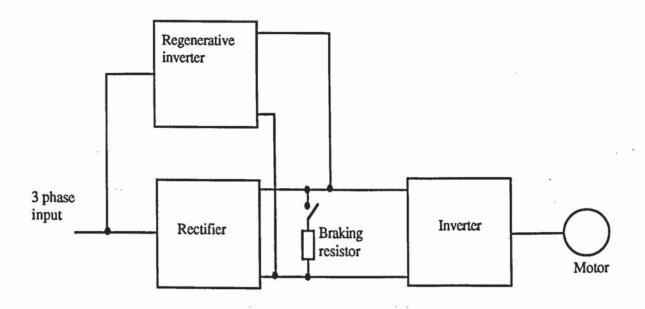

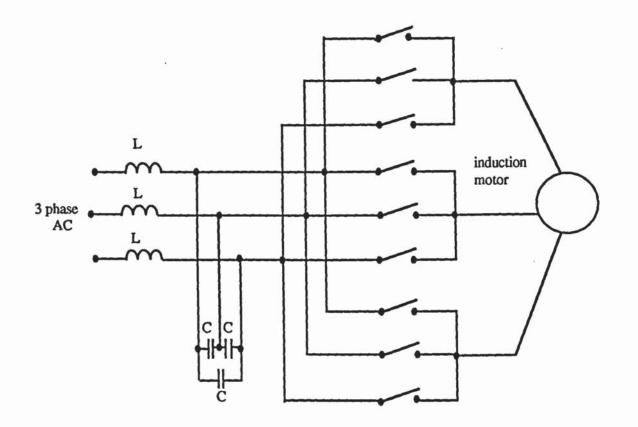

The rectifier stage of the AC/DC/AC converters, consists of an uncontrolled diode bridge or, less frequently, of a phase controlled thyristor converter. This results in a high harmonic content in the input AC line current and gives an input power factor which is dependent on the phase angle of the rectifier. The other disadvantage of this type of converter is that when the motor is regenerating, the stored energy is being returned to the DC link. This raises the DC link voltage by increasing the charge on the DC link capacitor. Unless this energy can be returned to the fixed frequency source using a converter in the inverting mode, regeneration is very limited. The energy can be dissipated in a braking resistor placed across the DC link and this is a form of dynamic braking (2). These two methods of braking are illustrated in figure (1-3). The disadvantage of the regenerative inverter configuration is that three different converters with two different units are needed. In the case of the braking resistor, there is wasted energy especially with high power induction motors.

Different techniques for AC-AC bi-directional power flow have been used. References (26-29) used a configuration called a matrix converter which is shown in figure (1-4). The nine switches in this circuit are arranged in a "matrix", and are switched sequentially and cyclically, such that any phase of the three-phase input can be connected to any phase of three-phase output, with either polarity of the voltage input or current output. The switches are assumed to have bi-directional voltage blocking ability as well as bi-directional current conduction and turn-off capability (25). A conventional bipolar junction transistor inside a bridge diode, or an inverse

parallel connection of transistors could be used as a switch element of the system of figure (1-4). It has been shown by Venturini (27-29) that with the proper switching algorithm, the matrix converter is capable of operating at lagging, unity, or even leading power factor at a variable frequency. Four-quadrant operation can be obtained with this type of converter, i.e., motor or generating operation with either leading or lagging current.

The distinguishing feature of this converter is the complete absence of a DC link. No energy capacitor or inductor is needed to support the link voltage or current. However, relatively small capacitors will generally be needed to isolate the converter from the inevitable inductance of the supply.

The main disadvantages (25) of this converter are:

- a) The high device losses and the device cost have so far prevented this converter from having much of an impact on the converter market.

- b) The output voltage is limited to 1/2 the input voltage.

- c) The switching instants must be carefully controlled; since current spikes could occur in the switch currents if overlap exists between gating signals, while a voltage spike could occur across the switch if a gap exists between switch gating signals.

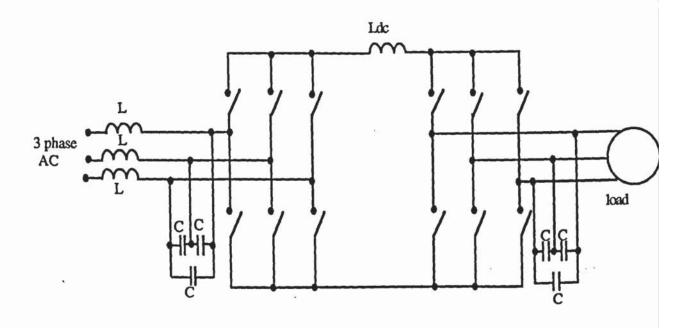

Another technique used in references (30-32), is a DC link current converter utilizing PWM technique for both the input and output bridges. The configuration is shown in figure (1-5). The implementation of the PWM techniques requires gate turn-off switching devices such as bipolar transistors, MOSFETs or GTOs to be used as unilateral switches (33). This configuration comprises a converter section to convert the constant frequency AC power from the commercial power source to DC power, a reactor to smooth the DC current and an inverter section to convert the DC power to the variable voltage variable frequency AC power (30). The capacitors are connected to both input and output sides to absorb the overvoltages which occur when the switch current cuts off. Sinusoidal current can be derived at both the input and

output lines and four-quadrant operation is readily obtained by simply reversing the polarity of the DC link voltage. This type of converter is used with a medium power (several hundred horse power) level but is not generally favoured because of the expensive and bulky passive components (33).

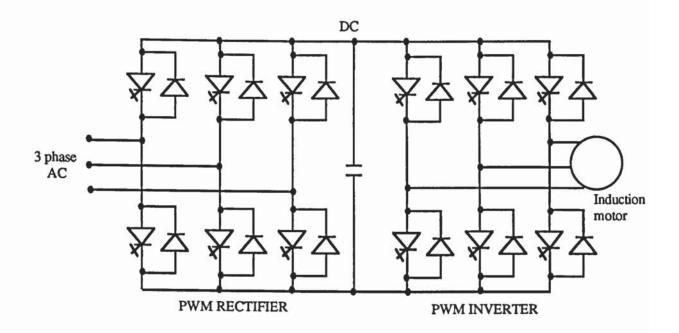

The three-phase current-controlled PWM rectifier/inverter DC voltage link shown in figure (1-6) has been reported in references (34-35). The current-controlled PWM converter merits attention due to its ability to deliver near sinusoidal currents at unity power factor. In addition the converter permits bidirectional DC current flow without the need for dual converters. In this configuration, both the rectifier and the inverter are identical. The current in each phase tracks a reference current waveform. Under the rectification mode of operation, the current path is preponderantly through the diodes, and under the inverter operation the current flows preponderantly through the forced commutated devices. Reference (36) used the same control technique but with a single phase system which can be useful to drive an AC traction motor from a single phase supply. Although a reversal of power flow with unity power factor was achieved with this type of converter, the main disadvantage is that, it is difficult to control the power factor in case the system needed to operate at leading or lagging power factors.

It is also possible to utilize a dual PWM converter for a resonant AC/DC link converter to achieve a reversal of power flow with unity power factor as has been mentioned and discussed in references (37-42). The advantage of these converters compared with the conventional DC voltage or current link converters is that the devices can operate without snubbers and with very little heat sinking. This is due to the zero voltage switching. However, the size and cost of the link inductor and capacitor are major inhibiting factors.

#### 1-4 RESEARCH LAYOUT.

The previous sections outlined the many techniques which are used to reverse power flow between AC and DC or AC and AC systems. Nearly all the references used an antiparallel diode with a forced commutated device for each converter arm. It was mentioned that the main disadvantage of the schemes of these references is the difficulty of controlling the power factor in case the system is needed to operate at leading or lagging power factor. However a new system using GTOs thyristor was built and studied for reversing the power flow in both directions. The main difference with the new system is that two antiparallel GTOs are used instead of a diode and a GTO. The advantages and disadvantages of the system is discussed at the end of this section.

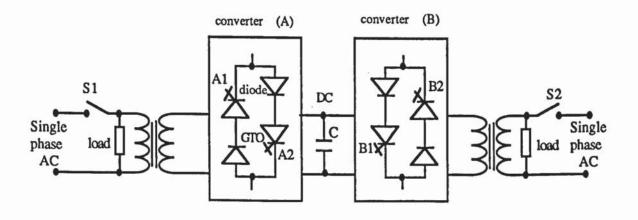

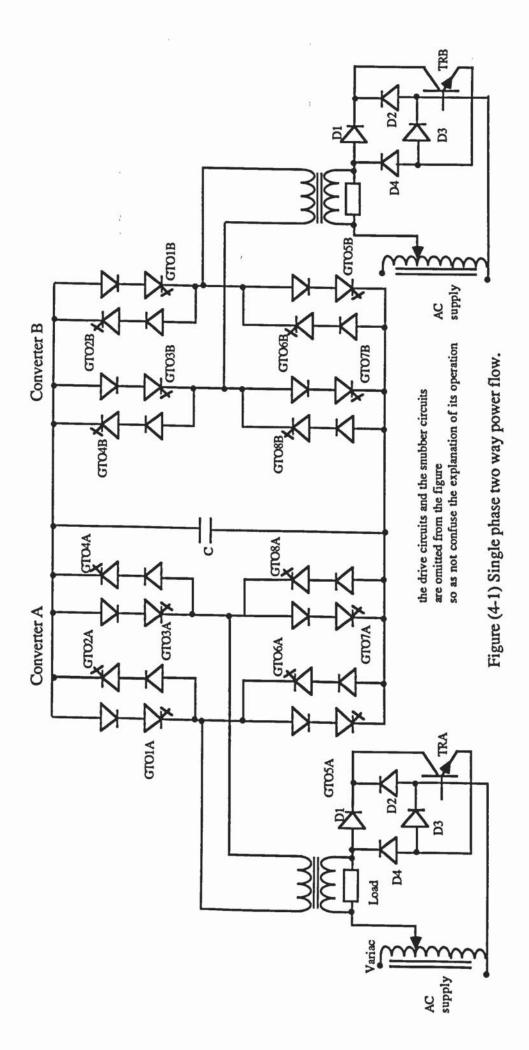

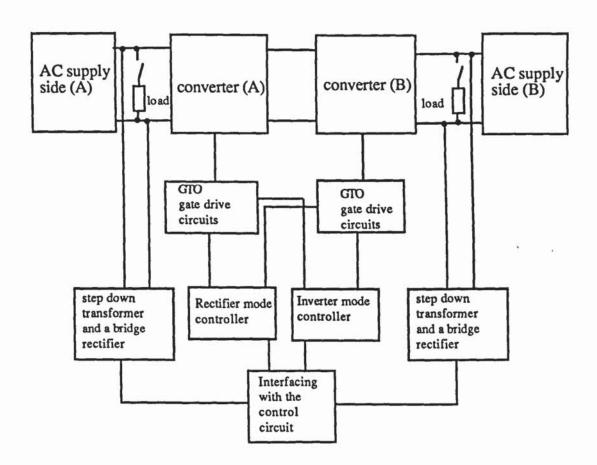

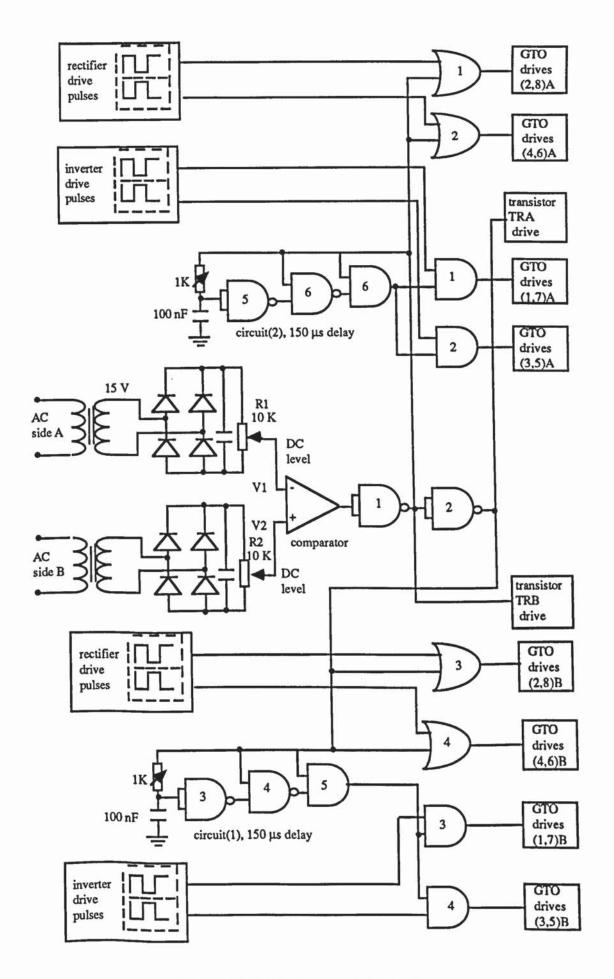

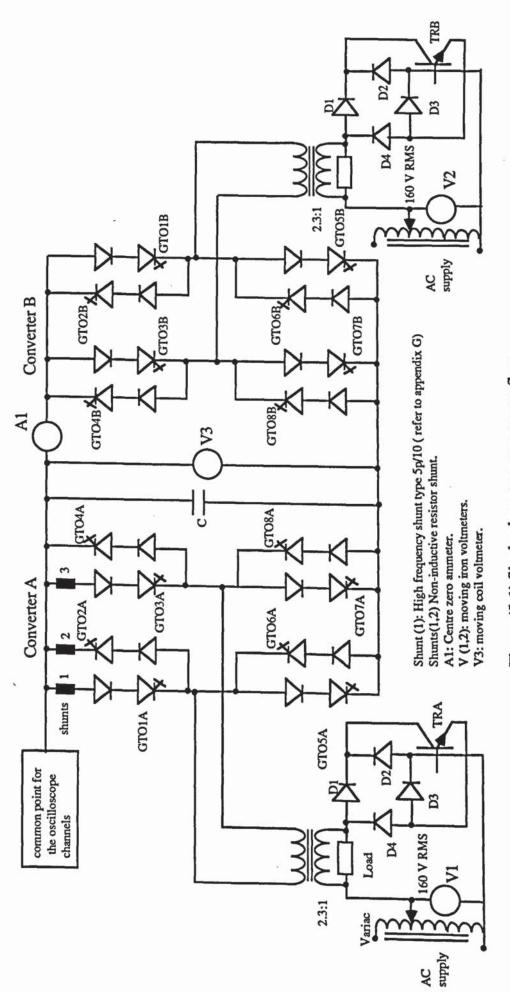

Originally the idea of the project was to build a three-phase system containing two GTOs converters connected in series, with each converter containing 12 antiparallel GTOs. However, due to lack of time and practical difficulties such as late delivery of components, the project was modified to a single-phase system as shown in the block diagram of figure (1-7). Two single phase converters are connected in series. Each converter contains 8 antiparallel GTOs. When power flows from side (A) to side (B), S1 closes and the AC mains supplies converter (A). This operates as a rectifier, by switching GTOs(A2) on as controlled devices and switching GTOs(A1) off. The output of rectifier (A) supplies the input of converter (B), which operates as an inverter. This can be achieved by switching GTOs(B2) continuously on, thus operating them as diodes and switching GTOs(B1) on to carry the inverter current. S2 must turn-off, to disconnect the supply from converter (B). The power from inverter (B) is fed to the load. When power flows from side (B) to side (A), converter (B) operates as a rectifier and converter (A) operates as an inverter. There is a switch at the input of each converter, since there is no synchronization between the system and the mains. This was due to the shortage of time which prevented synchronization the output of each converter with the mains.

The main objectives of the project were to study and investigate the reversal of the power flow between the two converters under steady-state and transient conditions and to investigate and control the rectifier power factor.

A brief outline of the various stages of the work is presented below.

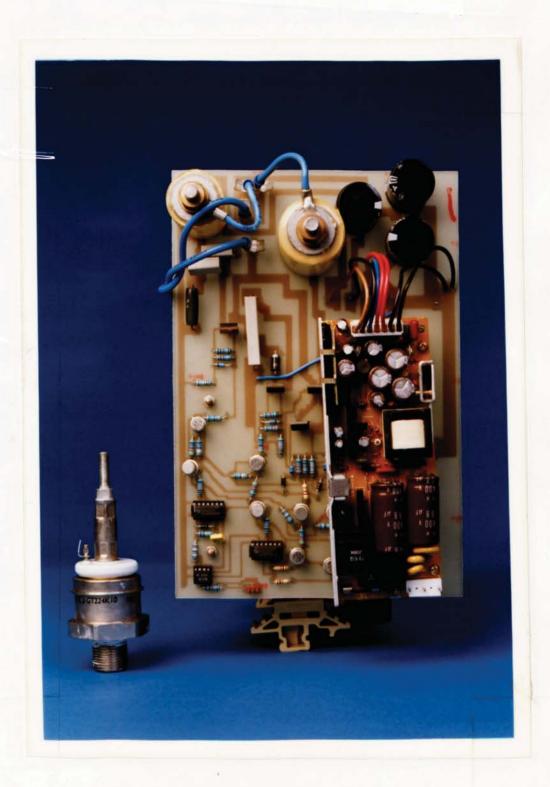

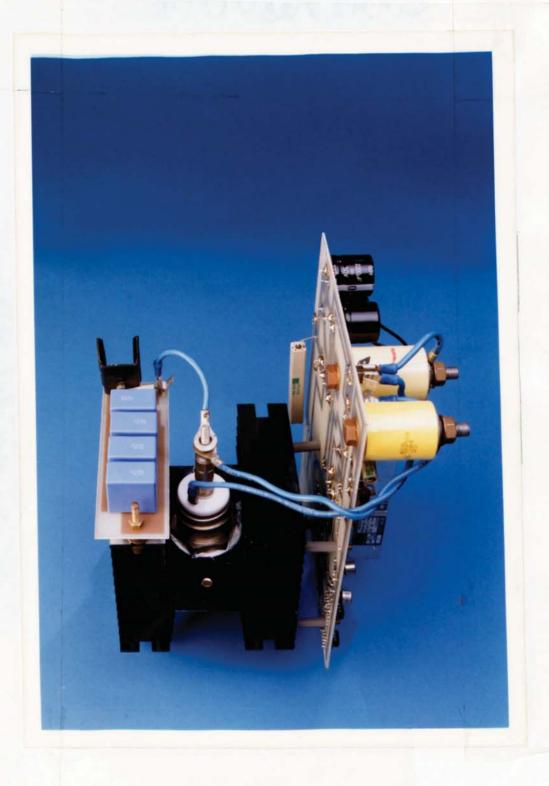

- a) An amount of time was spent to design and study a GTO drive circuit. Later some time was spent learning the technique for designing a PCB for the GTO gate drive. The work was done in the university laboratory using a computer software package called a 'Smartwork PCB draughting software'. The design, diagrams and explanations of the gate drive circuit and the switching behaviour of the GTO used in this research are shown in Chapter 2.

- b) A small system of about 100 W rating was designed and built to study and investigate the reversal of power flow between two units. The design and results of the system are presented in Chapter 3.

- c) As mentioned at the beginning of this chapter, one of the objectives of the system was to control the rectifier power factor. The author designed a rectifier control circuit which gave the choice of operating the system with either leading or lagging power factor. The full details of this circuit and the system control circuit are presented in Chapter 4.

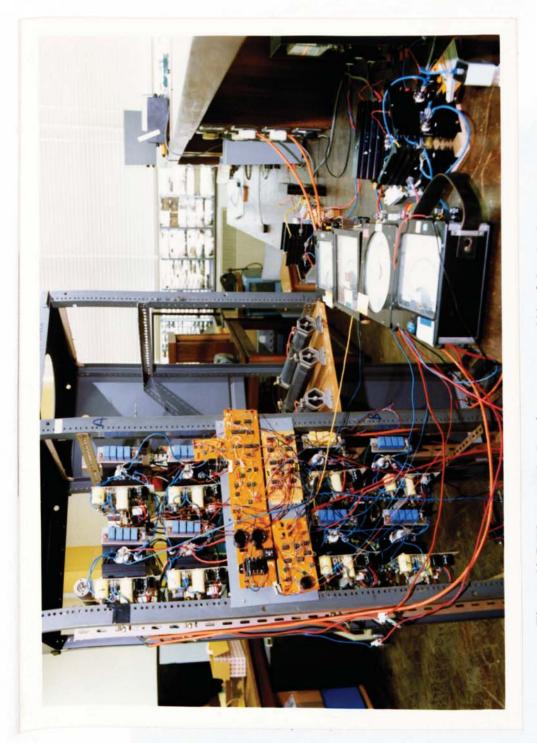

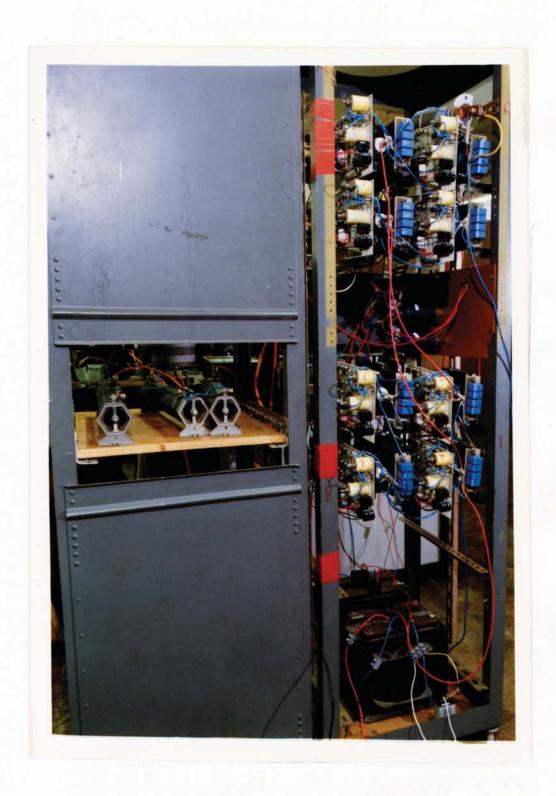

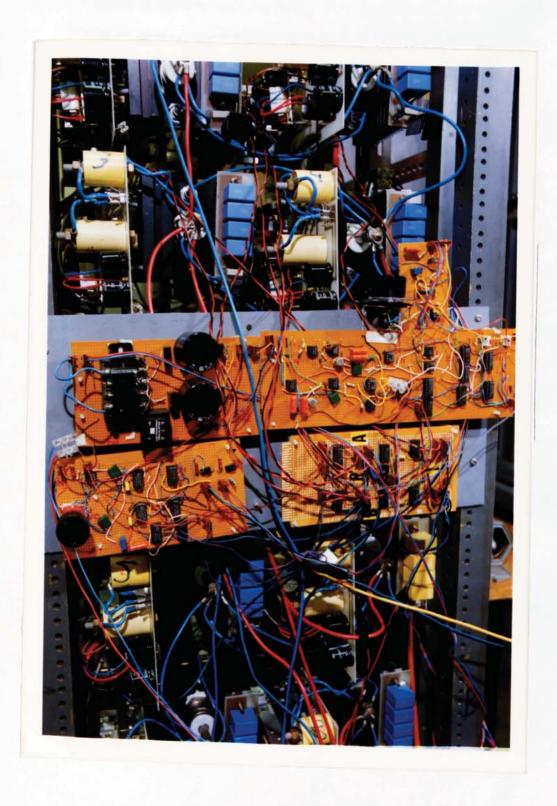

- d) The complete system was assembled in a single framework which was designed in the department and photographs of this are shown in Chapter 4.

- e) Before testing and reaching the final stage of the project, some problems were encountered, such as inrush current into the filter capacitor and transient voltages at the input to each converter. These problems, together with the experimental results are discussed in Chapter 5.

The advantages of this configuration are:]

- a) The rectifier power factor can be controlled.

- b) The power flow can easily be reversed; it has been found that the GTO can easily be transferred from a controlled device to a diode (always on).

The main disadvantage of this configuration is the switching losses of the devices. As shown in figure (1-7) there is a diode in series with each GTO, due to the fact that this type of GTO has a very low reverse voltage blocking capability and the need for series diodes stemmed from the non-availability of symmetrical GTOs.

The system can be operated in four-quadrants and can be used for a variable speed drive or to link two systems with different frequencies.

Finally, there is further work to be done on this research topic and this is discussed in the conclusions in Chapter 6.

Figure (1-2) Single phase converter circuit

Figure (1-3) Induction motor regenerative braking.

Figure (1-4) Matrix converter.

Figure (1-5) PWM current source inverter.

Figure (1-6) PWM-rectifier-PWM-inverter drive of an AC machine.

Figure (1-7) AC-AC converters using GTOs.

#### CHAPTER TWO

#### THE GTO THYRISTOR

#### 2-1 INTRODUCTION.

Recent developments in power semiconductor devices have yielded new and efficient controllable switches like the gate turn off thyristor (GTO) which is able to handle a higher blocking voltage compared with a power transistor and has the additional advantage of gate turn-off capability, eliminating the need for commutation circuits which are used with conventional thyristors.

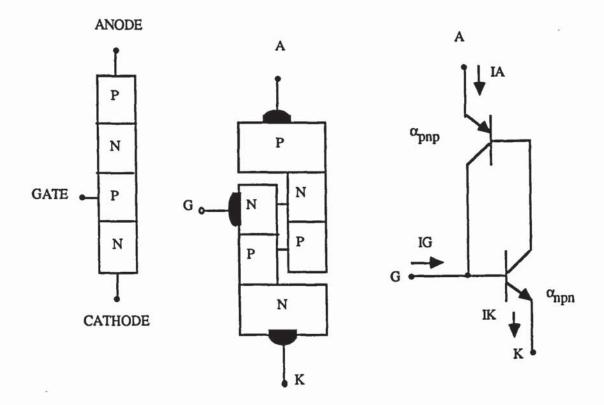

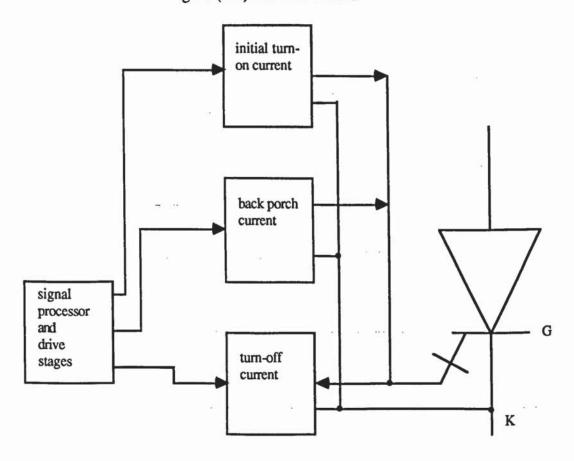

The construction of a GTO is similar to that of a conventional thyristor. It has a three terminal, four layer pnpn structure, which can be explained in terms of a two transistor model as shown in figure (2-1-a). This is a regenerative arrangement, in which the collector current of one transistor supplies the base drive for the other transistor (43,44). Once the thyristor is turned on, it cannot be turned-off. Thus the off-state cannot be restored by the gate signal.

The GTO thyristor can be turned-off by extracting sufficient current from the gate to cause the loop gain to fall to a point where the regenerative action ceases. This can be obtained by making  $\alpha(npn)$  relatively large and  $\alpha(pnp)$  small. The current amplification factor  $\alpha(pnp)$  of a GTO is lower than that of a conventional thyristor. Two methods are used to control  $\alpha(pnp)$ ; the diffusion of heavy metal as a life time killer and an anode-emitter short-circuit. These are shown in figure (2-1-b-c). In the heavy metal doping technique, the n1 region is doped with metal, such as gold, in order to reduce the lifetime of minority carriers (43,45,47).

The anode emitter shorting technique results in a device with a very low reverse voltage blocking capability. As can be seen in figure (2-1-c), the only junction capable of blocking reverse voltage is junction J3, since J1 has been shorted out. A

GTO with heavy-metal doping for minority carrier lifetime control has an on-state forward voltage drop of 10-15% greater than that obtained with a GTO using anode emitter shorting. However, its reverse voltage blocking capability is much greater since junction J1 is available to block reverse voltage as shown in figure (2-1-b) (45).

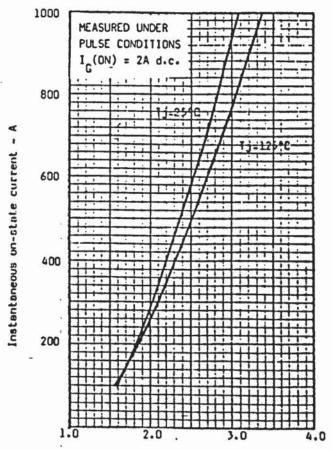

The Marconi GT224K GTO, was chosen for the research for the following reasons. Firstly a full data sheet for the device was provided by MEDEL and secondly, the device was offered to the department at a very reasonable cost. The data sheet of the GTO is given in appendix (A).

This chapter will improve the understanding of the switching behaviour of a GTO thyristor and the operation and design of both snubber and gate drive circuits. An inverter circuit as illustrated in section (2-6) of this chapter was used for this purpose.

Two Transistor model (a)

Figure (2-1) GTO Construction.

#### 2-2 TURN-ON CHARACTERISTICS.

A GTO thyristor is a latching device. Once the anode current reaches a certain latching value, the device will go into full conduction (50-53). The total turn-on time is the sum of the delay time  $(t_d)$  and the rise time  $(t_r)$  as defined in figure (2-2). Table (2-1) shows the terms and definitions for each symbol of the GTO switching waveforms. The turn-on time depends on the characteristics of the device as well as the rate of rise and the amplitude of the gate current.

To accomplish fast turn-on, a steep rise and a large value of gate current are required. The values depend on the size and the rating of the device and are usually specified by the manufacturer.

The power loss is comparatively low during the delay time because the anode current at this stage is still low. Maximum turn-on power losses are incurred during the rise time when the load is resistive with no di/dt limiting inductance in the circuit (50-55).

#### 2-3 TURN-OFF CHARACTERISTICS.

The on-state anode current can be turned-off by applying a negative gate bias to the gate-cathode junction of the GTO (50,53). The turn-off time is defined as the sum of the storage time ( $t_{gs}$ ), the fall time ( $t_{gf}$ ) and the tail time (45,53,56) as defined in figure (2-2).

The initiation of a negative gate voltage causes negative gate current to start to flow. The rate of rise of this current is controlled by the value of the turn-off voltage and the gate circuit inductance (51,57).

During the storage period, anode current (I<sub>A</sub>) and device voltage (V<sub>AK</sub>) remain constant. The switching power losses in this period are comparatively small. The duration of the storage time depends on how rapidly the excess charge (Q<sub>GQ</sub>) is removed from the P-base of the GTO. The termination of the storage time usually occurs when the gate current reaches a maximum value (53,57).

When the excess charge is removed, the centre junction of the GTO comes out of saturation. The anode current starts to fall rapidly and the anode voltage rises to  $V_{DP}$ . The anode voltage continues to rise at a linear rate until it reaches  $V_{DM}$ . There is further explanation about  $V_{DP}$  and  $V_{DM}$  in section (2-4).

After the fall time the anode current goes to a low value I<sub>TAIL</sub>, which decays more slowly, the duration of this time depends upon the characteristics of the device (53,48). The tail time is an important factor for switching power losses since the anode voltage is high at this time.

Illustration removed for copyright restrictions

Figure (2-2) GTO general switching waveforms.

(waveforms taken from MEDL data)

| Symbol           | Term                                       | Definitions                                                                                                                                      |

|------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| dV/dt            | Critical rate of rise of off-state voltage | The minimun value of rate of rise of off-state voltage to cause switching from off-state to on-state.                                            |

| I <sub>PG</sub>  | Forward gate current                       | The peak value of forward gate current at turn -on.                                                                                              |

| $I_{Gon}$        | On-state gate current                      | The value of the gate current during on-state conduction.                                                                                        |

| I <sub>Tav</sub> | On-state current                           | The maximum value of mean on-state current.                                                                                                      |

| QQQ              | Turn-off gate charge                       | The charge supplied to the gate during reverse bias that causes the on-state current to fall to 90% of its initial value.                        |

| t <sub>d</sub>   | Delay time                                 | The time interval between the gate current reaching 10% of its final value and the off state voltage falling to 90% of its initial value         |

| tgf              | Fall time                                  | The time interval for the on-state current to fall from 90% of its initial value and the beginning of tail time.                                 |

| t <sub>gq</sub>  | Gate controlled<br>turn-off time           | The time interval between the reverse gate current reaching 10% of its final value and the beginning of tail time.                               |

| tgs              | Storage time                               | The time interval between the reverse gate current reaching 10% of its final value and the on-state current falling to 90% of its initial value. |

| t <sub>r</sub>   | Rise time                                  | The time interval for the on-state voltage to fall from 90% to 10% of its initial value                                                          |

| $V_D$            | Continuous (direct) off-state voltage.     | The maximum value of applied direct off state voltage                                                                                            |

| V <sub>DM</sub>  | Turn-off voltage                           | The peak value of direct off-state voltage at turn-off.                                                                                          |

| $V_{DP}$         | Peak forward<br>transient voltage.         | The peak value of forward transient voltage appearing across the anode and cathode of the GTO during the fall time.                              |

| V <sub>RG</sub>  | Reverse gate voltage                       | The value of negative gate-cathode voltage.                                                                                                      |

| $I_{CQ}$         | Reverse gate current                       | The value of reverse current at switch off                                                                                                       |

Table (2-1) GTO terms, symbols and definitions.

#### 2-4 SNUBBER CIRCUIT.

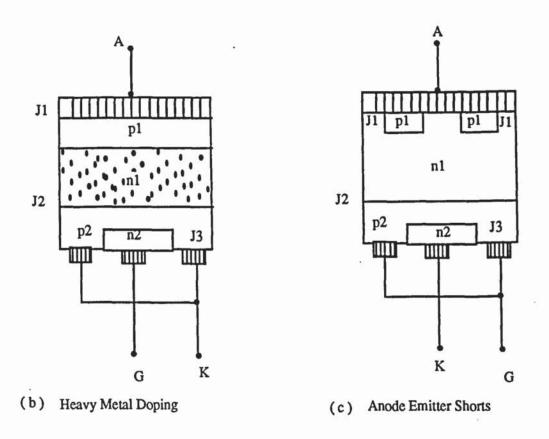

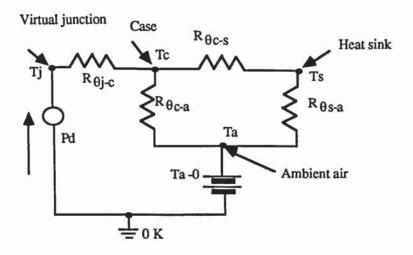

It is necessary to connect a snubber circuit across a GTO to limit the rate of rise of voltage during GTO turn-off and to limit the peak power dissipated by providing an alternative path for the anode current when the GTO turns-off (51,59.61). Figure (2-3) shows the connection of a snubber circuit across a GTO chopper circuit. The snubber circuit consists of a capacitor, a resistor and a diode.

After the expiry of the storage time, the GTO anode current collapses with a fall time which produces a very high rate of rise of current in the snubber circuit. The transient responses of the snubber network produce a voltage spike V<sub>DP</sub> which appears at the anode of the GTO. This voltage depends on the inductance of the snubber capacitor, the inductance of the circuit wiring and the transient turn-on impedance of the snubber diode (61,62). The value of V<sub>DP</sub> must be kept below the rated value of the GTO to avoid excessive turn-off power dissipation.

The capacitor voltage rises at a linear rate given by:

$$\frac{\mathrm{dV}_{\mathrm{C}}}{\mathrm{dt}} = \frac{\mathrm{I}_{\mathrm{A}}}{\mathrm{C}_{\mathrm{S}}} \tag{2-1}$$

Where IA is the anode current.

The capacitor voltage continues to rise until it reaches the DC supply voltage, at which instant, point (A) shown in figure (2-3) becomes effectively clamped to the DC supply. The capacitor voltage then overshoots and reaches V<sub>DM</sub>. The overshoot amount will be governed by the value of the snubber capacitor and the stray inductance.

The peak overshoot may be determined by simply considering the energy transfer in the circuit as follows. The total energy change in the system equals the energy stored in the inductance L plus the energy absorbed by the capacitor from the supply, where L is the total leakage inductance  $(L_{X1} + L_{X2})$  of the circuit.

Therefore:

$$\frac{1}{2}C_{S}(V_{DM}^{2} - V_{DC}^{2}) = \frac{1}{2}LI_{A}^{2} + V_{DC}\int idt$$

(2-2)

Where:

V<sub>DM</sub> is the peak capacitor voltage reached.

V<sub>DC</sub> is the supply voltage.

$$i = C_S \frac{dV_C}{dt}$$

Therefore.

$$\frac{1}{2}C_{S}(V_{DM}^{2} - V_{DC}^{2}) = \frac{1}{2}LI_{A}^{2} + V_{DC}\int_{D_{DC}}^{V_{DM}} C_{S} dV_{C}$$

(2-3)

$$\frac{1}{2}C_{S}(V_{DM}^{2} - V_{DC}^{2}) = \frac{1}{2}LI_{A}^{2} + C_{S}V_{DC}(V_{DM} - V_{DC})$$

(2-4)

Which gives:

$$V_{DM} = V_{DC} + I_A \sqrt{\frac{L}{C_S}}$$

(2-5)

After the voltage overshoots, the capacitor discharges through R<sub>S</sub> and D<sub>F</sub>, eventually settling to the DC supply voltage. The current in the snubber circuit approaches zero and a reverse current flows through the snubber diode maintained by the stored charge. D<sub>S</sub> cannot regain its reverse blocking capability until most of the stored charge is removed by the reverse extraction process and internal recombination of the charge carriers. This snap off of reverse current will produce via external circuit inductance, a negative voltage spike which then recovers rapidly to the steady-state positive voltage level (45,48,49,64). Since the magnitude of this voltage excursion depends on the diode turn-off speed, the snapiness can be reduced to a certain degree by using a soft recovery diode.

The greater part of the energy stored in  $C_S$  during turn off is dissipated in  $R_S$ . The required power rating of  $R_S$  is given by:

$$W_{S} = \frac{1}{2} C_{S} V_{C}^{2} f$$

(2-6)

Where f is the switching frequency and V<sub>C</sub> is the snubber capacitor voltage.

(Note that, in the above equation,  $V_{DM}$  is used to calculate the rating of the snubber resistor. Although the time during which  $V_C$  equals  $V_{DM}$  is only a fraction of a cycle, by basing on  $V_{DM}$  rather than  $V_{DC}$ , this gives a safety margin for the resistor rating).

The ohmic value of  $R_S$  is chosen to enable  $C_S$  to discharge almost completely during the shortest period for which the GTO is conducting. Otherwise any residual charge left on  $C_S$  will add to the voltage spike  $V_{DP}$  at turn-off. The discharge time is governed by the time constant  $R_SC_S$ . It is well known that for a RC circuit, the capacitor needs at minimum 5 times the time constant to be almost discharged. MEDL data sheet recommended that (57):

$$C_S R_S < t_{OD}/5.$$

(2-7)

Where ton is the conduction time of the GTO. On the other hand, the value of the snubber resistor R<sub>S</sub> must be high enough to limit to a safe value the capacitor discharging current which flows through the GTO at turn on (45).

#### 2-5 GTO GATE DRIVE CIRCUIT.

The gate drive circuit has a direct influence on the switching performance of a GTO thyristor. As was mentioned in section (2-3) the storage time is affected by the rate of rise of gate current and the peak gate current. In designing a gate drive circuit, care must be taken to ensure that the rate of rise of gate current meets the manufacturer's specification, and this can be controlled by varying the value of the gate inductance and the turn-off voltage (53,54).

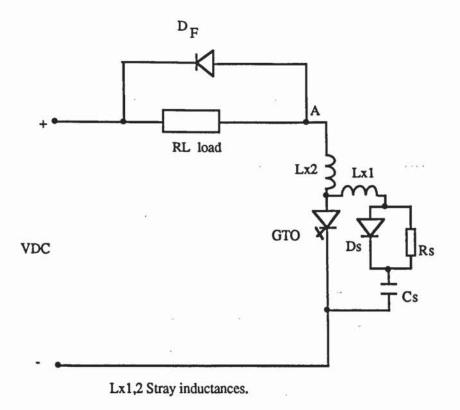

The GTO drive circuit represented by the block diagram of figure (2-4) is comprised the following blocks.

a) The input signal which handles the incoming control signal and the driver stages.

- b) The initial turn-on current which contains a circuit to handle the peak value of forward current (I<sub>FG</sub>) at turn-on.

- c) The third one contains a circuit to carry the back porch current which is the value of the gate current during on-state conduction.

- d) Finally the turn-off circuit and this carries the turn-off current ( $I_{GQ}$ ) ( this is the value of reverse gate current at turn-off).

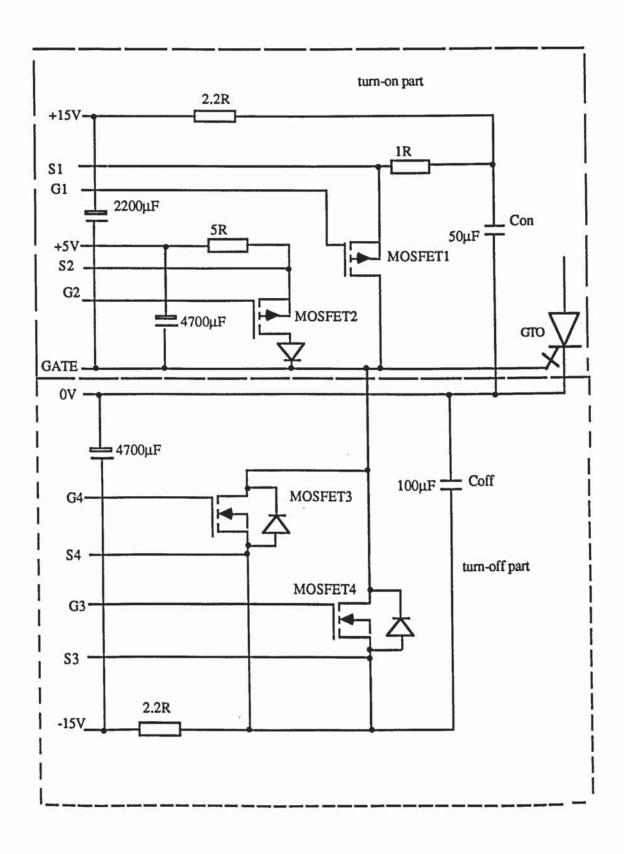

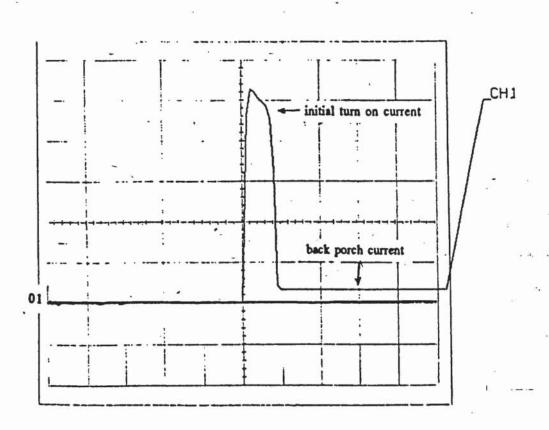

Figure (2-5) shows the circuit details for the turn-on and turn-off parts and figure (2-6) shows the waveform of the initial turn-on and the back porch current. The initial turn-on current consists of a high current pulse (About 15 A magnitude for  $12\mu s$ ) which can be obtained by discharging the capacitor  $C_{On}$  through  $1 \Omega$  resistor and power MOSFET1. The back porch current (about 1A) is obtained by switching the 5V supply to the gate through the  $5 \Omega$  resistor and power MOSFET2. To avoid any gap between the initial and the back porch current, MOSFET1 and MOSFET2 must turn-on simultaneously. According to the data sheet of the device, the initial pulse should have an amplitude of at least 10 A whilst the back porch current should be 1 A at  $25 \, {}^{\circ}\text{C}$ .

Turn-off is achieved by discharging capacitor Coff through the GTO gate and the two power MOSFETs3,4 in parallel to handle the reverse current of the GTO at turn-off. Note that MOSFETs1,2 are P channel enhancement and MOSFETs3,4 are N channel enhancement types. To turn-on the P channel the input voltage should be more negative than the threshold voltage(-2 V) and for N channel the input voltage should be more positive than the threshold voltage (3V).

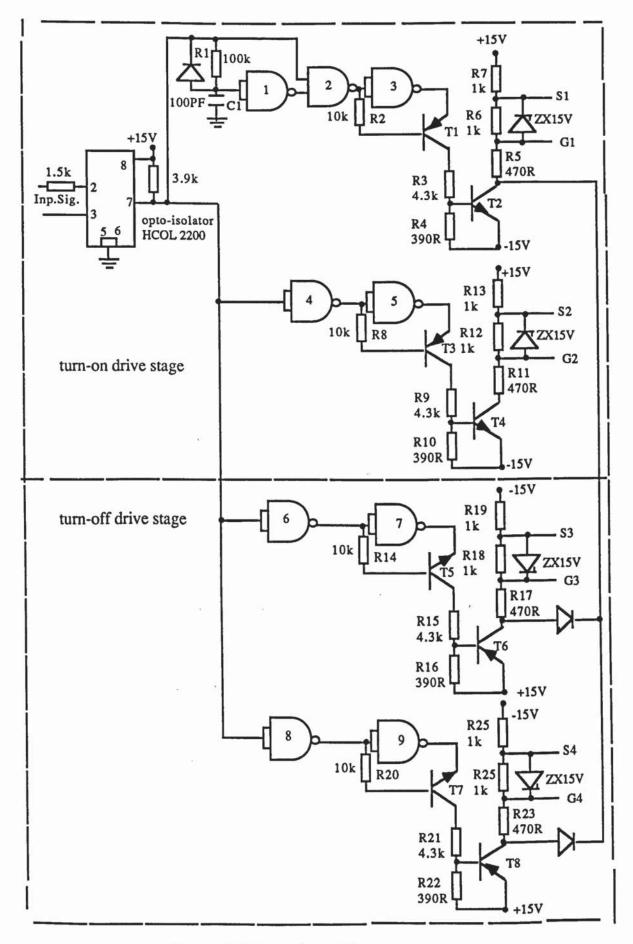

The gate circuits in turn are driven from turn-on and turn-off stages as shown in figure (2-7). To understand the operation of the drive stage circuit, the circuit has been divided into simple sections and each section is explained individually. As shown in figure (2-7) an opto-isolator is connected at the input of the drive stage, this is used to isolate each drive circuit from the input signal. The device is ideal for

isolating high speed logic interfaces, eliminating ground loops and implementing isolated line receivers in high noise environments.

The GTO thyristor is a latching device and a single narrow pulse or a pulse train to its gate is usually sufficient to turn it on. Due to the characteristics and application of the present gate drive circuit, wide-width pulses are used to drive the GTO. This means a continuous pulse supplies the gate throughout the whole conduction period of the GTO. When the input pulse of the gate circuit driving stages is high, the GTO will turn-on and when the input pulse is low, the GTO will turn-off.

Figure (2-3) Snubber circuit.

Figure (2-4) Gate drive block diagram.

Figure (2-5) GTO Drive circuit.

Figure (2-6) Initial turn on and back porch current.

CH2: 3 A/div.

Initial on current: 16 A.

Back porch current: 1 A.

Time: 15 µs/div.

Figure (2-7) Gate circuit drive stages.

#### 2-5-1 DELAY CIRCUIT.

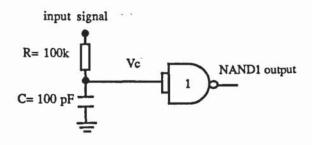

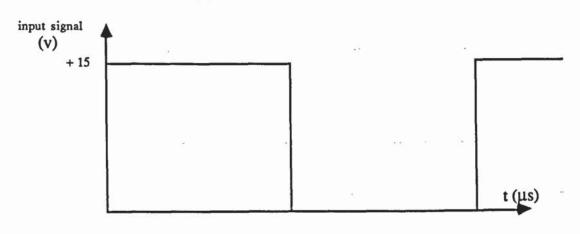

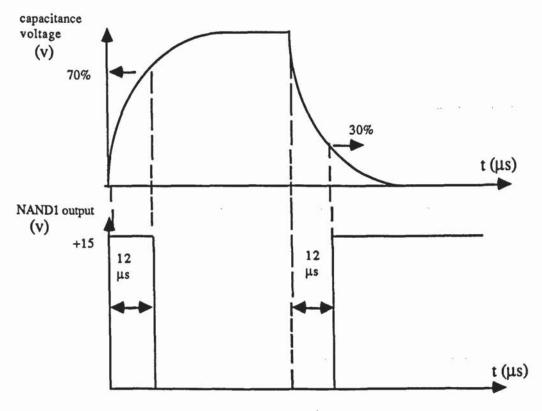

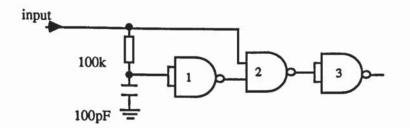

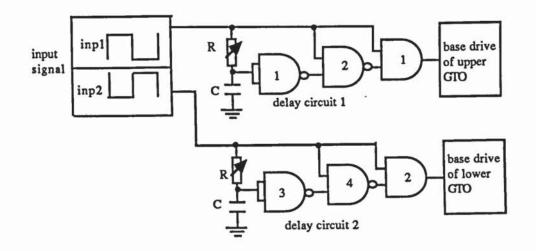

A 12 µs signal is used to feed the driving stage of MOSFET1 in order to carry the initial turn-on current pulse. This signal is generated by a delay circuit comprising three NAND gates and an RC circuit as shown in figure (2-9). This kind of NAND gate (CMOS 4093 2-input NAND Schmitt trigger) switches at different voltage levels for positive and negative going edges. For a positive-going edge, the gate switches when the input voltage reaches 70% of its peak value and for a negative-going edge, the gate switches when the input voltage drops to 30% of its peak value. The peak value of the input voltage is 15 V, therefore the output of the NAND gate changes state when its input reaches 10.5 V or when its input drops to 4.5 V.

To get a 12  $\mu$ s wide signal, the input of the delay circuit must rise exponentially and reaches 70% of its peak voltage in 12  $\mu$ s. By feeding the input signal to an RC circuit, the capacitor voltage will reach 70% of the peak input when t = 1.2RC as illustrated in equation (2-8)

$$V_C = V_{inp} (1 - e^{\frac{3}{RC}})$$

(2-8)

Figure (2-8) shows the connections of the input signals to the RC circuit and the effect of NAND1.  $R = 100 \text{ k} \Omega$ , C = 100 pF,  $1.2RC = 12 \mu\text{s}$

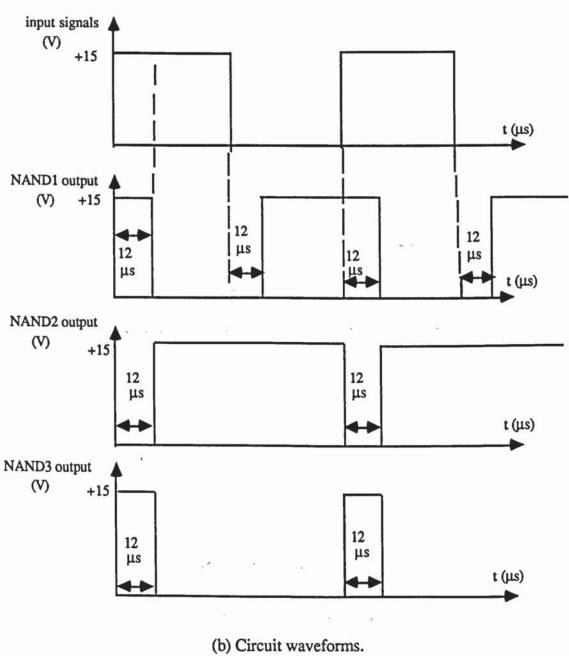

Refer again to figure (2-9), the output of NAND1 supplies one input of the NAND2 and the input signal supplies the other input. The output of NAND2 is inverted using NAND3, which gives a 12 µs pulse at the beginning of the input signal. Figure (2-10) shows the oscillograms of the input signal and the output of the delay circuit (output of NAND3).

(a) Circuit connections.

(b) Circuit waveforms.

Figure (2-8) RC circuit connections and waveforms.

(a) Circuit connections.

Figure (2-9) Delay circuit connections and waveforms.

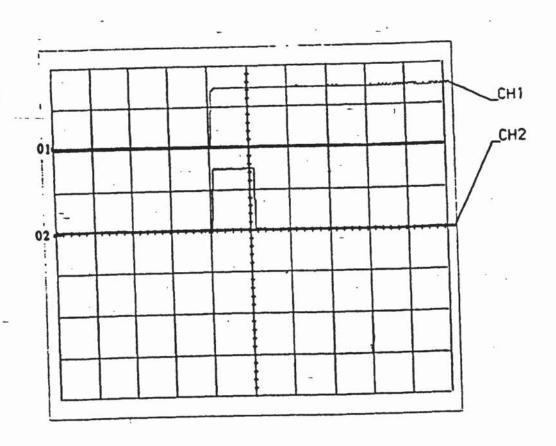

Figure (2-10) Output of the delay circuit.

. CH1: 15 V/div. (input signal).

CH2: 15 V/div. (delay circuit output).

Time:  $10 \mu s/div$ .

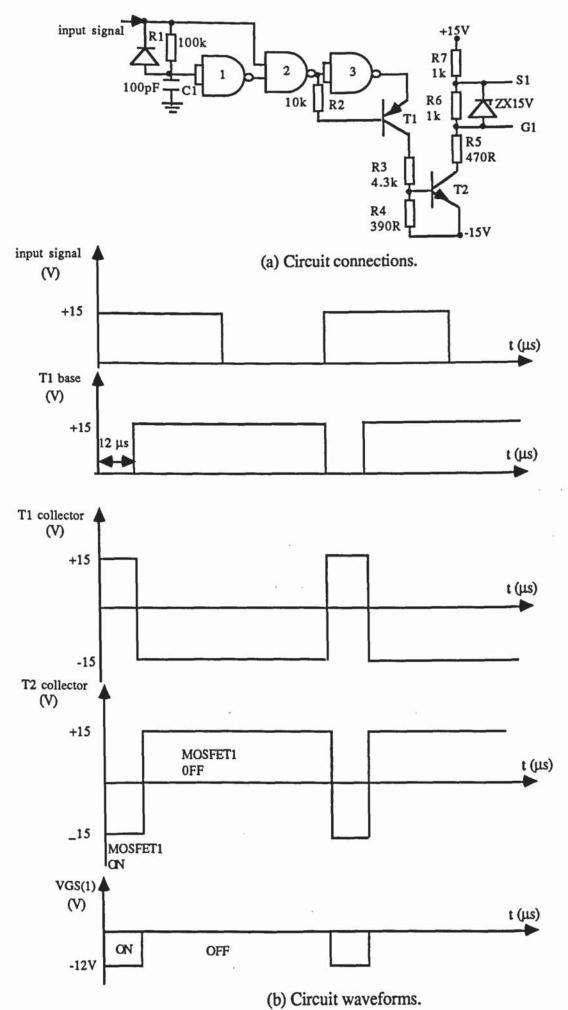

# 2-5-2 MOSFET1 DRIVE STAGE.

Figure (2-11) shows the MOSFET1 drive stage. Each time the input signal changes from low to high state, the output of NAND2 will be zero for a 12 µs duration. The output of NAND2 feeds the base of transistor T1 to switch it on. The emitter of T1 is connected to the output of NAND3 which inverts the state of NAND2 output. When T1 turns-on, current flows through its emitter, collector and the resistors (R3 and R4). These resistors operate as a voltage divider to feed the base of T2. When transistor T2 turns-on, a current flows from the +15 V rail through R7, R6, R5, and T2 to the -15 V rail. This current produces a voltage at the gate of MOSFET1, with a magnitude of:

$$V_{G1S1} = \frac{30}{R_7 + R_6 + R_5} R_6 = \frac{30}{1 + 1 + 0.47} = 12.1 \text{ V}$$

This voltage is negative with respect to the source and less than the threshold voltage thus MOSFET1 will turn-on to carry the initial pulse current.

After the 12  $\mu$ S duration, the output of NAND2 changes state to a high level (+15 V), T1 turns-off and the base of T2 is connected to -15 V rail. Hence T2 turns-off and the current through R6 cuts-off. The gate-source voltage is zero which is higher than the threshold voltage and this turns MOSFET1 off. Figure (2-12) shows the oscillograms of the drive stage.

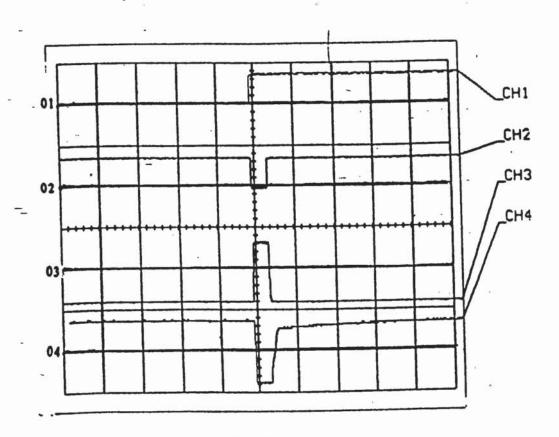

# 2-5-3 MOSFET2 DRIVE STAGE.

Figure (2-13) shows the MOSFET2 drive stage. The input signal is inverted by NAND4 to feed the base of transistor T3 via R8, whilst the emitter of T3 is connected to the output of NAND5 which has the same state as the input signal. When the input signal is high, the base of T3 is low, A current flows through its emitter, collector and the resistors (R9,R10), this current supplies the base of transistor T4 to turn it on. When T4 turns-on, a current flows from the +5 V rail through R13, R12, R11

and T4 to the -15 V rail. This current produces a gate voltage across R12 with a magnitude of:

$$V_{G2S2} = \frac{20}{R_{11} + R_{12} + R_{13}} R_{12} = \frac{20}{1 + 1 + 0.47} = 8 \text{ V}$$

This gate voltage is negative with respect to the source of MOSFET2 and less than the threshold voltage, hence MOSFET2 turns-on to carry the back porch current of the GTO gate drive circuit. When the input signal is low, T3 turns-off. Transistor T4 also turns-off. Since there is no current flow from the +5 V rail, the voltage across R12 is zero and MOSFET2 switches off. Figure (2-15) shows the oscillograms of the drive stage.

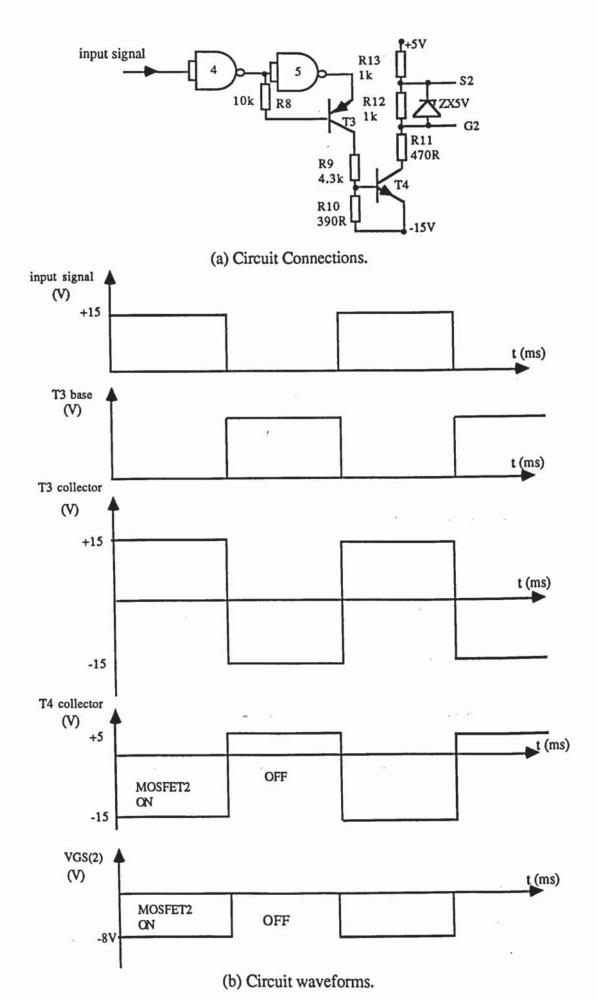

#### 2-5-4 MOSFET3 DRIVE STAGES.

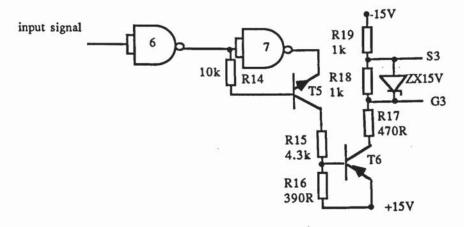

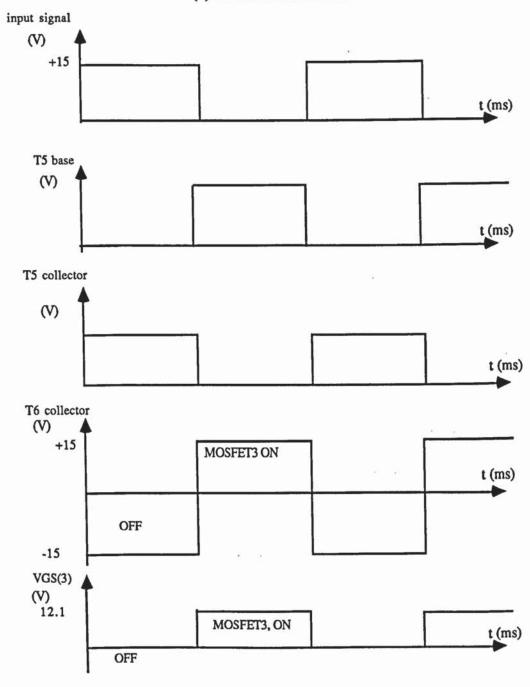

Figure (2-14) shows the MOSFET3 drive stage. The input signal is inverted by NAND6 to feed the npn transistor T5. When the input signal is low the base drive of T5 is high and this turns it on. The emitter of T5 is connected to the output of NAND7 which is low. A current flows from the +15 V rail through R16, R17 and T5. By the operation of the voltage divider (R15 and R16) the base voltage level of T6 is negative with respect to the emitter. T6 will turn on and a current flows from the +15 V rail through T6, R17, R19, and R20 to the -15 V rail. This current produces a gate voltage across R18 with a magnitude of:

$$V_{G3S3} = \frac{30}{R_{17} + R_{18} + R_{19}} R_{18} = \frac{30}{1 + 1 + 0.47} = 12.1 \text{ V}$$

This gate voltage is positive with respect to the source of MOSFET3 and higher than the threshold voltage, thus MOSFET3 turns-on. When the input signal is high (+15 V), T5 turns-off which in turn switches transistor T6 off. Since there is no current flow through T6, the voltage across R18 is zero and MOSFET3 turns-off. Figure (2-16) shows the oscillograms of the drive stage. (Note that the operation of MOSFET4 driving stage is similar to that of MOSFET3).

Figure (2-11) MOSFET1 drive stage.

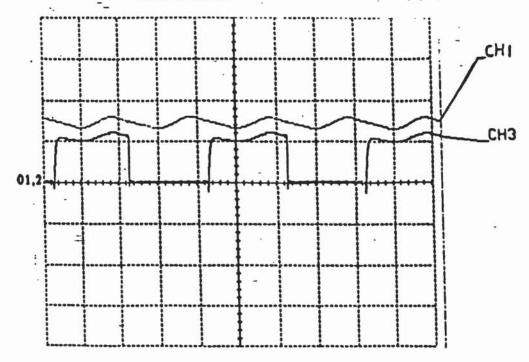

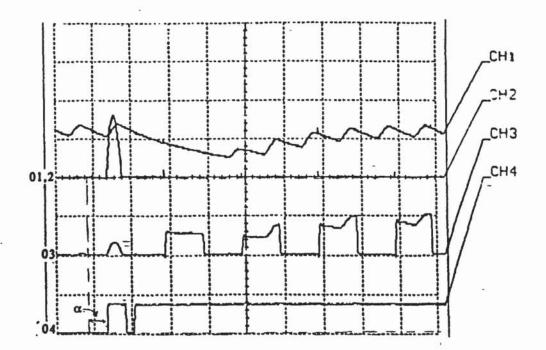

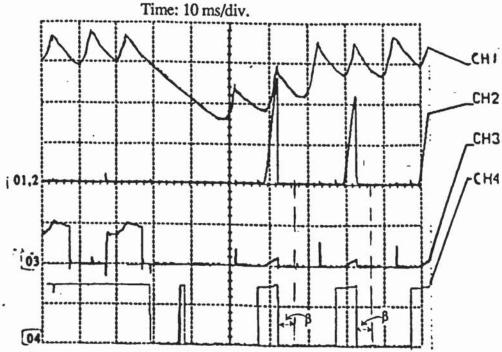

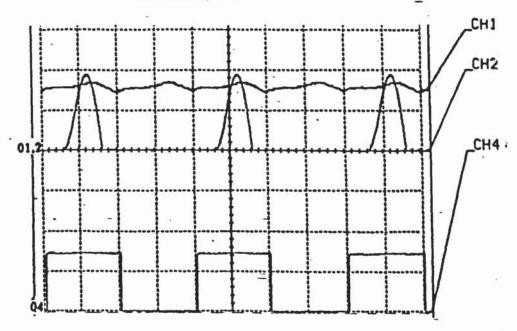

Figure (2-12) Output of MOSFET1 drive stage.

CH1: Input signal 20 V/div.

CH2: T1 base 20 V/div.

CH3: T1 collector 20 V/div. CH4: T2 collector 20 V/div.

Time: 25  $\mu$ s/div.

Figure (2-13) MOSFET2 drive stage.

(a) Circuit connections.

(b) Circuit waveforms.

Figure (2-14) MOSFET3 drive stage.

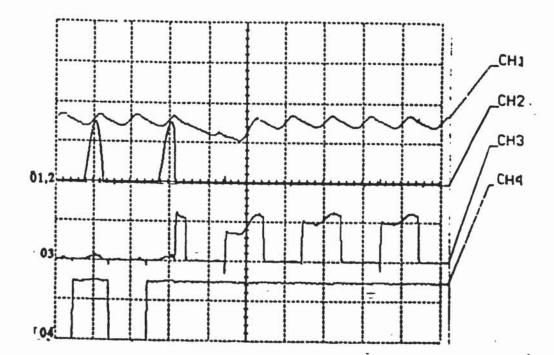

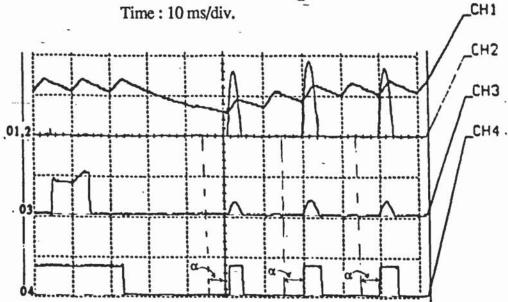

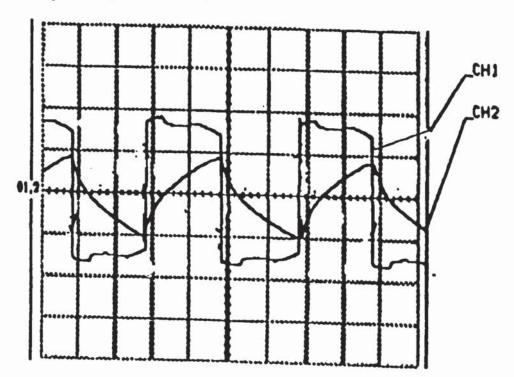

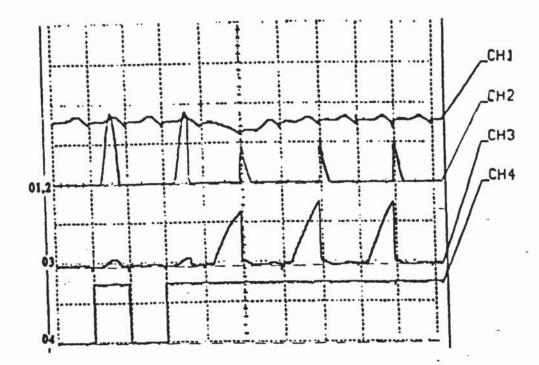

Figure (2-15) Outputs of MOSFET2 drive stage.

CH1: Input signal 20 V/div.

CH2: T3 base 20 V/div.

CH3: T3 collector 20 V/div.

CH4: T4 collector 20 V/div.

Time: 5ms/div.

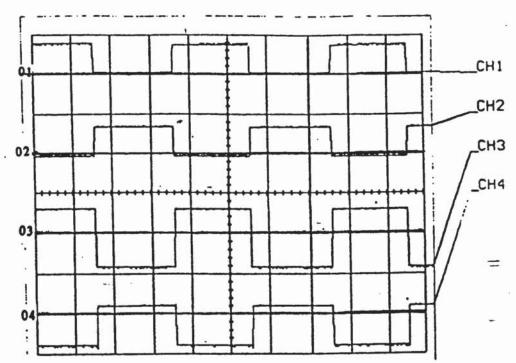

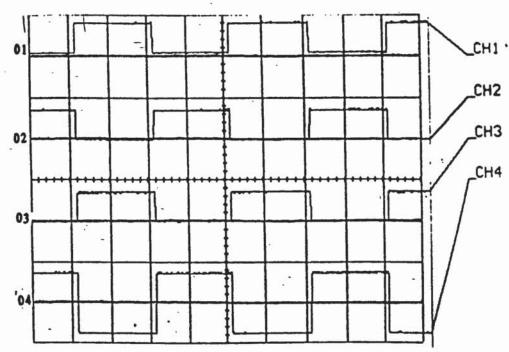

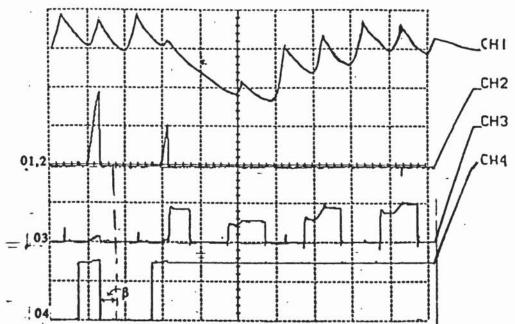

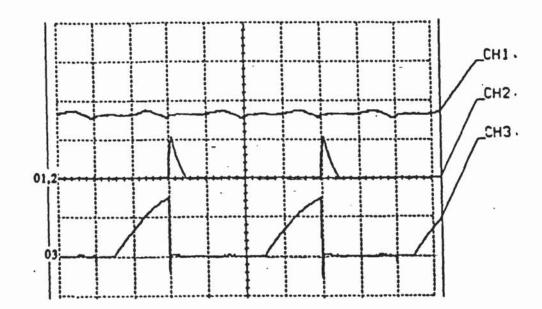

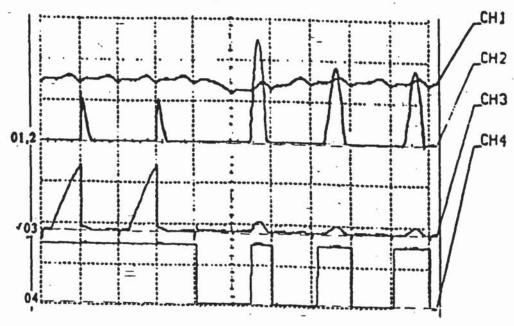

Figure (2-16) Outputs of MOSFET3 drive stage.

CH1: Input signal 20 V/div.

CH2: T5 base 20 V/div.

CH3: T5 collector 20 V/div.

CH4: T6 collector 20 V/div

Time: 5 ms/div.

## 2-6 GTO TESTING CIRCUIT.

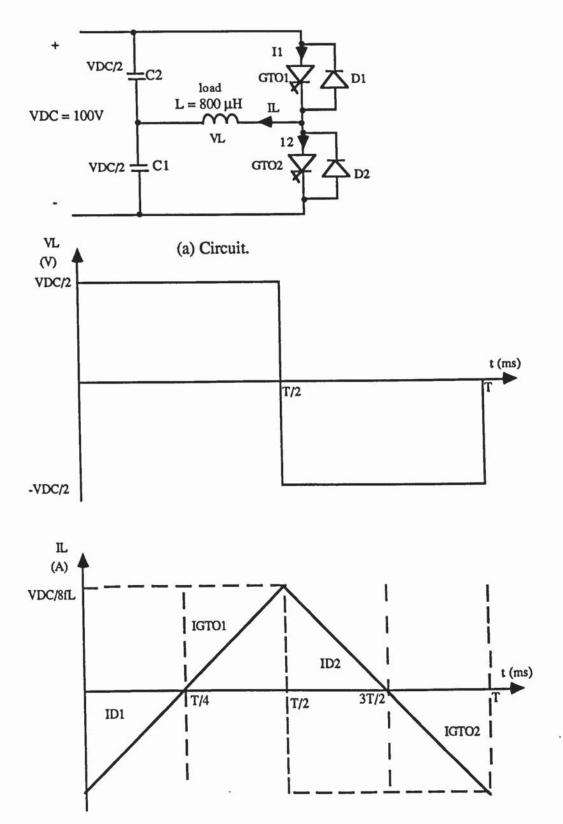

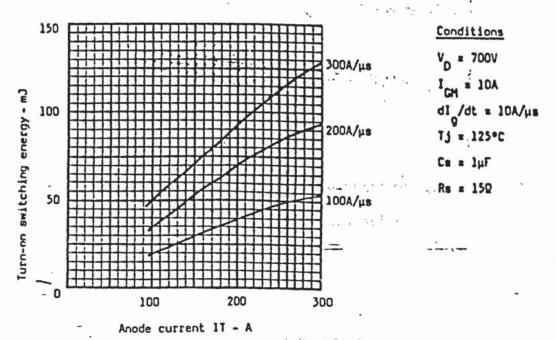

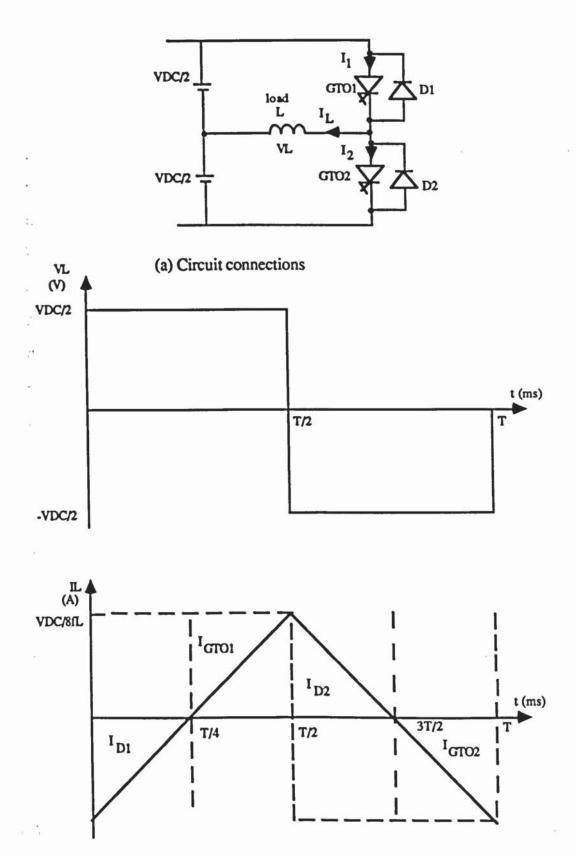

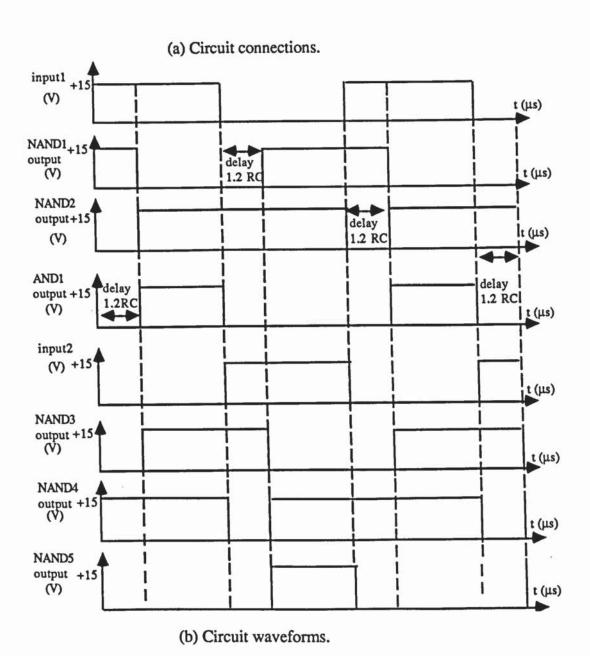

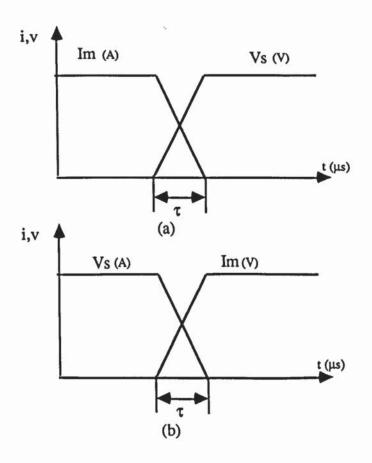

The switching waveforms and the operation of the gate drive circuit of the GT224K GTO were tested using the single phase half-bridge inverter of figure (2-17). For the initial test it was decided to operate the GTO at 10 A RMS as a safety margin and a switching frequency of 1kHz was chosen since this was the chosen frequency for the PWM waveform. The voltage of the DC power supply was 100 V. To obtain the required current of 10 A RMS at the stated voltage and switching frequency, the load was arranged to have an inductance of 800 µH and virtually negligible resistance to minimize the losses.

Referring to figure (2-17), since the inverter is a half bridge, when one GTO is turned-on for a time T/2 (T = 1/f), the instantaneous voltage across the load is VDC/2. Assume that, for the first half cycle GTO1 is turned on to carry the load current. When GTO1 turns-off and GTO2 turns-on, the load voltage reverses and the load current transfers to the diode D2, the voltage drop across D2 reverses the biases of GTO2. The current through D2 starts to fall and when it reaches zero, GTO2 becomes a forward biased and the load current flows through GTO2. Again when GTO2 turns-off and GTO1 turns-on, the load current transfers first to the diode D1 and when it reaches zero, it transfers to GTO1.

Under-steady state condition the maximum load current passing through the GTO at the end of first half cycle equals:

$$I_{PK} = \frac{V_{DC}}{8fL}$$

(2-9)

Where f is the inverter frequency and L is the load inductance. The derivation of the above formula is given in appendix (B).

With f = 1kHz,  $L = 800 \mu H$  and  $V_{DC} = 100 V$ , the peak current equals:

$$I_{PK} = \frac{100}{(8)(1000)(0.0008)} \approx 16 \text{ A}$$

Figure (2-18) shows that GTO<sub>1</sub> starts to conduct when the current through D<sub>1</sub> reaches zero. Since the load is purely inductive, the conduction period of the GTO is almost equal to that of the diode.  $I_{PK}$ = 16 A, and the RMS current is:

$$I_{RMS} = \frac{I_{PK}}{\sqrt{3}} = \frac{16}{\sqrt{3}} = 9.23 \text{ A}$$

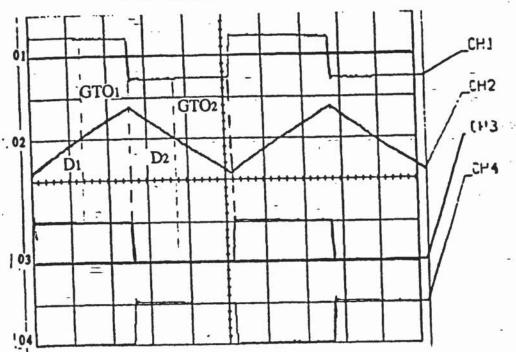

Figure (2-19) shows the load voltage, load current, the voltage across GTO1 and the voltage across GTO2. It is clear that the voltage across the load is  $V_{DC}/2$ .

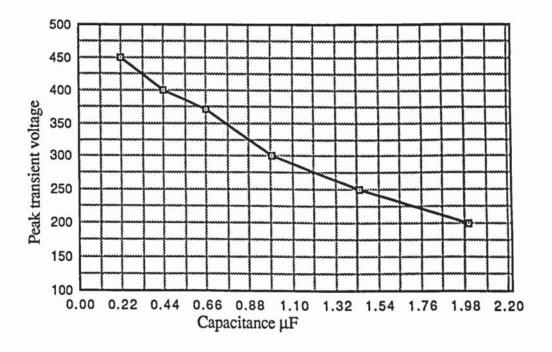

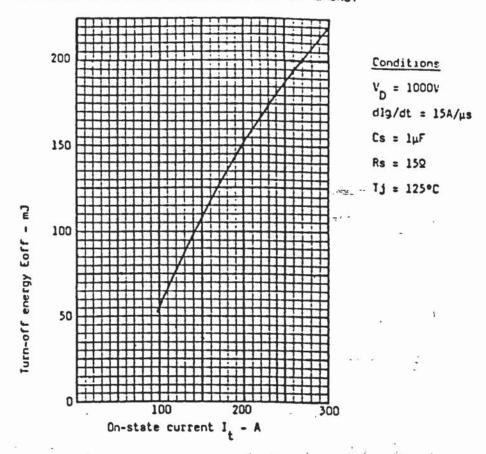

The value of the snubber capacitor was calculated assuming that, future research would be carried on with a 50 A peak anode current through each GTO. According to the device data sheet, the maximum permissible dV/dt is 500 V/ $\mu$ s and referring to the snubber section in this chapter, the value of  $C_S$  is:

$$C_S = \frac{I_A}{dV_C/dt} = 0.1 \,\mu\text{F}$$

(2-10)

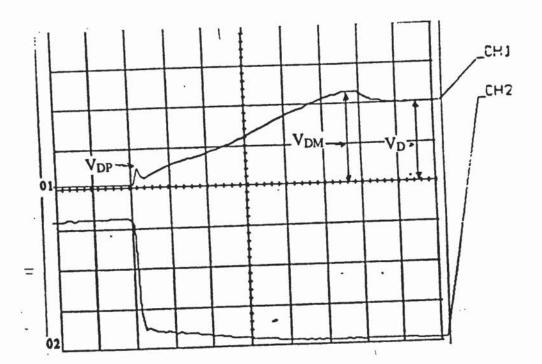

As mentioned above in this inverter peak anode current is much less than 50 A ( $I_{PK}$  = 16 A), when a 0.1  $\mu$ F snubber capacitor was used, it was found that the snubber circuit produces a high voltage spike and overshoot voltage ( $V_{DP}$  = 100 V,  $V_{DM}$  = 200 V,  $V_{overshoot}$  = 100 V). The voltage  $V_{DP}$  depends on the inductances of the snubber capacitor and the circuit wiring. The voltage  $V_{DM}$  also decreases when  $C_S$  increases.

$$V_{DM} = V_{DC} + I_A \sqrt{\frac{L}{C_S}}$$

(2-11)

Where:

$$V_{\text{overshoot}} = I_{\text{A}} \sqrt{\frac{L}{C_{\text{S}}}}$$

(2-12)

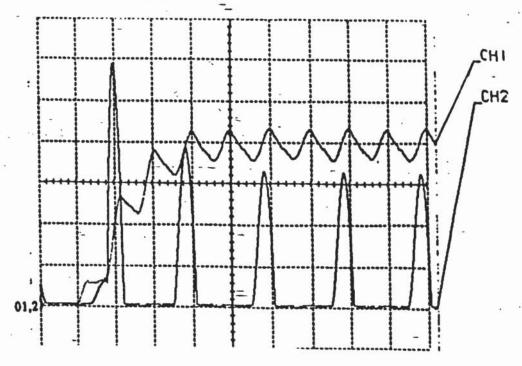

To reduce the values of the above voltages and to minimize the capacitor inductance, four capacitors were used in parallel for the snubber circuit (0.22  $\mu$ F each capacitor) and these gave waveforms shown in figure (2-20), where:

$$V_{DM} = 120 \text{ V}.$$

$$V_{DP} = 25 \text{ V}.$$

$$V_{\text{overshoot}} = 20 \text{ V}.$$

With  $I_A = 16$  A and  $C_S = 0.88 \,\mu\text{F}$ , the total stray inductance according equation (2-12) is:

$$L = \frac{V_{\text{overshoot}}^2 C_S}{I_A^2} = 1.375 \,\mu\text{H}$$

The ohmic value of R<sub>S</sub> must be:

$$R_{S} < \frac{t_{on}}{5C_{S}} \tag{2-13}$$

With 1 kHz switching frequency, the conduction time of the GTO is 250  $\mu$ s which gives a choice for the value of the snubber resistance of 57  $\Omega$  or less, the rating of the resistor must be:

$$W_{S} = \frac{1}{2} C_{S} V_{C}^{2} f$$

(2-14)

Where  $V_C$  is the snubber capacitance voltage.

With  $C_S = 0.88 \,\mu\text{F}$ ,  $V_C = 120 \,\text{V}$  and  $f = 1 \,\text{kHz}$ , the required rating is approximately 7 W.  $R_S$  should be large enough to limit the capacitor discharge current and since a 15  $\Omega$ , 7 W resistor was available, this was used for the snubber circuit. The maximum capacitor discharge current is quite low compared with the current rating of the GTO.

$$I_{C(Max)} = \frac{V_C}{R_S} = \frac{120}{15} = 8 \text{ A}$$

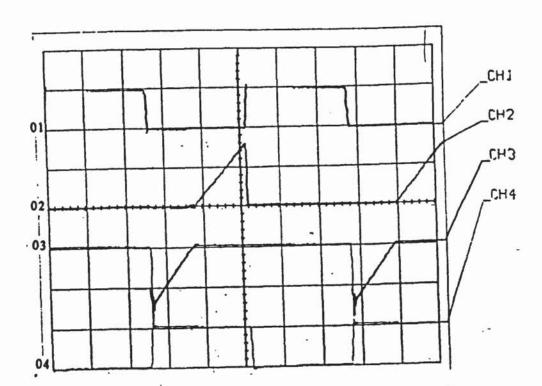

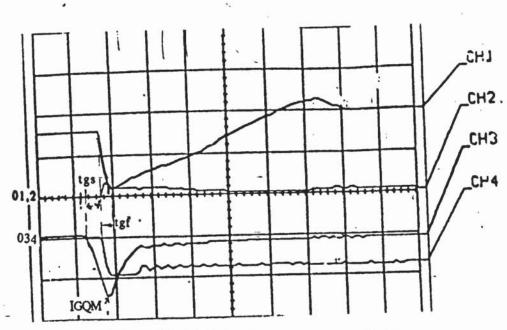

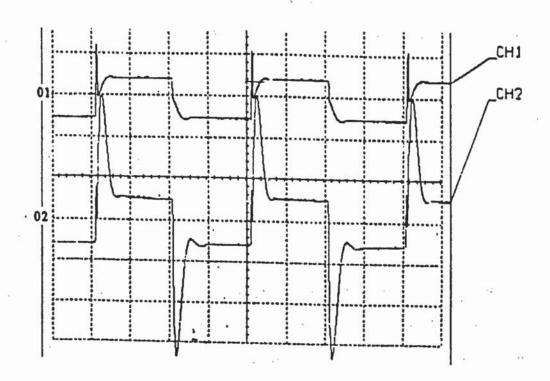

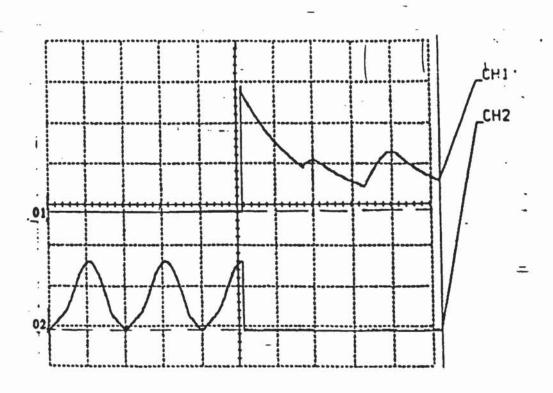

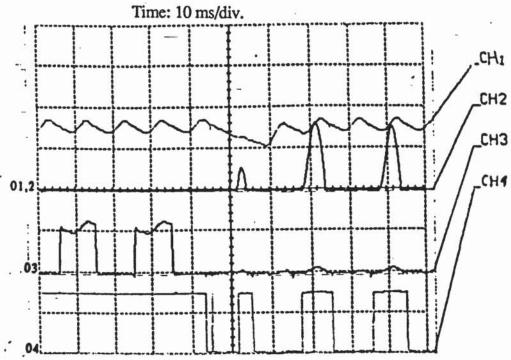

Figure (2-21) shows the GTO<sub>1</sub> switching waveforms. From Channel 3 it can be seen that  $I_{GOM} = 13$  A (it reaches this value after 0.75  $\mu$ s). Thus:

$$\frac{dI_{QQ}}{dt} = \frac{13}{0.75} = 17.33 \text{ A/}_{\mu s}$$

According to the device data sheet, the rate of rise of the reverse current must be between 12 and 30 A/ $\mu$ s.

In conclusion the above test shows that the switching characteristics and the operation of the gate drive of the GT224K meets the design and data sheet specification for the device.

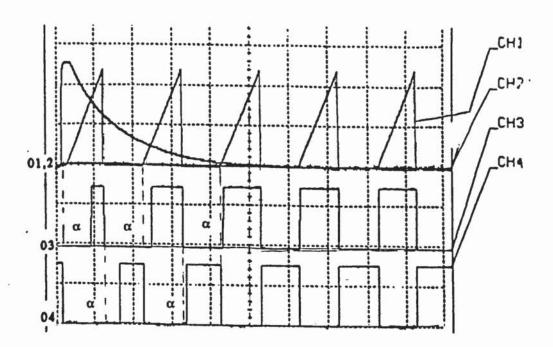

(b) Load voltage and current with an inductive load.

Figure (2-17) GTO Inverter.

Figure (2-18) Devices Voltages and Currents

CH1: V<sub>AK</sub> (GTO<sub>1</sub>) 100V/div. CH2: I<sub>A</sub> (GTO<sub>1</sub>) 10 A/div.

CH3: ID1 10 A/div.

CH4: VAK (GTO2) 100V/div.

Time: 5 ms/div.

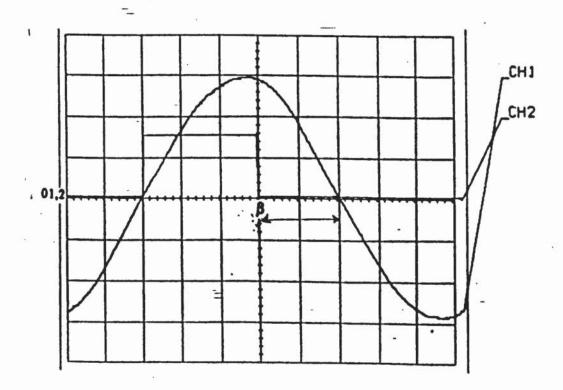

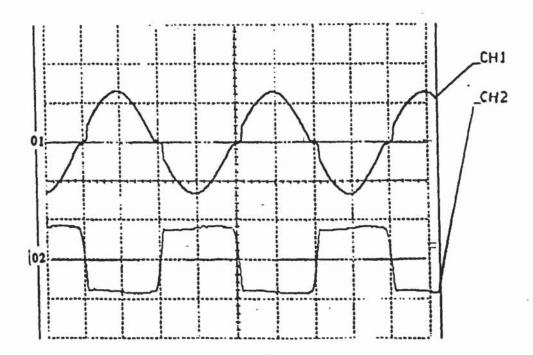

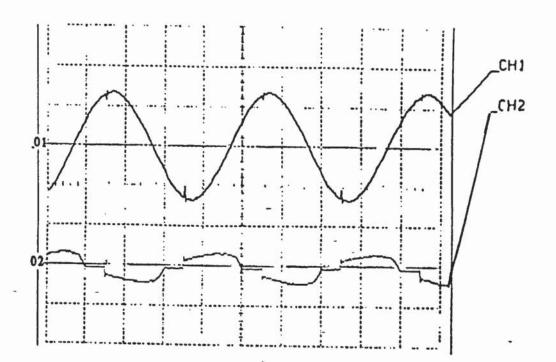

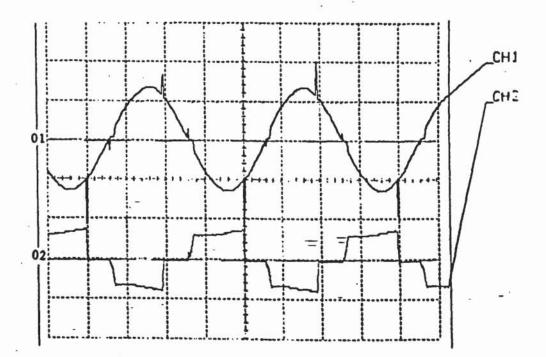

Figure (2-19) Load voltage and current.

CH1: Load voltage 100V/div.

CH2: Load current 20 A/div.

CH3: VAK (GTO2) 100V/div.

CH4: VAK (GTO1) 100V/div.

Time: 5 ms/div.

Figure (2-20) Voltage and Current when GTO1 is turning-off.

CH1: VAK 50V/div.

CH2: IA 5 A/div.

$V_{DP} = 25V$

$V_{DM} = 120V$

Time:  $2 \mu s/div$ .

Figure (2-21) Switching waveforms of GTO1.

CH1: VAK 50V/div.

CH2: IA 10A/div.

. CH3: I<sub>GQ</sub> 10 A/div.

CH4: VGK 20V/div.

Time: 2  $\mu$ s/div. Fall time = 0.5 $\mu$ s. Storage time = 1 $\mu$ s.

#### CHAPTER THREE

#### PRELIMINARY INVESTIGATION FOR TWO WAY POWER FLOW.

#### 3-1 INTRODUCTION.

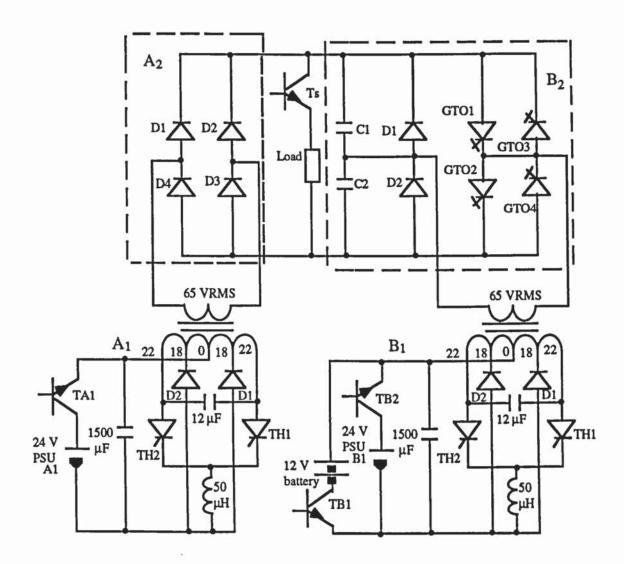

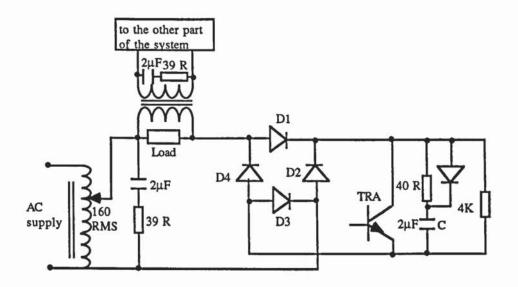

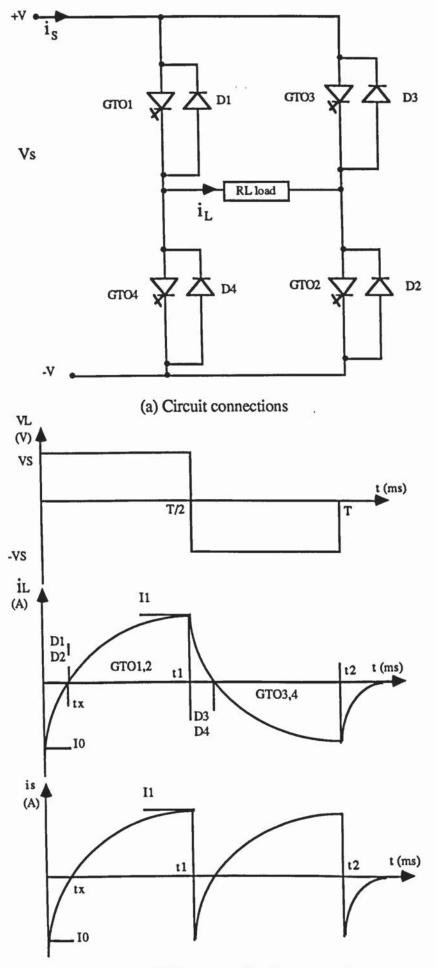

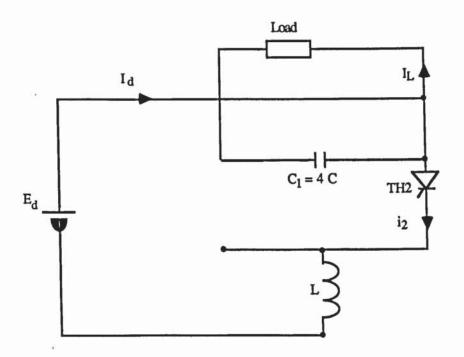

The circuit shown in figure (3-1) was chosen for a preliminary investigation into the problems associated with two directions power flow. The circuit contains two centre-tap inverters (A1 and B1), a diode bridge (A2) and a half-bridge GTO (B2). The use of a diode bridge and a half-bridge GTO respectively in converters (A2) and (B2) was necessitated by the lack of a sufficient quantity of gate drive circuits for the GTOs.

The configuration of figure (3-1) was decided on for preliminary investigation for the following reasons:

- a) The centre tap inverters readily lend themselves to the use of low battery voltages and low power loads.

- b) The power supplies were self contained and independent of the mains, thus ensuring additional safety and avoiding the need for synchronization with the mains.

This chapter presents the operation of the system, operation and testing of the centre tap inverters, system control circuit and finally a discussion of some results obtained from the system.

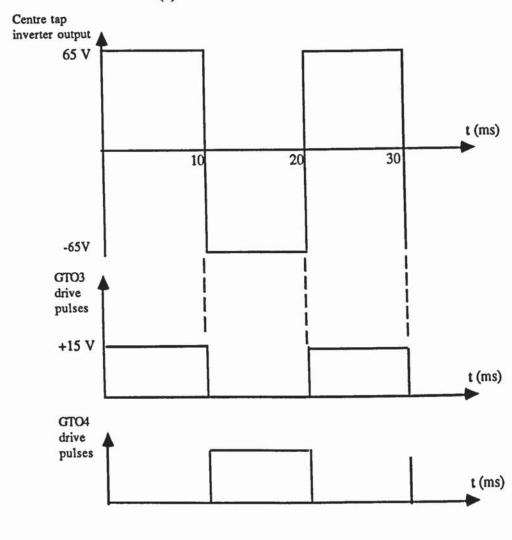

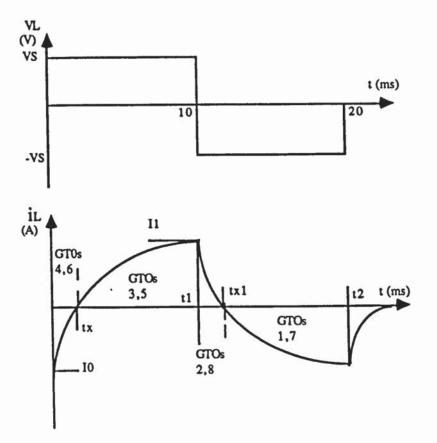

## 3-2 SYSTEM OPERATION.

When power flows from side (A) to (B) of the circuit shown in figure (3-1), (A1) acts as an inverter, with its output feeding the diode bridge (A2). The output of (A2) supplies (B2), which operates as an inverter to supply rectifier (B1) and the battery charges via diodes D1,2(B1).

When power flows from side (B) to (A), (B1) operates as an inverter, (B2) changes from an inverter to a rectifier and the power is dissipated in the load. When (B2) is operating as an inverter, GTO3 and GTO4 are continuously on and operate as diodes. The current flows through GTO1 and C1 during one half cycle and C2, GTO2 during the other. When (B2) operates as a rectifier, GTO1 and GTO2 are off and GTO3 and GTO4 turn-on as controlled devices. In this case, the rectifier will operate via GTO3 and D2 or GTO4 and D1.

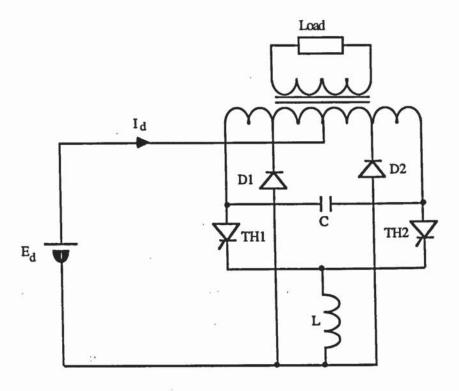

## 3-3 CENTRE TAP INVERTER.

There are two centre tap inverters connected to DC power supplies as shown in figure (3-1). These inverters are designed for 24 V and 5 A on the DC side and 65 V and 1.5 A RMS on the AC side. Conventional thyristors are used because the gate drive circuit for a thyristor is much cheaper and simpler than that of a GTO, while the single capacitor and inductor required for the commutation circuit of this 100 W parallel inverter are sufficiently small and cheap to justify their use in this application. When one thyristor is on, the DC source voltage appears across one half of the transformer primary, the total primary voltage is 2 VDC, and the capacitor is charged to 2 VDC. When the other thyristor is fired, the charged capacitor is then placed across the first thyristor turning it off.

Inverter (A1) is used to send power only while (B1) is used either to send or receive power. When (B1) is sending power, its input is connected to a 24 V power supply unit and when it is receiving power it is connected to a 12 V battery which will charge via the diodes. The reason for using the 24 V power supply unit for inverter (B1) is that the diodes are connected to an 18 V tapping as shown in figure (3-1) so the nominal voltage on the "high voltage" side would not be sufficient to produce the required charging voltage for a 24 V battery. Transistor switches are used to connect (B1) either to the 24 V power supply unit or to the 12 V battery depending on the direction of power flow.

Figure (3-1) Single phase arrangement for two way power flow.

(The drive and snubber circuits of the devices have been omitted from the figure so as not to confuse the explanation)

#### 3-3-1 THYRISTOR FIRING CIRCUIT.

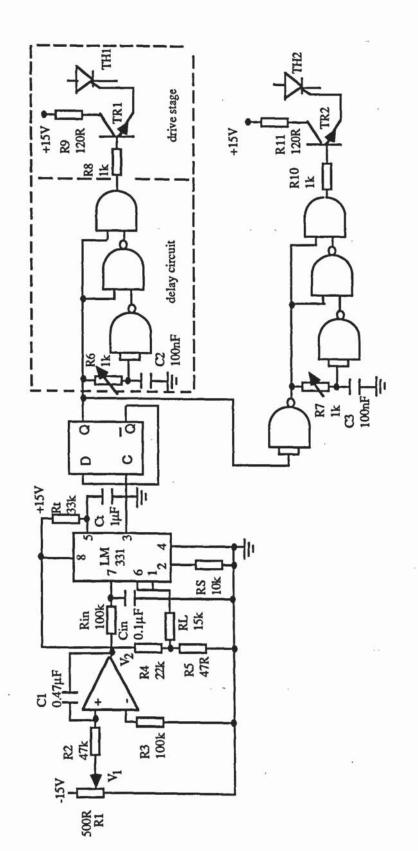

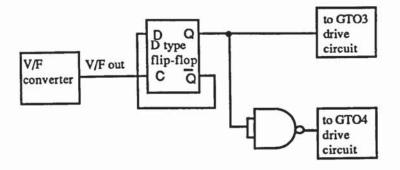

Figure (3-2) shows the thyristor firing circuit for the centre tap inverter which contains an integrator, a voltage-to-frequency converter (V/F), a D type flip flop and various resistors, capacitors and logic gates. Each part of the circuit will be explained individually.

Figure (3-3-a) shows the connections for the integrator and the V/F converter. The integrator uses a 741 operational amplifier with a capacitive feed back. Its input (V<sub>1</sub>) is connected to a DC voltage which produces a current to charge the capacitor (C<sub>1</sub>) with a value equal to V<sub>1</sub>/R<sub>2</sub>.

The current flows in C1 producing a volt drop which equals (65):

$$V_{C1} = \frac{1}{C_1} \int idt = \frac{V_1}{R_2 C_1} \int dt$$

(3-1)

The output voltage of the integrator  $V_2 = -V_{C1}$ . Therefore:

$$V_2 = -\frac{V_1}{C_1 R_2} \int dt$$

(3-2)

The input to the integrator is negative and this gives a positive going output voltage as shown in figure (3-3-b). The integrator output is connected to the input of (V/F) which produces pulses at a frequency proportional to its applied input voltage. In the event of failure of the DC supply, the integrator would try to maintain the output voltage (input of V/F) for a few milliseconds, the output voltage falls at the same rate as the capacitor voltage. The discharging time of the capacitor dependents on the time constant of the circuit. The connections for the V/F converter are given in figure (3-3-a) and the equation for the output frequency (66) is.

$$f_{out} = \frac{V_2}{2.09} \cdot \frac{R_S}{R_L} \cdot \frac{1}{R_t C_t} Hz$$

(3-3)

Where: V2 is the output voltage of the integrator.

The output of the integrator and hence the frequency of V/F converter can be varied by means of the variable resistor R1 which was set to give a frequency of 100 Hz.

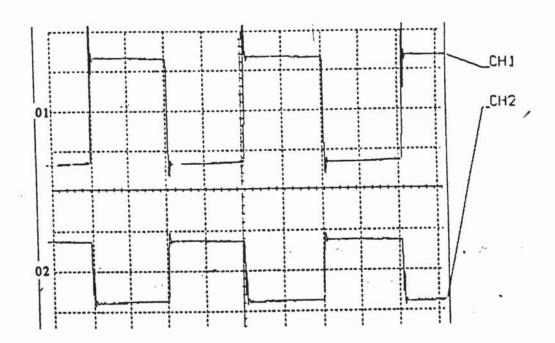

The V/F converter is connected to the D type flip-flop of figure (3-2), which operates as a trigger. A 50% duty cycle is obtained by connecting the complementary output terminal of the flip-flop to its D input and its clock to the output of the V/F converter. The output of the D type flip-flop will change state (high to low or vice versa) at the positive going edge of its clock pulse. In this case, the output frequency of the flip-flop is half the frequency of the V/F converter, as shown in the waveforms of figure (3-4) giving an output of 50 Hz.

Two delay circuits are used, as shown in figure (3-2), to introduce a delay time between the outgoing thyristor and firing the incoming thyristor. Otherwise, a short circuit condition would result through the two thyristors. The value of the delay time depends on the time constants (R6C2 and R7C3). An experiment showed that the optimum delay time to be introduced is 35µS. The operation of the delay circuit is similar to the one which is given in appendix (C).

Each delay circuit output supplies a thyristor drive stage, which contains a transistor and two resistors. When the output of the delay circuit is high (+15 V), a current flows through R8 (or R10) and transistor TR1 (or TR2) turns-on. A current is supplied from the +15 V rail through R9 (or R11) and the emitter of TR1 (or TR2) to the gate of thyristor TH1 (or TH2) to turn it on. The thyristor gate current is approximately 120 mA which is greater than the minimum gate current of 100 mA defined in the device data sheet.

Figure (3-2) Thyristor firing circuit.

(a) Circuit connections.

(b) Circuit waveforms.

Figure (3-3) Integrator and the V/F circuit.

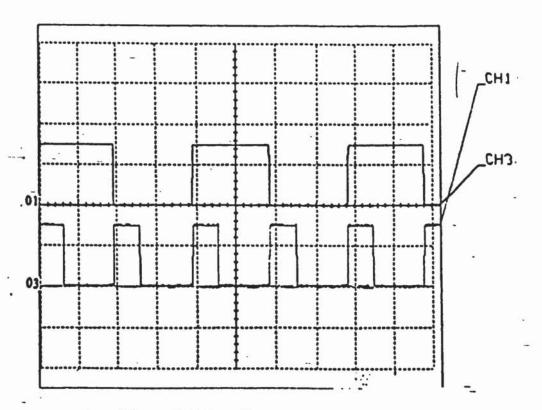

CH1: 10 V/div (output of the V/F).

CH3: 10 V/div (output of the integrator).

Time: 5 ms/div.

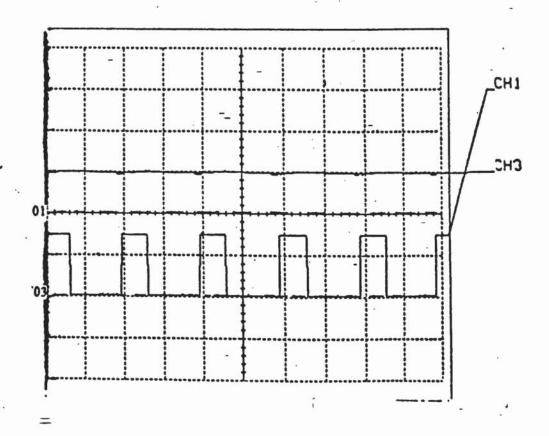

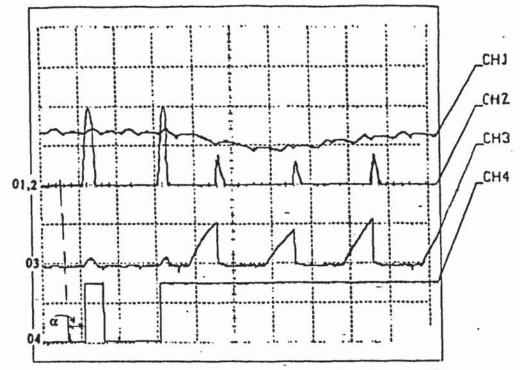

Figure (3-4) Output waveforms of the V/F and the flip-flop.

CH1: 10 V/div (V/F output).

CH3: 10 V/div (D flip flop output).

Time: 5 ms/div.

### 3-3-2 THYRISTOR TURN-OFF TIME,

A thyristor is turned-off by reducing its anode current to a value less than the holding current which is almost zero. The turn-off time (t<sub>0</sub>) is the time required to regain forward blocking capability after forward current has ceased to flow.

The turn-off time of the thyristor operating in a centre tap inverter is given by (67):

$$t_0 = g(x)\sqrt{4LC} \tag{3-4}$$

where:

$$g(x) = \sin^{-1} \left[ \frac{x}{\sqrt{x^2 + 1}} \right] - \sin^{-1} \left[ \frac{x}{2\sqrt{x^2 + 1}} \right]$$

(3-5)

and

$$x = \frac{E_d}{I_{pk}} \sqrt{\frac{4C}{L}}$$

(3-6)

where:

Ed is the inverter input voltage,

Ipk is the peak thyristor current and

L and C are the commutating capacitor and inductance.

The derivation of the above expressions are given in appendix (E).

The centre tap inverters were tested on open-circuit, with a resistive load ( $R = 42 \Omega$ ) and an inductive load (L = 60 mH,  $R = 25 \Omega$ ). These values were chosen to limit the load current to the rating of the inverter ( $I_{LRMS} = 1.5 \text{ A}$ ). As mentioned at the beginning of the chapter, the output of the centre tap inverter is 65 V, so the RMS current for a resistive load is:

$$I_{LRMS} = \frac{V_L}{R} = \frac{65}{42} = 1.54 \text{ A}$$

For an inductive load, the load current grows exponentially given by:

$$I_{L} = \frac{V_{L}}{R} \left( 1 - e^{-tR} \right)$$

(3-7)

To choose the values of inductance and resistance, the following considerations were made. Firstly considering the exponential part of the above equation is much less than 1, the peak load current approximates to:

$$I_{Lpeak} = \frac{V_L}{R} = \frac{65}{25} = 2.6 \text{ A}$$

Secondly, assuming the load current has a triangular waveform, the RMS current is given by:

$$I_{LRMS} = \frac{I_{peak}}{\sqrt{3}} = \frac{2.6}{\sqrt{3}} = 1.5 \text{ A}$$

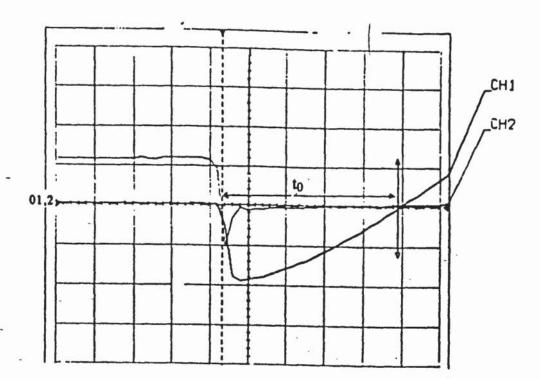

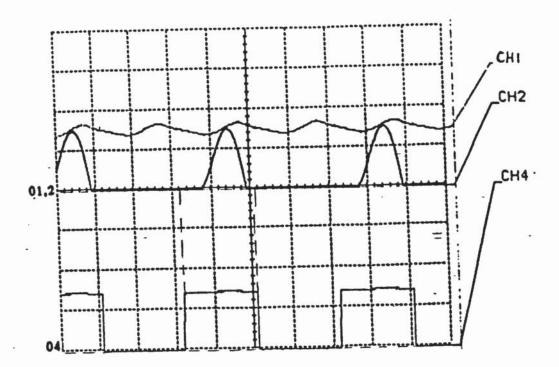

The turn-off time of the thyristors were investigated and compared with the theoretical results shown in table (3-1) and figures (3-5) to (3-7). It was found that the turn-off time of the two thyristors in each inverter is the same so table (3-1) shows the turn off time of one thyristor in each inverter. The oscillograms show the results for one inverter only, since there is not much difference between the waveforms of the two inverters. The inverter input DC voltage was 22 V (the DC supply is 24 V but there is a 2 V drop in the inverter).

Figure (3-5) shows the turn-off time of one thyristor in inverter (A1) with the transformer secondary open circuited. The peak current through the thyristor is 2 A, by using equations (4,5,6):

$$x = 10.77$$

$$g(x) = 0.95$$

$$t_0 = 46.55 \, \mu s$$

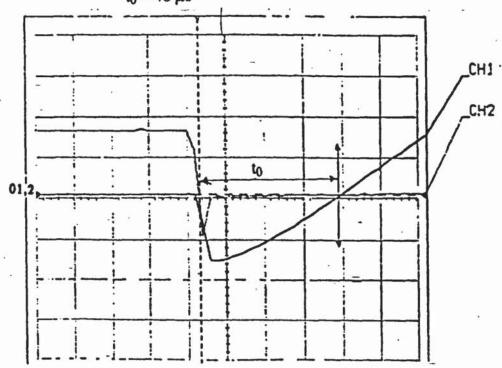

Figure (3-6) shows the turn-off time of one thyristor in inverter (A1) with a resistive load. The peak current through the thyristor is 7.2 A, thus:

$$x = 2.99$$

$$g(x) = 0.75$$

$$t_0 = 36.74 \mu s$$

Figure (3-7) shows the turn off-time of one thyristor in inverter (A1) with an inductive load. The peak current through the thyristor is 11 A, therefore:

$$x = 1.95$$

$$g(x) = 0.63$$

$$t_0 = 30.8 \ \mu s$$

There is a small difference in the turn-off time between the two inverters, with 5% difference for the resistive load and 7% for the inductive load. There is also a small difference between the theoretical and experimental results of about 2.5%. It is believed that these differences may be related to the losses and tolerances of the commutating capacitor and inductance.

|                                              | No load  Ipk= 2 A | Resistive load  I <sub>pk</sub> = 7.2 A | Inductive load  Ipk = 11 A |

|----------------------------------------------|-------------------|-----------------------------------------|----------------------------|

|                                              |                   |                                         |                            |

| Inverter (A) (TH1, TH2) t <sub>0</sub> in μs | 46                | 36                                      | 28                         |

|                                              | (46.5)            | (36.7)                                  | (30.8)                     |

| Inverter (B) (TH1, TH2) t <sub>0</sub> in µs | 46                | 37                                      | 30                         |

|                                              | (46)              | (37)                                    | (33)                       |

Table (3-1) Turn-off time of the thyristors.

(Theoretical values in brackets)

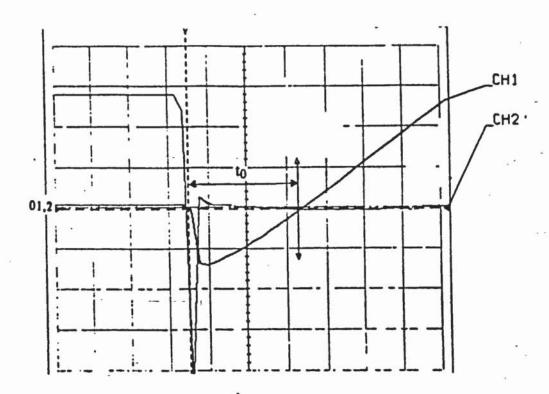

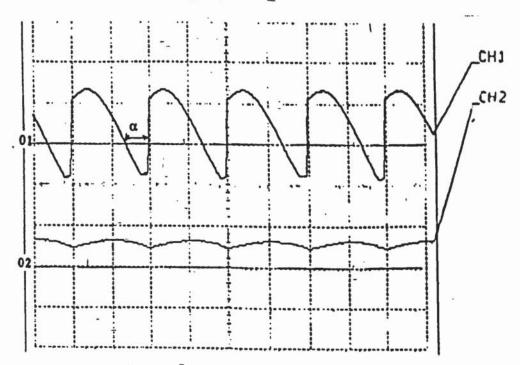

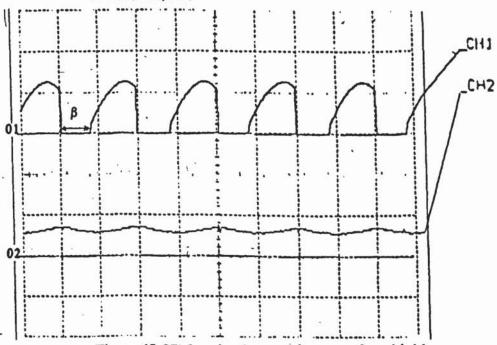

Figure (3-5) Thyristor turn off time on open circuit (A1).

CH1: V<sub>AK</sub> 20 V/div. CH2: I<sub>AK</sub> 1.6 A/div. Time: 10 μs/div.

$t_0 = 46 \, \mu s$

Figure (3-6) Thyristor turn off time with a resistive load (A1).

CH1: V<sub>AK</sub> 20 V/div. CH2: I<sub>AK</sub> 4 A/div.

Time: 10 µs/div.

$t_0 = 36 \, \mu s$ .

Figure (3-7) Thyristor turn off time with an inductive load - (A1).

CH1: V<sub>AK</sub> 20 V/div.

CH2: IAK 4 A/div.

Time:  $10 \mu s/div$ .

$t_0 = 28 \ \mu s.$

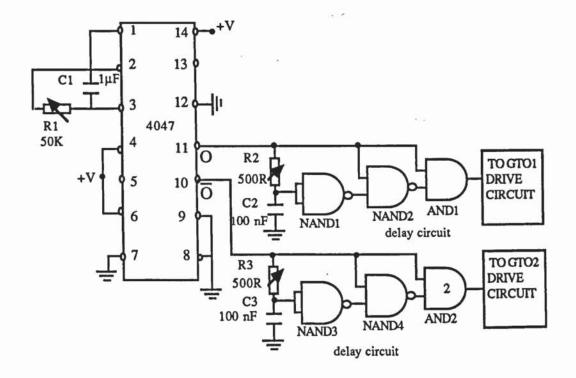

#### 3-4 GTO INVERTER/RECTIFIER DRIVE PULSES.

The gating pulses for the GTOs in the inverter circuit (B2) are obtained from a 4047 CMOS astable multivibrator. The outputs of the 4047 were set to give a 50 Hz frequency with a 10 ms pulse width. Figures (3-8) shows the circuit connections for the inverter drive pulses. According to reference (66), the output frequency is:

$$f = \frac{1}{4.4R_1C_1}$$

Hz (3-8)

A delay circuit is connected to each output of the 4047 to prevent the two GTOs from being on simultaneously. The operation of the delay circuit and its use with an inverter control circuit are explained in appendix (C). The delay time depends on the time constant (R<sub>2</sub>C<sub>2</sub>) and (R<sub>3</sub>C<sub>3</sub>). It was found that the optimum turn-off time for the GTO was 15 μs. This means a 15 μs time delay must be introduced to the turn-on pulse, to allow the complementary device to turn-off.

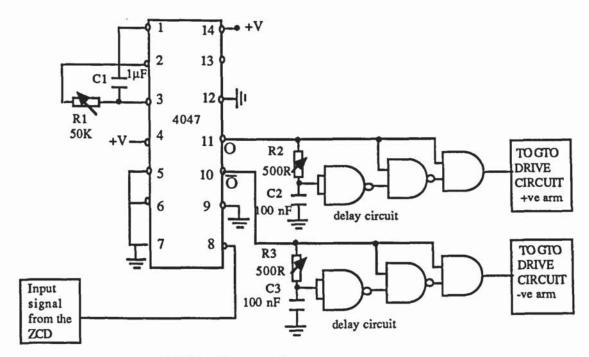

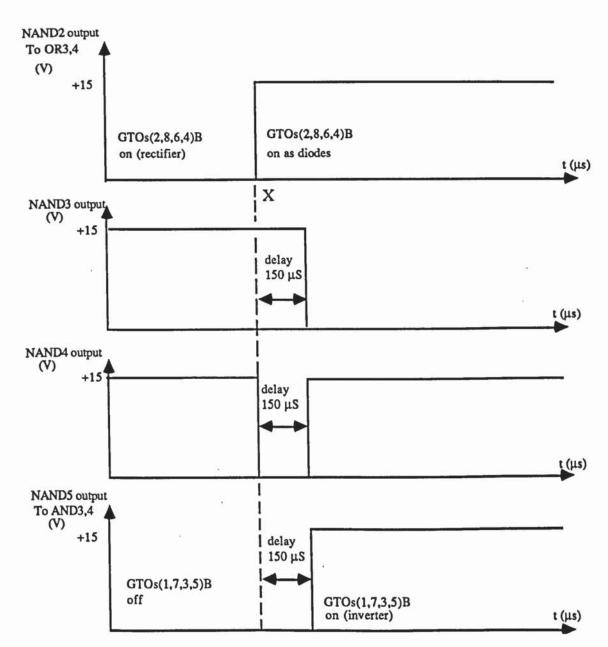

As explained previously, when (B2) operates as a rectifier, GTOs1,2 turn-off and GTOs3,4 turn-on as controlled devices. In order to synchronize the rectifier drive pulses with the output of the centre tap inverter (B1), the drive pulses are taken directly from the output of the D type flip-flop of the thyristor firing circuit. Figures (3-9) (a) and (b) respectively show the circuit connections and the waveforms for the rectifier drive pulses. (Note that, the output voltage at the secondary winding of the transformer of the centre tap inverter is shown so that its synchronization with the driving pulses can be seen).

## 3-5 TRANSISTOR DRIVE CIRCUIT.

When power flows from side (A) to side (B) of the circuit shown in figure (3-1), transistors Ta1 and TB1 turn-on simultaneously to connect the input of inverter (A1) to the 24 V P.S.U and (B1) to the 12 V battery. Transistors TB2 and Ts are turned-off to disconnect the input of inverter (B1) from the 24 V P.S.U and the output of converter (B2) from the load.

When power flows from side (B) to side (A) transistors TA1 and TB1 turn-off to disconnect the centre taps of the transformers (A1) and (B1) from the P.S.U and the battery respectively. Transistors TB2 turn-on, to connect the 24 V P.S.U. to the input of inverter (B1), at the same time transistor Ts turn-on to connect the load to the output of converter (B2) which operates as a rectifier.

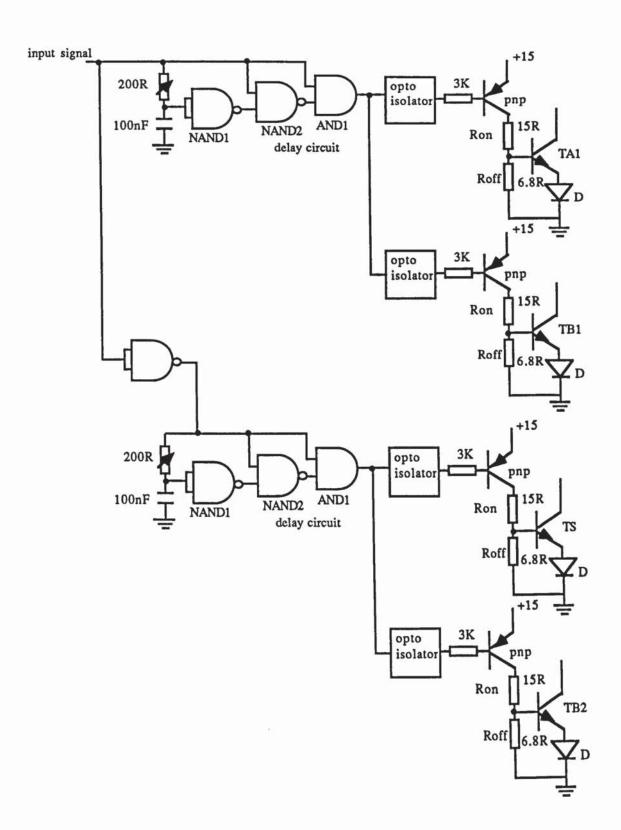

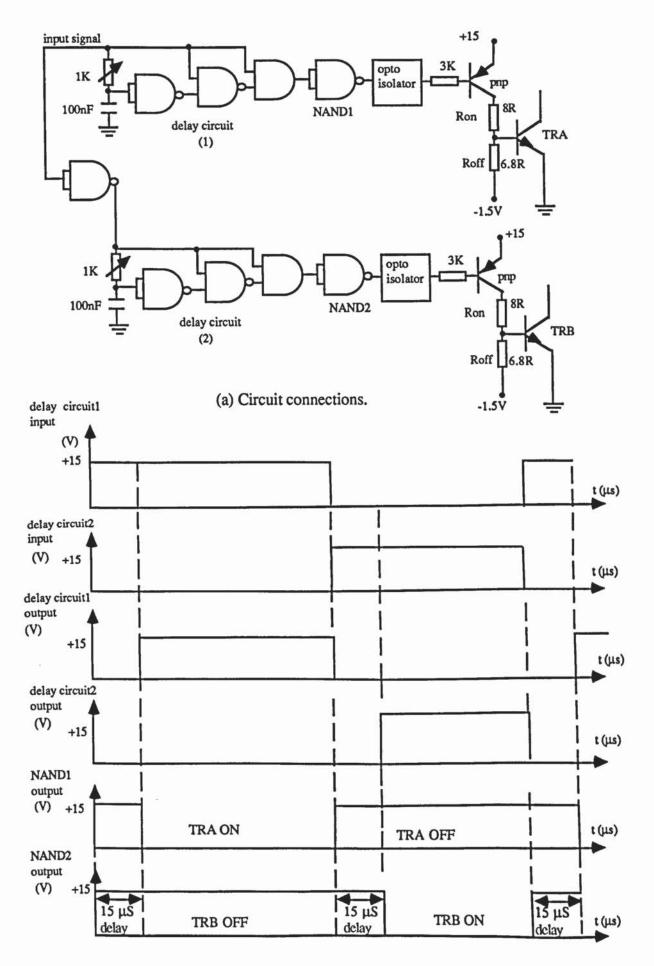

Figure (3-10) shows the drive circuit for the four transistors. Since one pair of these transistors is turning-on whilst the other pair is turning-off, two delay circuits are connected to the inputs of their drive circuits to prevent the two transistor pairs ((TA1,TB1) and (Ts,TB2)) being on simultaneously.

To simplify the explanation of the transistor drive circuit assume that transistor Ta1 is turning-on. When the input signal is low (0 V), the base of the pnp transistor (T1) is low and it turns-on. Current flows from the +15 V rail via Ron to turn Ta1 on.

When the input signal is high, the pnp transistor (T1) turns-off and the voltage drop of the diode D maintains a negative bias between the base and emitter of TA1.

Opto-isolators are used to provide isolation between the control circuit and the base drives of the transistors.

Figure (3-8) GTO inverter drive pulse circuit connections.

(a) Circuit connections.

Figure (3-9) GTO rectifier drive pulse circuit.

(b) Circuit waveforms.

Figure (3-10) Transistor drive circuits.

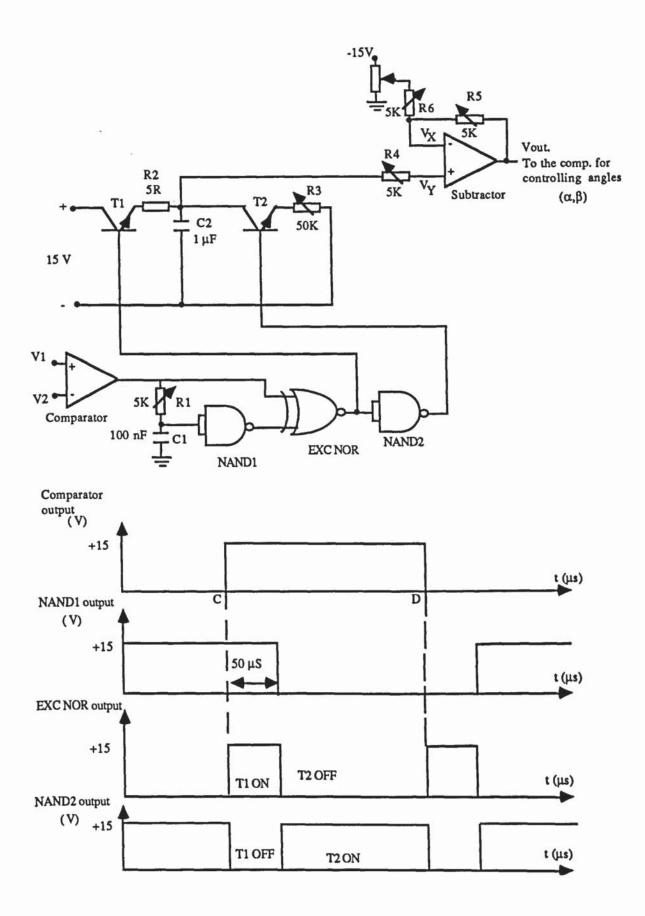

## 3-6 CONTROL CIRCUIT.

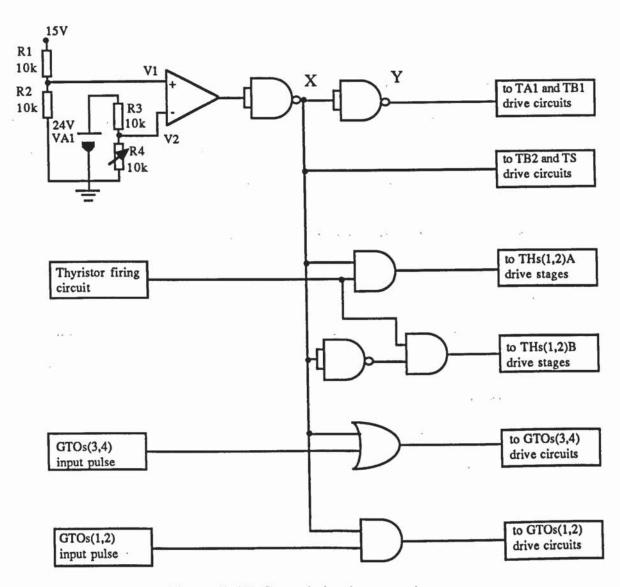

The control circuit of the system shown in figure (3-1) was designed to provide the correct signals to drive the switching devices (transistors, thyristors and GTOs) to send power in both directions. One limitation of this particular control circuit is that it can be controlled from side (A) only. Figure (3-11) shows the connections of the system control circuit. By changing the state of the comparator output, the signals will transfer from one group of devices to another depending on the required direction of the power flow.

As can be seen from figure (3-11), one input of the comparator (V1) is used as a fixed 7.5 V reference, the other input (V2) can be varied by means of the variable resistor R4. When V2 is higher than V1, the comparator output is low. When V2 is lower than V1, the comparator output changes state from low to high level (note that low level means zero and high level means 15 V).

Table (3-2) shows the switching sequences of the control circuit when power flows in both directions. Assuming that power flows from side (A) to (B). (V2 must be higher than V1) the comparator output is low (0 V), point (X) is high and (Y) is low. Therefore:

- 1) Transistor Ta1 turns-on and P.S.U.A1 supplies the inverter (A1).

- 2) The thyristor firing circuit feeds the drive stages of thyristors TH1,2A and (A1) operates as an inverter to supply the rectifier diode bridge (A2).

- 3) The switch transistor Ts turns-off and the rectifier diode bridge (A2) supplies the converter (B2).

- 4) GTO3,4 operate as diodes (always on) and GTO1,2 turn-on, (B2) now operates as an inverter to supply the converter (B1).

5) Transistors TB1 turn-on and TB2 turn-off. Converter (B2) is connected to the battery, at the same time, thyristors TH1,2B turn off, (B2) operates as a rectifier and the battery charges via the diodes.

When reverse power is required, the voltage V2 must be reduced to a value less than 7.5 V, point (X) changes to low state and (Y) changes to high state therefore:

- 1) Transistor TA1 turns-off and the P.S.U.A1 is disconnected from inverter (A1).

- 2) The thyristor firing circuit is disconnected from the drive stage of thyristors TH1,2A to turn them off.

- 3) Transistor TB1 turns-off and TB2 turns-on and converter (B2) is connected to the (P.S.U.B1). At the same time thyristors TH1,2B turn-on and (B2) operates as an inverter to feed (B2).

- 4) GTOs3,4 turn-on to operate as controlled devices and GTOs1,2 turn-off, B2 operates as a rectifier to supply the load.

- 5) The switch transistor Ts turn-on to connect the load to the output of (B2).

Figure (3-11) Control circuit connections.

|                                                                                                                                                                                 | x    | Y    | TA1 | ТВ1 | ТВ2 | TS  | TH<br>1,2<br>A | TH<br>1,2<br>B | GTO<br>1,2            | GTO<br>3,4           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-----|-----|-----|----------------|----------------|-----------------------|----------------------|

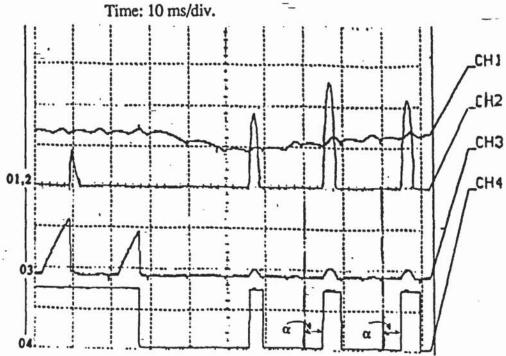

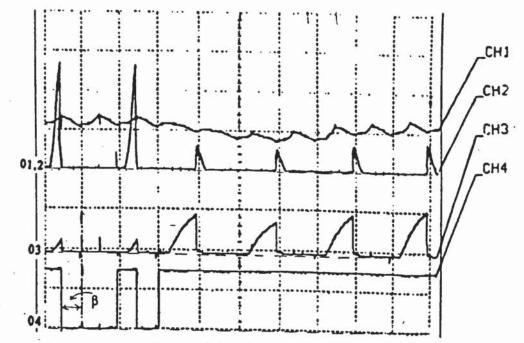

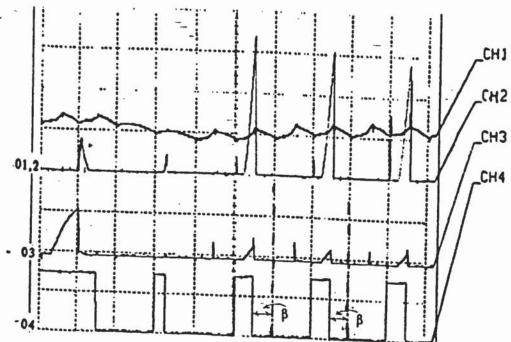

| Power<br>ATOB<br>V2>V1                                                                                                                                                          | high | low  | on  | on  | off | off | on             | off            | on                    | operate<br>as diodes |