## **Control Strategies for Low Voltage DC**

### Microgrids

Ph.D. Thesis

Fulong Li

Doctor of Philosophy

Aston University

July 2019

#### ©Fulong Li, 2019

Fulong Li asserts his moral right to be identified as the author of this thesis

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright belongs to its author and that no quotation from the thesis and no information derived from it may be published without appropriate permission or acknowledgement

## Aston University Control Strategies for Low Voltage DC Microgrids Fulong Li, Doctor of Philosophy, 2019

### **Thesis Summary**

Increasingly, clean renewable energy sources such as wind power and solar power are supplementing and/or replacing, fossil fuels as inputs to electrical grids. Effective and efficient integration of such diverse energy sources, to their full potential, necessitates changes to the architecture and management of those grids. Microgrids provide an effective means for power distribution from renewable energy sources. DC microgrids are well suited to low voltage applications, and have advantages over AC microgrids, including simpler control, higher efficiency and no reactive power. Conventionally, DC microgrids are operated using a hierarchical control scheme. However, complicated control structures add to the cost of microgrids, and limit their application to electrifying remote and developing areas. This thesis focuses on the control of DC microgrids. A set of control strategies based on a modified hierarchical control scheme is proposed for household applications with power coordination, stability enhancement and plug and play performance.

First, a dual-window DC bus interacting method is proposed as a replacement for conventional communication infrastructure. It utilises the advantages of both droop control and DC bus signalling methods. Droop control has plug and play performance and DC bus signalling has the function of automatic power regulation. Low bandwidth signalling between distributed sources can be achieved by manipulating relationships between droop coefficients. With the proposed DC bus interacting method, coordination and power management of distributed energy sources in the absence of communication infrastructure in a DC microgrid may be achieved.

Second, a passive stabiliser is proposed for the primary controller to compensate nonminimum phase in interface converters. The stability performance of an interface converter in a DC microgrid can be optimised by adjusting the feedforward gain in a passive stabiliser. This affects the quiescent operating point and therefore a modified feedforward controller is used in this system. Consequently, potential instability caused by non-minimum phase can be avoided. As a by-product, the passive stabiliser can reduce the required size of the terminal capacitor.

Third, a novel hierarchical control scheme is implemented in a low voltage DC microgrid bench. The passive stabiliser is applied in the primary layer, droop control in the secondary layer, and a six-bit signal series based on the dual-window DC bus voltage interacting method is applied in tertiary layer for power flow control. The impact of bidirectional power flow on battery banks in the system is discussed based on the terminal input admittance analysis. In addition, the small signal model of terminal output admittance under the proposed the passive stabiliser is built. It shows that the proposed system is stable under all possible working modes based on the minor loop gain analysis. The on-grid and off-grid operation modes are conducted, and seamless transfer between them can be achieved. Especially, the surplus power from PV generations is limited, for the power balance consideration, by the proposed modified MPPT algorithm when the system operates under off-grid mode.

Key words: DC microgrids, DC bus interacting control, passive controller, terminal admittance, plug and play.

# Dedication

To my beloved parents,

For their love and support

### Acknowledgements

First of all, I would like to thank my supervisor, Dr. Zhengyu Lin, for his guidance and leading me to the world of power electronics and DC microgrids. I still remember many moments that we discuss the academic problems, paper writing, etc. I am really grateful for his patience and constant support.

Secondly, I would like to thank Zhongnan Qian, Mina Abedi varnosfaderani, Zhengzhao He, Shubo Hu and Corentin Foucault for their company on my first year and I really had a great time to do research with you guys together. Special thanks to Zhongnan for the discussions on my research and Mina for her help on my first-year induction.

Besides, thanks to the EU H2020 project RDC2MT (under grant agreement No. 734796), I have the chances to visit the academic and industrial institutes in the Netherlands, China, and Canada.

In Netherlands, thanks to Martijn de Blook for his help in my life in DCBV and Harry Stokman for impressive discussions on DC protection.

In China, I would like to thank to Prof. Wuhua Li and Dr. Jiande Wu for their guidance. In addition, I would also like to thank Zhongnan Qian, Weihao Zhou, Ruichi Wang, Jiawei Hu, Ye Yan, etc., for their help and support on both my life and research in Zhejiang University. I would also like to thank Prof. Alian Chen in Shandong University for her suggestions on my research, and other excellent researchers in Shandong University, Xiangyang Xing, Changwei Qin, Xiaoyan Li, etc.

In Canada, I would like to thank Prof. Claudio Canizares for his guidance and great suggestions on DC microgrid optimisations. I would also like to thank Dr. Mauricio Restrepo. We had many impressive discussions on our research and life. Besides, I need to thank to other researchers in this group, Noela Sofía Guzmán, Ivan Calero and Dario Peralta for my great life in University of Waterloo. Besides, I would like to thank Nils van der Blij. It was really great time to be with you talking about research and life during the time in University of Waterloo.

Last but not least, to my colleague, Muhannad Al-Shareef, and he is the only person who is being with me all three years. We had countless moments on research discussions, life in the Netherlands, Christmas, and mutual encouragement on our path to pursue Ph.D.

There are too many stories and people in the past three years. Apology for that I cannot list them all. All these memories will become the treasure of my life.

Fulong Li

July 2019

## List of Contents

| Thesis Summary2                                        |

|--------------------------------------------------------|

| Dedication                                             |

| Acknowledgements                                       |

| List of Contents                                       |

| List of Tables                                         |

| List of Figures                                        |

| Abbreviations                                          |

| Symbols                                                |

| Chapter 1 Introduction                                 |

| 1.1 Background24                                       |

| 1.2 Definition and Configuration of Microgrid26        |

| 1.2.1 AC and DC microgrids                             |

| 1.2.2 DC Microgrids— Applications and State of the Art |

| 1.3 Objectives and Structure of Thesis                 |

| Chapter 2 Literature Review                            |

| 2.1 Control Strategies in DC Microgrids                |

| 2.1.1 Control Concepts in DC Microgrids                           |    |

|-------------------------------------------------------------------|----|

| 2.1.2 Hierarchical Control Scheme                                 |    |

| 2.1.3 Droop Control and Variations                                | 41 |

| 2.1.4 DC Bus Signalling                                           | 45 |

| 2.1.5 Power Line Signalling/Communication                         | 47 |

| 2.2 Stability Analysis in DC Microgrids                           |    |

| 2.2.1 Stability Analysis Methods                                  |    |

| 2.2.2 Instability Factors in DC Microgrids                        |    |

| 2.2.3 Linear Stability Criteria                                   |    |

| 2.2.4 Stabilisation Methods in DC Microgrids                      |    |

| 2.3 Conclusions and Problem Statements                            | 60 |

| Chapter 3 Introduction of DC Microgrid Bench                      |    |

| 3.1 Low Voltage DC Microgrid Bench                                | 62 |

| 3.2 Design of interface converters                                | 64 |

| 3.2.1 Power Board                                                 | 66 |

| 3.2.2 Control Board                                               | 68 |

| 3.3 Configurations of Distributed Sources                         | 69 |

| 3.4 Conclusions                                                   | 71 |

| Chapter 4 Dual-window DC Bus Interacting Method for DC Microgrids | 72 |

| 4.1 Mechanism of DC Bus Interacting Method                        |    |

| 4.2 Discussion of Droop Curves                                    | 74 |

| 4.3 Principle of the DC Bus Interacting Method                    | 77 |

| 4.4 Signal Series Design                                          | 79 |

| 4.4.1 Signal Series and Extendibility                                                  | 79  |

|----------------------------------------------------------------------------------------|-----|

| 4.4.2 Discussions of Signal Magnitude and Width                                        | 81  |

| 4.5 Experimental Validations                                                           | 82  |

| 4.5.1 Negative Interacting Current Modification                                        | 83  |

| 4.5.2 A Simple Case Study                                                              | 85  |

| 4.6 Conclusions                                                                        | 87  |

| Chapter 5 Passive Stabilisers Design for Interface Converters                          | 88  |

| 5.1 Passive Theory—Brief Introduction                                                  | 88  |

| 5.2 Passivation for Interface Converters                                               | 91  |

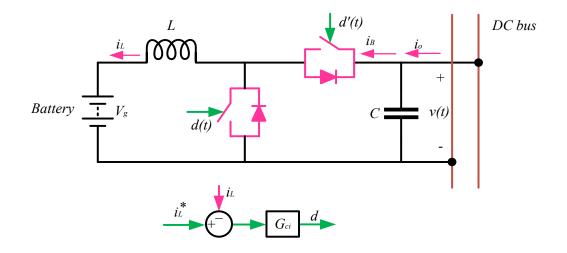

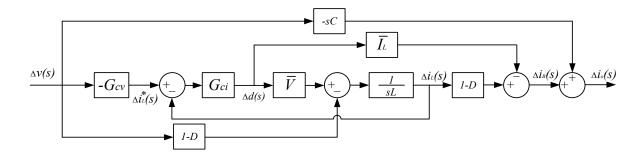

| 5.2.1 Modelling and Analysis of Interface Converters                                   | 91  |

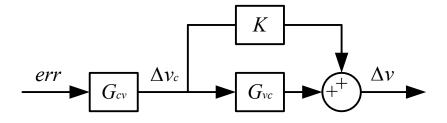

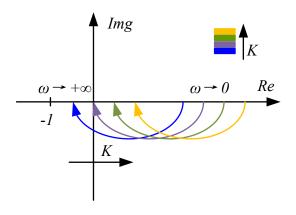

| 5.2.2 Passivation with Feedforward Gain K                                              | 96  |

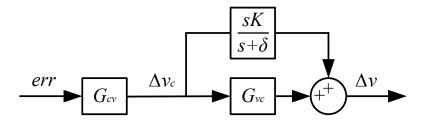

| 5.2.3 Passivation with Feedforward HPF-K                                               | 97  |

| 5.3 Discussion and Design                                                              | 99  |

| 5.3.1 Controllers Design                                                               | 99  |

| 5.3.2 Discreteness of Controllers                                                      | 101 |

| 5.4 Experimental Validation                                                            | 104 |

| 5.4.1 Validation of Passive Stabilisers                                                | 104 |

| 5.4.2 Modified Passive Stabilisers                                                     | 105 |

| 5.5 Conclusions                                                                        | 107 |

| Chapter 6 Operation of DC Microgrids with Enhanced Stability in a Hierarchical Control |     |

| Scheme                                                                                 | 108 |

| 6.1 System Control Configurations                                                      | 109 |

| 6.1.1 Definitions of Each Control Layer                                                | 109 |

| 6.1.2 System Control Diagram                   | 109 |

|------------------------------------------------|-----|

| 6.2 Terminal Admittance Modelling and Analysis | 112 |

| 6.2.1 Load Side Input Admittance               | 112 |

| 6.2.2 Source Side Output Admittance            | 116 |

| 6.3 Signal Series Interpretations              | 121 |

| 6.4 Algorithms and State Machine               | 123 |

| 6.4.1 PV Power Limitation Algorithm            | 123 |

| 6.4.2 System State Machine                     | 125 |

| 6.5 Experimental Validations                   | 128 |

| 6.5.1 On-grid operations                       | 129 |

| 6.5.2 Off-grid operations                      | 135 |

| 6.6 Conclusions                                | 138 |

| Chapter 7 Conclusions and Future Work          | 139 |

| 7.1 Conclusions                                | 139 |

| 7.2 Future Work                                | 140 |

| 7.3 Author's Publications                      | 142 |

| Reference                                      | 144 |

| Appendix                                       | 154 |

| A1. Design of Interface Converters             | 155 |

| A2. Values of Passive Components               | 158 |

| A3. Passive Stabiliser Design                  | 159 |

| A3.1 Calculations for Passive Controller       | 159 |

| A3.2 Negative Frequency Calculations           | 160 |

| A4. Terminal Input Admittance Calculations     | 161 |

|------------------------------------------------|-----|

| A4.1 Constant Power Load                       | 161 |

| A4.2 Constant Power Source                     | 162 |

| A5. Terminal Output Admittance Calculations    | 164 |

| A5.1 Passive Stabilisers with Droop Control    | 164 |

| A5.2 Droop Control without Passive Stabilisers | 169 |

| A5.3 Passive Stabilisers without Droop Control | 171 |

| A5.4 Initial Double Loop Control               | 174 |

| A6. Signal Series Explanations                 | 176 |

# List of Tables

| Table 2-1 Comparisons of minor loop gain based stability criteria.    | 56  |

|-----------------------------------------------------------------------|-----|

| Table 3-1 Specification of interface converter.                       | 64  |

| Table 3-2 Component list of power board                               | 67  |

| Table 3-3 Component list of control board.                            | 68  |

| Table 3-4 Parameters for the converter connections.                   | 70  |

| Table 4-1 Signal series design with different pulse widths.           | 80  |

| Table 4-2 List of experimental parameters for dual-window DBI method. | 82  |

| Table 5-1 Parameters used in both simulations and experiment.         | 102 |

| Table 6-1 Signal series design with six bits.                         | 122 |

| Table 6-2 Data of experimental setup for plug and play operation      | 128 |

# **List of Figures**

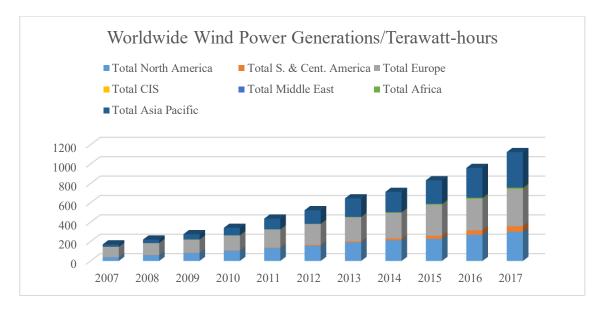

| Figure 1.1 Worldwide wind power generations from 2007 to 201725                              |

|----------------------------------------------------------------------------------------------|

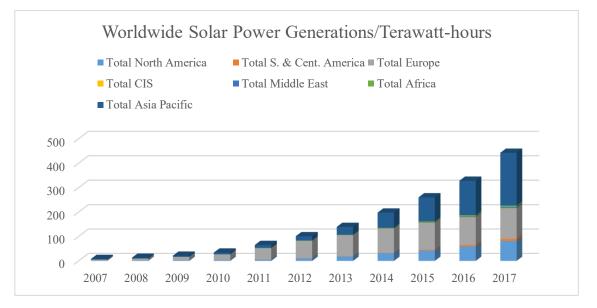

| Figure 1.2 Worldwide solar power generations from 2007 to 201725                             |

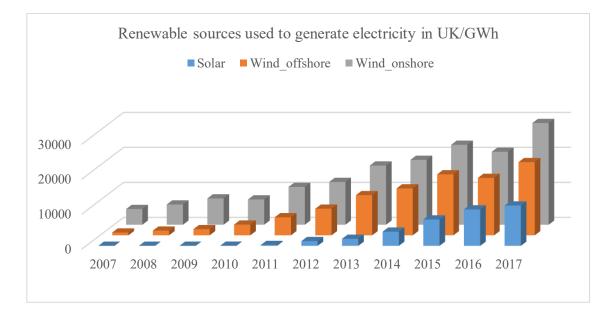

| Figure 1.3 Wind and solar energy electricity contribution in UK from 2007 to 201726          |

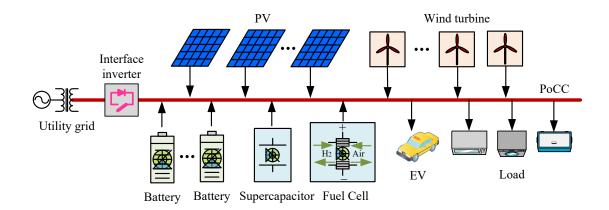

| Figure 1.4 A typical microgrid configuration27                                               |

| Figure 1.5 Power distribution structure                                                      |

| Figure 1.6 A typical AC microgrid configuration                                              |

| Figure 1.7 A typical DC microgrid configuration                                              |

| Figure 2.1 Diagram [24] of centralised (a), decentralised (b) and distributed (c) control    |

| networks                                                                                     |

| Figure 2.2 Hierarchical control scheme of interface converters in DC microgrids              |

| Figure 2.3 Modified MSC with diode array                                                     |

| Figure 2.4 Master-slave control for distributed power systems                                |

| Figure 2.5 Equivalent circuit of two paralleled distributed energy sources                   |

| Figure 2.6 Droop curves in DC microgrids; (a) output current based droop control; (b) output |

| power based droop control                                                                    |

| Figure 2.7 Bus restoration with low bandwidth communications                                 |

| Figure 2.8 Diagram for voltage level signalling and DC bus signalling control methods        |

| Figure 2.9 Control blocks for DBS method                                                     |

| Figure 2.10 Mechanism of mode-adaptive DBS droop control methods47                             |

|------------------------------------------------------------------------------------------------|

| Figure 2.11 The mechanism of power line signalling/communication                               |

| Figure 2.12 Domain of attraction for large signal nonlinear stability criteria                 |

| Figure 2.13 Discrimination of the sources and loads in a DC microgrid                          |

| Figure 2.14 Diagram for showing negative incremental resistance caused by constant power       |

| load                                                                                           |

| Figure 2.15 Impedance interaction with input filter                                            |

| Figure 2.16 Interaction of a cascaded interface converter system                               |

| Figure 2.17 Various criteria for stability boundary                                            |

| Figure 2.18 System impedance analysis                                                          |

| Figure 2.19 Total bus impedance analysis                                                       |

| Figure 3.1 An overview of DC microgrid bench                                                   |

| Figure 3.2 Configuration of DC microgrid bench                                                 |

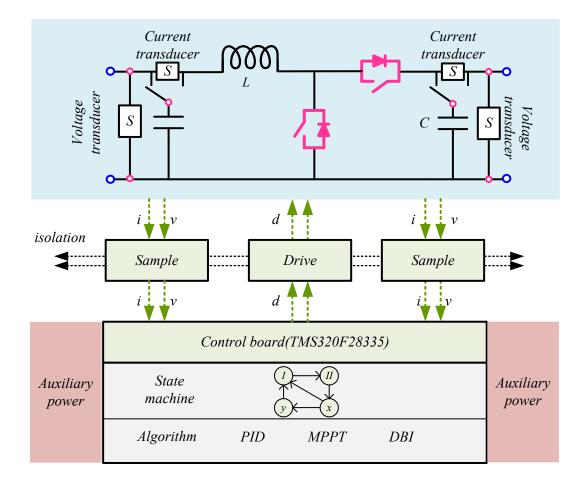

| Figure 3.3 Block diagram of the interface converter                                            |

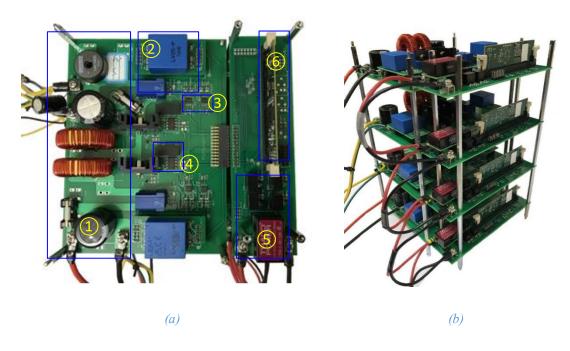

| Figure 3.4 Prototype of low voltage DC microgrids. (a) the front view of interface converters; |

| (b) setup of interface converters for DC microgrids                                            |

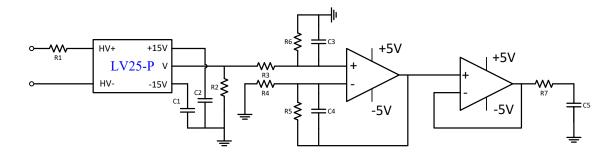

| Figure 3.5 Voltage sampling circuit                                                            |

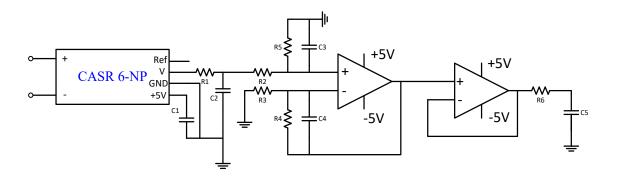

| Figure 3.6 Current sampling circuit                                                            |

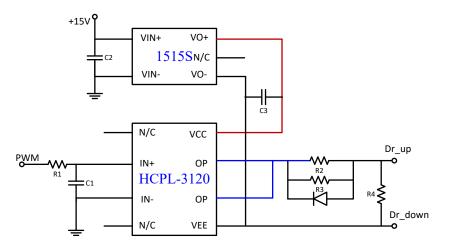

| Figure 3.7 MOSFET drive circuit                                                                |

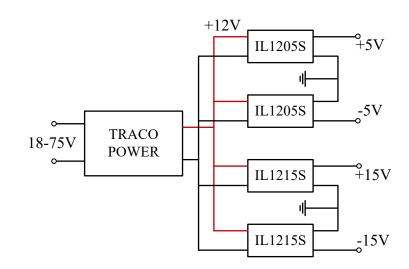

| Figure 3.8 Auxiliary power circuit                                                             |

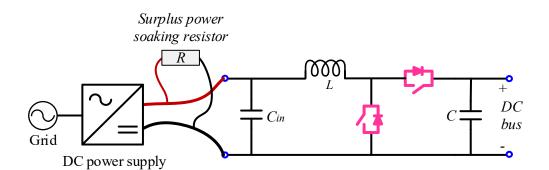

| Figure 3.9 Emulated grid connections                                                           |

| Figure 3.10 Battery connections                                                                |

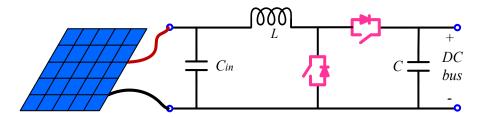

| Figure 3.11 PV panel connections70                                                             |

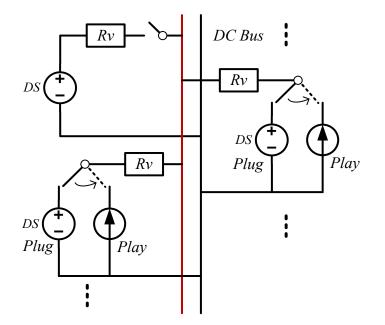

| Figure 4.1 General mechanism of proposed DBI method73                                          |

| Figure 4.2 Two-node equivalent model of interface converters.                                     | 74  |

|---------------------------------------------------------------------------------------------------|-----|

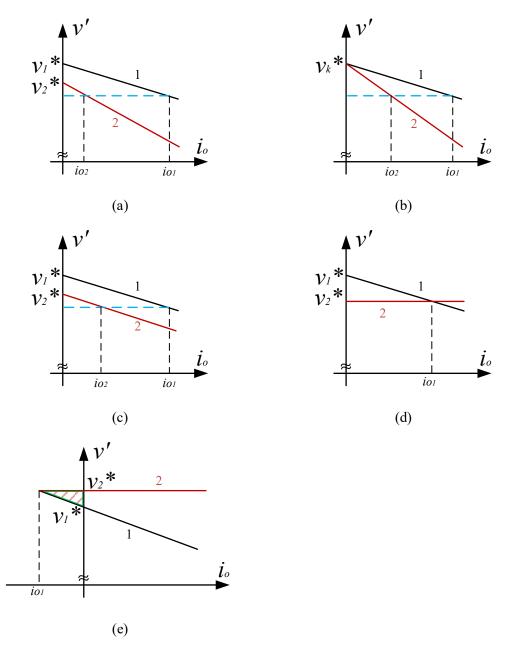

| Figure 4.3 Various droop curve combinations. (a) droop curves with different floating voltage     | es  |

| and droop coefficients; (b) droop curves with identical floating voltage but different droop      |     |

| coefficients; (c) droop curves with different floating voltages but identical droop coefficients; | ;   |

| (d) droop curves with zero droop coefficient and point of intersection at right side; (e) droop   |     |

| curves with zero droop coefficient and point of intersection at left side                         | 75  |

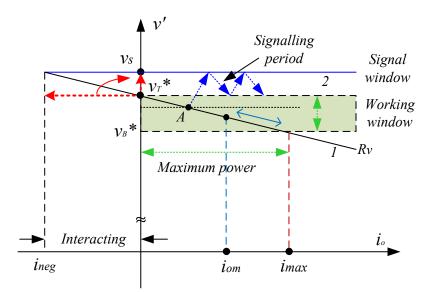

| Figure 4.4 Dual window droop curves of interface converters                                       | 77  |

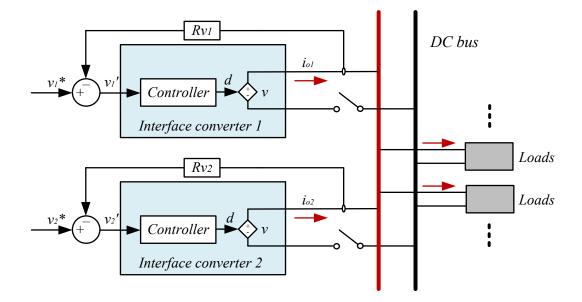

| Figure 4.5 Control block of proposed DBI method.                                                  | 79  |

| Figure 4.6 Control block of proposed DBI method with negative interacting current                 |     |

| modification                                                                                      | 79  |

| Figure 4.7 Signal series design with fixed pulse width and multiple bits.                         | 80  |

| Figure 4.8 Experimental configuration for validating proposed DBI method                          | 82  |

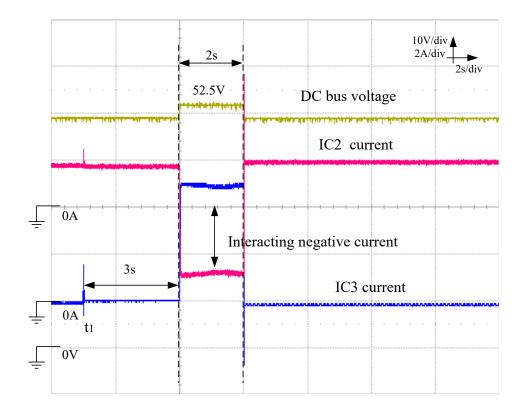

| Figure 4.9 Experimental results of DBI method with negative interacting current.                  | 84  |

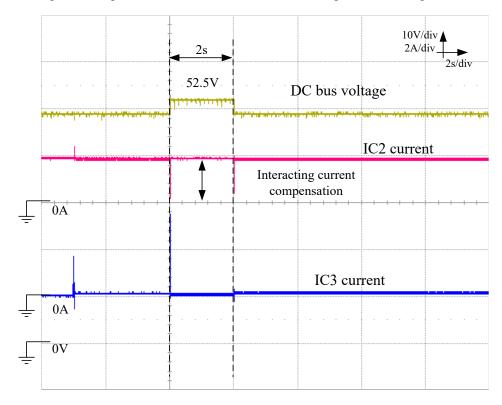

| Figure 4.10 Experimental results of DBI method with positive interacting current compensation     | on. |

|                                                                                                   | 84  |

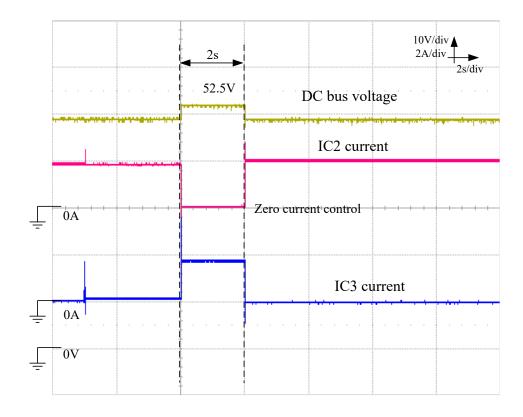

| Figure 4.11 Experimental results of DBI method with zero interacting current compensation.        | .85 |

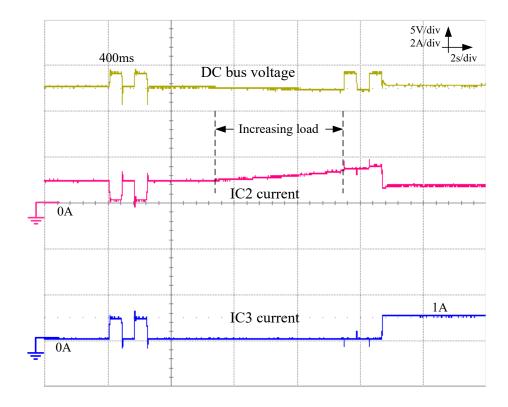

| Figure 4.12 Experimental results of signalling with proposed DBI method, ON case                  | 86  |

| Figure 4.13 Experimental results of signalling with proposed DBI method, OFF case                 | 86  |

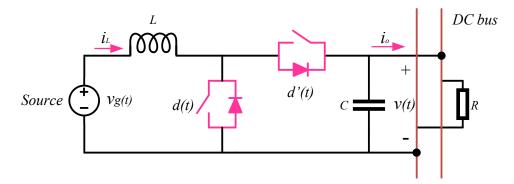

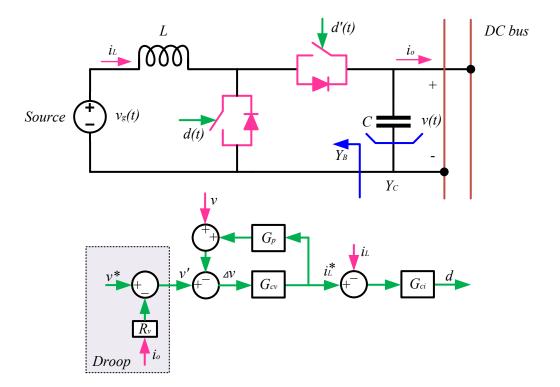

| Figure 5.1 Interface converter in DC microgrids                                                   | 91  |

| Figure 5.2 Equivalent model of Boost converter                                                    | 92  |

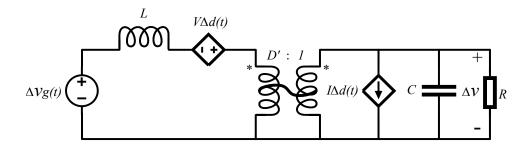

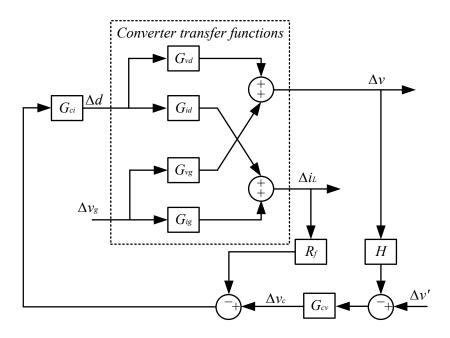

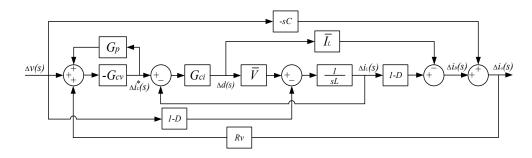

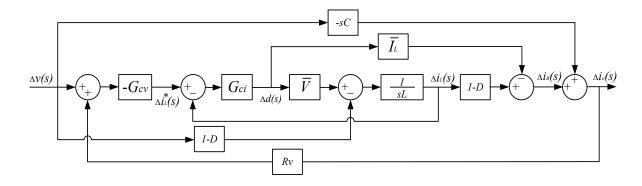

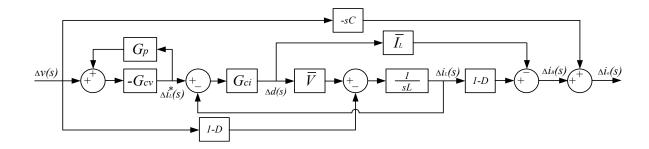

| Figure 5.3 Converters transfer function map                                                       | 93  |

| Figure 5.4 Nyquist plot of outer loop control plant.                                              | 94  |

| Figure 5.5 Control blocks of feedforward compensation for outer loop plant                        | 96  |

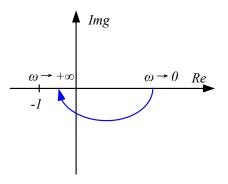

| Figure 5.6 Nyquist plot analysis for passivation with K.                                          | 97  |

| Figure 5.7 Control blocks feedforward compensation for outer loop plant with high pass filter. |    |

|------------------------------------------------------------------------------------------------|----|

|                                                                                                | 98 |

| Figure 5.8 Nyquist plot analysis for passivation with HPF-K                                    | 99 |

| Figure 5.9 Full sketch of control block for interface converter10                              | 00 |

| Figure 5.10 Nyquist plot passivation with K10                                                  | 03 |

| Figure 5.11 Nyquist plot passivation with HPF-K10                                              | 03 |

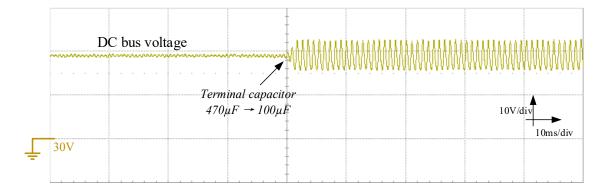

| Figure 5.12 Reducing the terminal capacitor to make the system oscillate10                     | 04 |

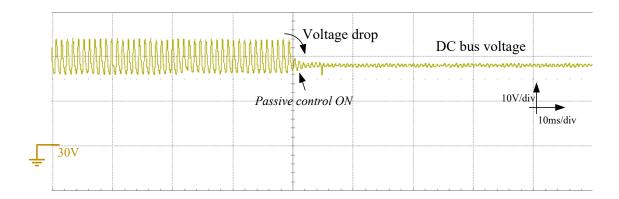

| Figure 5.13 Unstable case becomes stable by applying passive control with expected voltage     |    |

| drop10                                                                                         | 05 |

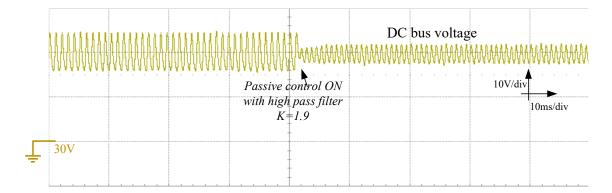

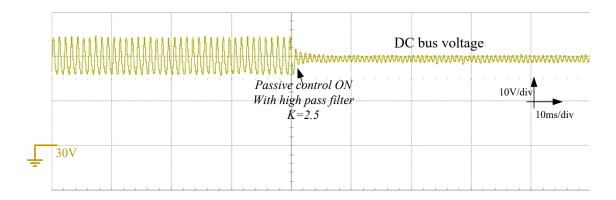

| Figure 5.14 Unstable case becomes stable by applying passive control with HPF, K=1.910         | 05 |

| Figure 5.15 Unstable case becomes stable by applying passive control with HPF, K=2.510         | 06 |

| Figure 5.16 Instability occurs when the passivation controller is removed from two parallel    |    |

| interface converters with average current sharing droop control10                              | 06 |

| Figure 6.1 Functions of each control layer in hierarchical control scheme                      | 09 |

| Figure 6.2 System control configuration diagram                                                | 11 |

| Figure 6.3 Terminal admittance modelling for battery charging mode1                            | 12 |

| Figure 6.4 Signal flow chart of terminal admittance for battery charging mode                  | 13 |

| Figure 6.5 Terminal admittance of CPL and CPS1                                                 | 15 |

| Figure 6.6 Circuit diagram and control blocks for terminal admittance evaluations1             | 15 |

| Figure 6.7 Signal flow chart of terminal admittance1                                           | 16 |

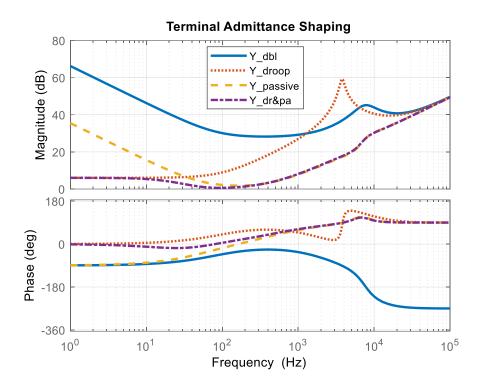

| Figure 6.8 Terminal admittance shaping of interface converter by passive stabilisers12         | 20 |

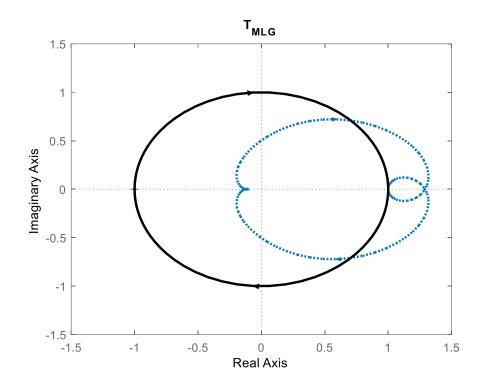

| Figure 6.9 Minor loop gain of passive controller with CPL12                                    | 20 |

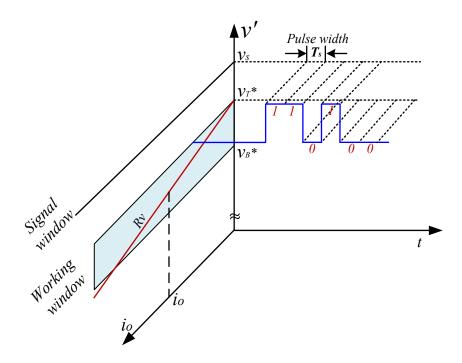

| Figure 6.10 Signal series sample in 3-D plot12                                                 | 23 |

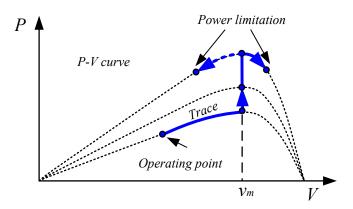

| Figure 6.11 PV predicted tracking curve of power limitation                                    | 24 |

1. : . 1 £14 ъ: 1 1 1 10 1 \_ • . 1

| Figure 6.12 Battery characteristics of DC microgrids with droop control                       |

|-----------------------------------------------------------------------------------------------|

| Figure 6.13 Flow chart of algorithm for PV surplus power limitation125                        |

| Figure 6.14 State machine of signal series sending and receiving                              |

| Figure 6.15 State machine switches of different working modes                                 |

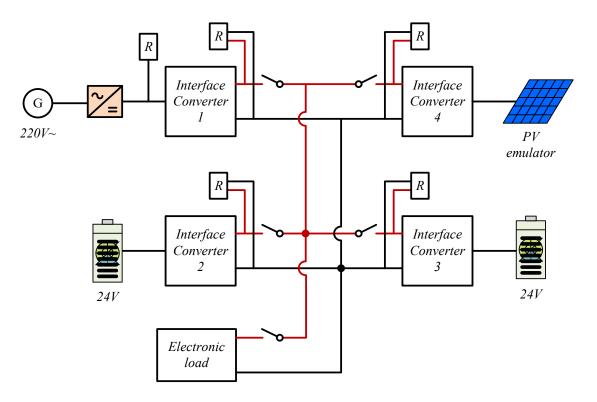

| Figure 6.16 Configuration of experimental setup128                                            |

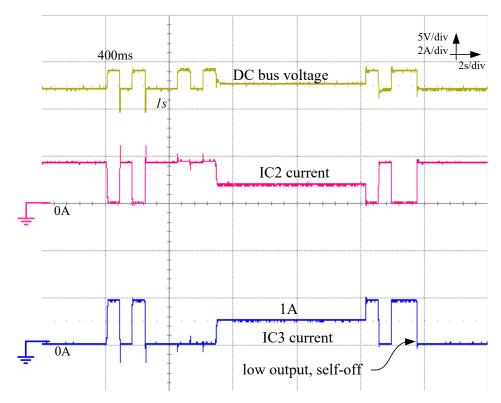

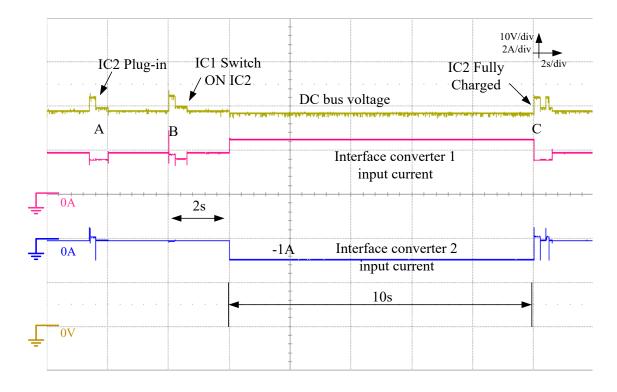

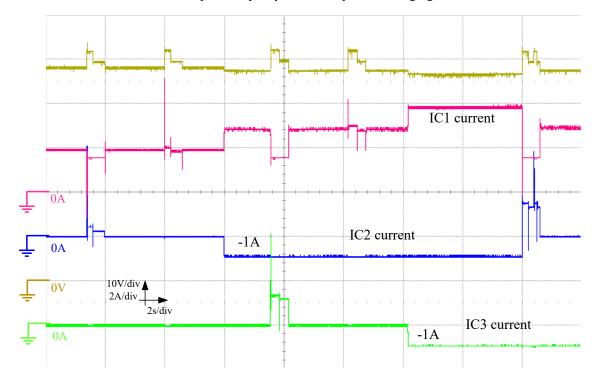

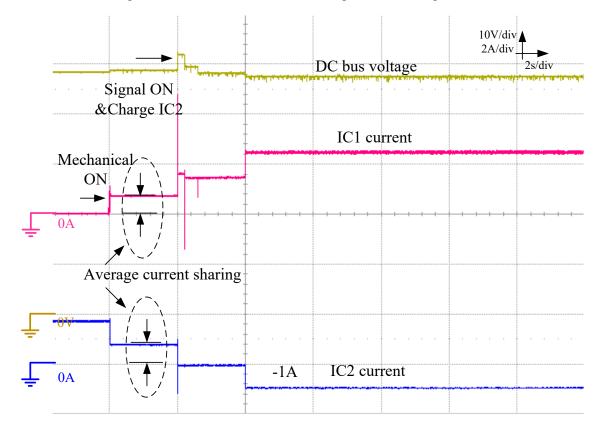

| Figure 6.17 System operation under on-grid mode; IC2 is plugged in at low power capacity and  |

| then IC1 switches on IC2 to absorb power from the DC microgrid with a charging current of     |

| 1A                                                                                            |

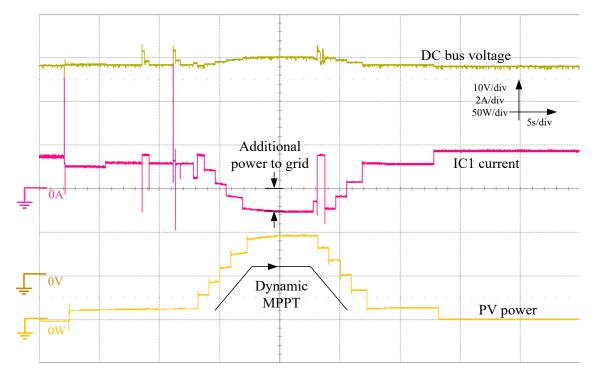

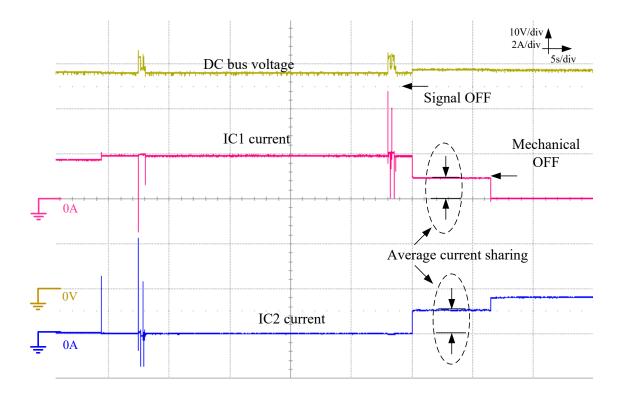

| Figure 6.18 System operation under on-grid mode; IC2 is plugged in at full power capacity and |

| the additional power from the PV generations will be supplied to the grid                     |

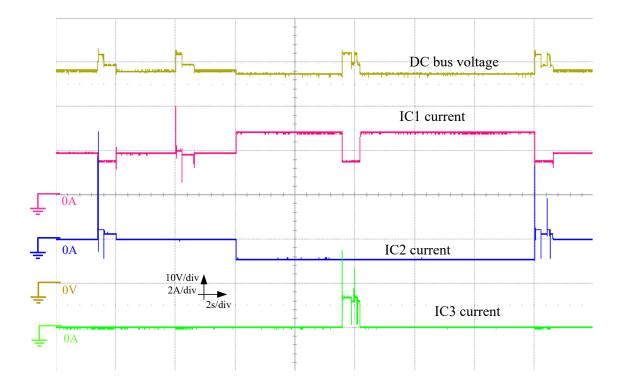

| Figure 6.19 System operation under on-grid mode; IC2 is plugged in at low power capacity and  |

| then IC1 switches on IC2 to absorb power from the DC microgrid with a charging current of     |

| 1A; IC3 is plugged in at full power capacity and is ready for discharging                     |

| Figure 6.20 System operation under on-grid mode; IC2 is plugged in at low power capacity and  |

| then IC1 switches on IC2 to absorb power from the DC microgrid with a charging current of     |

| 1A; IC3 is plugged in at low power capacity and then IC1 switches on IC3 to absorb power      |

| from the DC microgrid with a charging current of 1A132                                        |

| Figure 6.21 Seamless alternation from on-grid mode to off-grid mode134                        |

| Figure 6.22 Seamless alternation from off-grid mode to on-grid mode134                        |

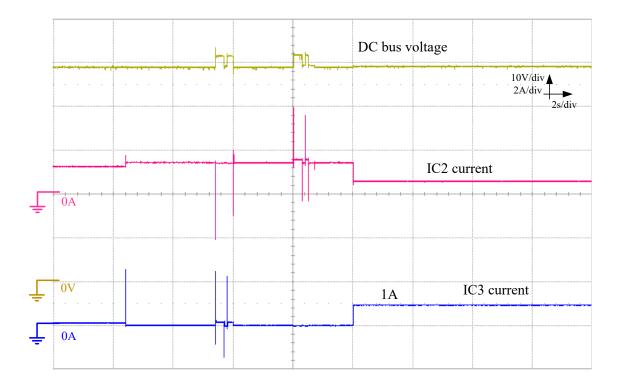

| Figure 6.23 System operation under off-grid mode; IC3 is plugged in and is able to supply the |

| power to the DC microgrid, then IC2 switches on IC3 and supplies the load with 1A due to the  |

| light load136                                                                                 |

| Figure 6.24 System operation under off-grid mode; IC3 is plugged in and is able to supply the |

| power to the DC microgrid, then IC2 switches on IC3 with 2A due to the dynamically instant    |

| heavy load                                                                                    |

| Figure 6.25 System operation under off-grid mode; IC3 is plugged in and needs power from the     |

|--------------------------------------------------------------------------------------------------|

| DC microgrid, IC2 needs power as well; IC2 absorbs power first; when it is full, then IC2        |

| switches on IC3 and absorbes power at 1A137                                                      |

| Figure 6.26 System operation under off-grid mode; IC3 is plugged in and at full SoC state, and   |

| IC2 is also nearly at full SoC, then the PV output power is limited and operating point moves to |

| the right side                                                                                   |

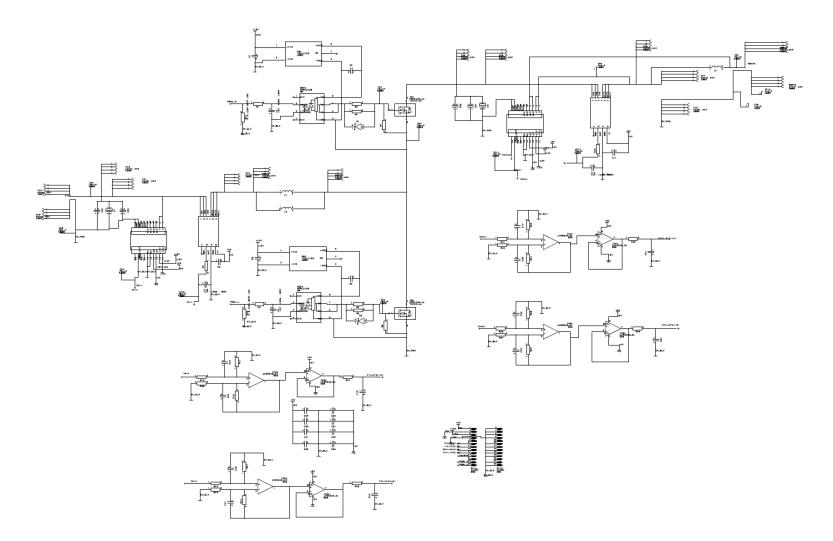

| Figure A. 1 Schematic of control board.                                          | 155 |

|----------------------------------------------------------------------------------|-----|

| Figure A. 2 Schematic of power board.                                            | 156 |

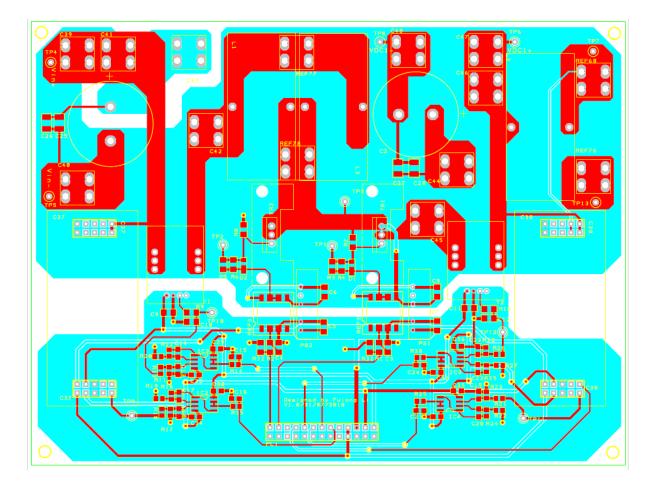

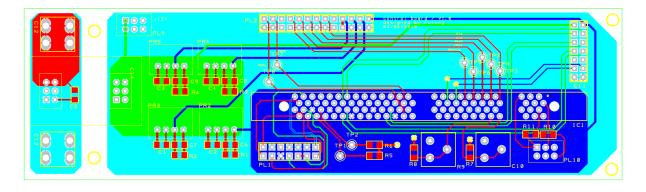

| Figure A. 3 PCB layout of power board                                            | 157 |

| Figure A. 4 PCB layout of control board                                          | 157 |

| Figure A. 5 Circuit and control block diagram of constant power load             | 161 |

| Figure A. 6 Signal flow chart of constant power load.                            | 161 |

| Figure A. 7 Circuit and control diagram of constant power source.                | 162 |

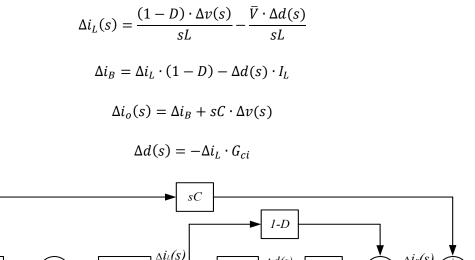

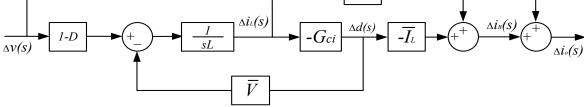

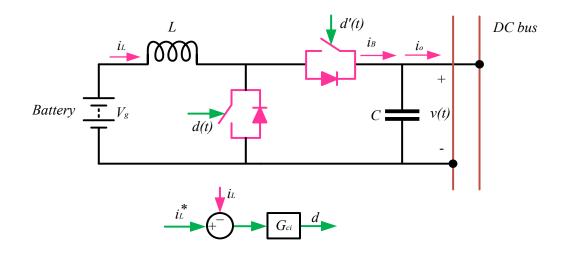

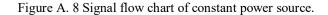

| Figure A. 8 Signal flow chart of constant power source.                          | 163 |

| Figure A. 9 Circuit and control blcok diagram of source side converter.          | 165 |

| Figure A. 10 Signal flow chart of source side converter - whole controller       | 166 |

| Figure A. 11 Signal flow chart of source side converter - droop controller       | 169 |

| Figure A. 12 Signal flow chart of source side converter - passive controller     | 171 |

| Figure A. 13 Signal flow chart of source side converter - double loop controller | 174 |

## Abbreviations

| Abbreviations | Full meaning |

|---------------|--------------|

|---------------|--------------|

| ac    | Alternate current small signal analysis |

|-------|-----------------------------------------|

| AC    | Alternating current                     |

| CC    | Central controller                      |

| CPL   | Constant power load                     |

| CPS   | Constant power source                   |

| CS    | Current source                          |

| DBI   | DC bus interacting                      |

| DBS   | DC bus signalling                       |

| DC    | Direct current                          |

| DES   | Distributed energy source               |

| DG    | Distributed generator                   |

| DoA   | Domain of attraction                    |

| DOA   | Design-oriented analysis                |

| DS    | Distributed source                      |

| DSP   | Digital signal processor                |

| ES    | Energy storage                          |

| ESAC  | Energy source analysis consortium       |

| EV    | Electrical vehicle                      |

| GMPMC | Gain margin and phase margin criterion  |

| HPF   | High pass filter                        |

| HV   | High voltage                         |

|------|--------------------------------------|

| IC   | Interface converter                  |

| LBC  | Low bandwidth communication          |

| LTI  | Linear time invariant                |

| LPF  | Low pass filter                      |

| MAC  | Multi-agent control                  |

| MGF  | Mason's gain formula                 |

| MLG  | Minor loop gain                      |

| MSC  | Master slave control                 |

| MV   | Medium voltage                       |

| NIR  | Negative incremental resistance      |

| NMP  | Non-minimum phase                    |

| OAC  | Opposing argument criterion          |

| PCB  | Printed circuit board                |

| PLC  | Power line communication             |

| PLS  | Power line signalling                |

| POCC | Point of common coupling             |

| PoL  | Point of load                        |

| PU   | Per unit                             |

| PV   | Photovoltaic                         |

| RES  | Renewable energy source              |

| RESC | Root exponential stability criterion |

| SISO | Single input single output           |

| SoC  | State of charge                      |

| SVC  | Supervisory control                  |

| VLS  | Voltage level signalling             |

| VS   | Voltage source                       |

|      |                                      |

# Symbols

| i <sub>ok</sub> | Output current                                                                                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $v_k'$          | Voltage reference for the controller                                                                                                                                  |

| $v_k^*$         | Nominal voltage                                                                                                                                                       |

| $R_k^{iv}$      | Virtual resistance (or droop coefficient) based on output current                                                                                                     |

| k               | The k-th converter connected in the system.                                                                                                                           |

| $R_k^{Pv}$      | Virtual resistance (or droop coefficient) based on output power                                                                                                       |

| $\Delta v$      | Small variations of bus voltage                                                                                                                                       |

| v               | Bus voltage                                                                                                                                                           |

| $\Delta i$      | Small variations of input current to the constant power load                                                                                                          |

| i               | Input current to the constant power load                                                                                                                              |

| Р               | The power of CPL                                                                                                                                                      |

| $G_{vd}$        | Control to output voltage transfer function of interface converter                                                                                                    |

| Zo              | Output impedance of filter                                                                                                                                            |

| $Z_i$           | Input impedance of interface converter                                                                                                                                |

| $Z_N$           | The input impedance $Z_i(s)$ under the condition that the controller varies the duty cycle to maintain the output voltage variation as much close to zero as possible |

| $Z_D$           | Input impedance $Z_i(s)$ under the condition that duty cycle is equal to zero                                                                                         |

| Т               | Closed loop gain                                                                                                                                                      |

| $T_{MLG}$       | Minor loop gain                                                                                                                                                       |

| G <sub>a</sub>  | Stable line transfer function of source subsystem                                                                                                                     |

| $G_b$            | Stable line transfer function of load subsystem |

|------------------|-------------------------------------------------|

| $V_{1a}$         | Input voltage of source subsystem               |

| $V_{2a}$         | Output voltage of source subsystem              |

| $V_{1b}$         | Input voltage of load subsystem                 |

| $V_{2b}$         | Output voltage of load subsystem                |

| Z <sub>bus</sub> | Total bus impedance                             |

| Voltage reference for the control loop of interface converter 1       |

|-----------------------------------------------------------------------|

| Voltage reference for the control loop of interface converter 2       |

| The nominal voltage (or floating voltage) of interface converter 1    |

| The nominal voltage (or floating voltage) of interface converter 2    |

| The converter output current of interface converter 1                 |

| The converter output current of interface converter 2                 |

| Virtual resistance (or droop coefficient) of interface converter 1    |

| Virtual resistance (or droop coefficient) of interface converter 2    |

| Top floating voltage for the control loop voltage reference           |

| Bottom voltage that allowed to reach with the droop coefficient $R_v$ |

| Maximum allowed output current                                        |

| Maximum output power                                                  |

| Negative current over two converters interactions period              |

| Signal voltage                                                        |

| Power capability of interface converter 2                             |

| Total load power                                                      |

| Dedicated inner loop current reference                                |

| Bus voltage in per unit                                               |

| Signal voltage in per unit                                            |

| Resistance load                                                       |

|                                                                       |

| $f_s$           | Switching frequency of Boost converter                                                             |

|-----------------|----------------------------------------------------------------------------------------------------|

| S               | s domain                                                                                           |

| L               | Converter inductor                                                                                 |

| С               | Converter capacitor                                                                                |

| i <sub>L</sub>  | Inductor current                                                                                   |

| ν               | Output voltage/capacitor voltage                                                                   |

| $v_g$           | Input source voltage                                                                               |

| i <sub>o</sub>  | Output current after capacitor                                                                     |

| d               | Duty cycle                                                                                         |

| d'              | The compensation of duty cycle, which is equal to $1 - d$                                          |

| D               | Steady state duty cycle                                                                            |

| D'              | The compensation of steady state of duty cycle, which is equal to $1 - D$                          |

| R               | Equivalent load resistance                                                                         |

| $G_{vd}$        | Control to output voltage transfer function of converter                                           |

| G <sub>id</sub> | Control to inductor current transfer function of converter                                         |

| $G_{vg}$        | Input voltage to output voltage transfer function of converter/line transfer function of converter |

| $G_{ig}$        | Input voltage to inductor current transfer function of converter                                   |

| $\Delta v$      | Small variations of output voltage                                                                 |

| $\Delta v_c$    | Small variations of inductor current reference in voltage form                                     |

| $\Delta d$      | Small variations of duty cycle                                                                     |

| $i_L^*$         | inductor current reference                                                                         |

| $\Delta i_L^*$  | Small variation of inductor current reference                                                      |

| $\Delta i_L$    | Small variations of inductor current                                                               |

| $R_f$           | Current sampling coefficient/resistor                                                              |

| $G_{\nu c}$     | Transfer function of inductor current reference to output voltage.                                 |

| Κ               | Passive stabiliser gain                                                                            |

| $G_p$           | Passive controller                                                                                 |

| $G'_{\nu c}$         | Compensated transfer function of inductor current reference to output voltage. |

|----------------------|--------------------------------------------------------------------------------|

| $G_{ci}$             | Current loop controller/compensator                                            |

| $G_{cv}$             | Voltage loop controller/compensator                                            |

| $\omega_z/f_z$       | Numerator zero frequency of inner current loop controller                      |

| $\omega_p/f_p$       | Dominator pole frequency of inner current loop controller                      |

| $\omega_{zv}/f_{zv}$ | zero frequency of outer voltage loop controller                                |

| $\delta/f_{pa}$      | Crossover frequency of passive controller                                      |

| $f_N$                | The frequency that enters negative part in $G_{vc}$                            |

| $T_{sp}$             | Sampling time/period                                                           |

| $\overline{V}$       | Steady state value of output voltage                                           |

| $\overline{I_L}$     | Steady state average value of inductor current                                 |

| $Y_T^{P\&D}$     | Terminal admittance with passive and droop controllers              |

|------------------|---------------------------------------------------------------------|

| $Y_T^P$          | Terminal admittance with passive controller                         |

| $Y_T^D$          | Terminal admittance with droop controller                           |

| $Y_T^{dbl}$      | Terminal admittance with initial double loop controllers            |

| $Y_T^{Bat\_CPL}$ | Terminal admittance for battery working constant current/power mode |

| $Y_T^{bus}$      | Total terminal admittance of DC microgrids                          |

| $v_{lim}$        | The voltage that indicates PV step into power limitation mode       |

| $v_{PV}$         | PV input voltage                                                    |

| $i_{PV}$         | PV input current                                                    |

### **Chapter 1 Introduction**

The increasing use of renewable energy sources requires a more effective and efficient power distribution structure. Microgrids, an effective power distribution structure for renewable energy sources, are an active research topic.

In this Chapter, the increased use of renewable energy sources during the past decade (2007-2017) is analysed from both UK and worldwide perspective. AC and DC microgrids are introduced and compared. In particular, the development and application of DC microgrids are illustrated, which is because DC microgrids form the topic of this thesis. Finally, the motivation for and structure of this thesis are stated.

### 1.1 Background

Demand for clean energy is increasing. In addition to creating pollution, fossil fuel energy resources are finite. The use of renewable energy sources (RESs), e.g. wind power, solar power, and hydro power, changes the energy consumption structure globally.

Renewable power generations<sup>1</sup> have grown rapidly in the past decade [1], as shown in Figure 1.1 and Figure 1.2. Europe, North America and the Asia Pacific area make the majority of contributions<sup>2</sup> whereas in areas such as Africa, utilisation of RESs is still quite low. Spare population distribution and inactive economy could be reasons for low utilisation of RESs. Since

<sup>&</sup>lt;sup>1</sup> It mainly refers to wind power and solar power in this thesis.

<sup>&</sup>lt;sup>2</sup> Data based on BP in the reference [1].

2010, IEEE Smart Village [2] has started their efforts on empowering off-grid villages, and acts as the catalyst for socioeconomic and technological change in remote areas of Africa, India, and the South Pacific.

Figure 1.1 Worldwide wind power generations from 2007 to 2017.

Figure 1.2 Worldwide solar power generations from 2007 to 2017.

In the UK, use of RESs is increasing [3] and their electricity contribution has grown rapidly in the past decade, as shown in Figure 1.3<sup>1</sup>. RESs benefit from developments in power electronic

<sup>&</sup>lt;sup>1</sup> Data based on UK energy statistics in reference [3].

technology and from cost reductions in power switching devices, PV generations and wind turbines.

Figure 1.3 Wind and solar energy electricity contribution in UK from 2007 to 2017.

The adoption of distributed RESs requires changes to the conventional power distribution structure, which has only single way power flow. Environmental factors including variation of wind flow and solar irradiance, make power generation by RESs unpredictably intermittent and discontinuous, and thereby influence and stress peak power regulation and management. Typically, RESs are connected to the utility grid through power electronic devices. High frequency harmonics caused by power converters may lower the power quality and interact with filters on the power line so as to threaten the stability of the system.

Driven by above concerns, a new and effective power distribution structure for distributed energy sources is required. Microgrids are proposed in this role.

#### **1.2 Definition and Configuration of Microgrid**

The concept of a microgrid is proposed by Prof. Lasseter [4].

It assumes a cluster of loads and distributed micro-sources operating as a single controllable system that provides both power and heat to its local area.

A typical microgrid is shown in Figure 1.4. The distributed energy sources and loads are connected together through the same power line. The microgrids subsystem can then be connected together through point of common coupling (POCC) [5]. They can be connected with the utility grid through an interface converter/inverter.

Figure 1.4 A typical microgrid configuration.

A typical low voltage microgrid usually contains the following parts [5][6].

• Distributed energy sources

Distributed energy sources (DESs) may include renewable energy sources, such as solar power, wind power, hydro power, biomass power (such as fuel cell), or thermal power.

• Energy storage

Energy storage (ES) devices include electrochemical energy storage devices, e.g. lead-acid batteries, lithium-ion batteries, electrical energy storage devices, e.g. supercapacitors and mechanical energy storage devices, e.g. compressed air and flywheels.

• Interface to utility grid

The utility grid refers to the mains grid. Microgrid system can operate at the grid connected mode and off-grid mode. Off-grid mode is also called isolated/islanded mode [7].

Power load

Power loads can be uncontrollable, e.g. residential (home appliances) or controllable, which are able to participate in the power management in microgrids, e.g. electrical vehicles (EVs).

#### **1.2.1 AC and DC microgrids**

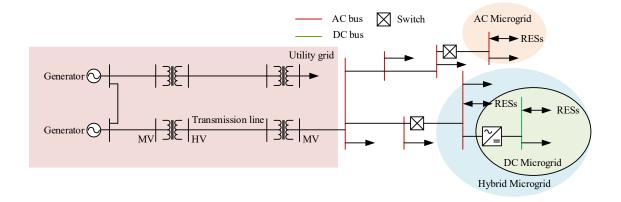

The common power bus in a microgrid may be either AC or DC [8]. The relationship of microgrids with conventional utility grid is shown in Figure 1.5.

Figure 1.5 Power distribution structure.

Utility grid is still the main composition of current power distribution architecture. Microgrids are used to work as the sub-stream of power distribution to manage the RESs and provide power to the local loads. AC and DC microgrids can be integrated to form hybrid microgrids. An interface converter is required to link the AC and DC buses. This interface converter can naturally link or isolate the DC microgrid without additional switch/breaker.

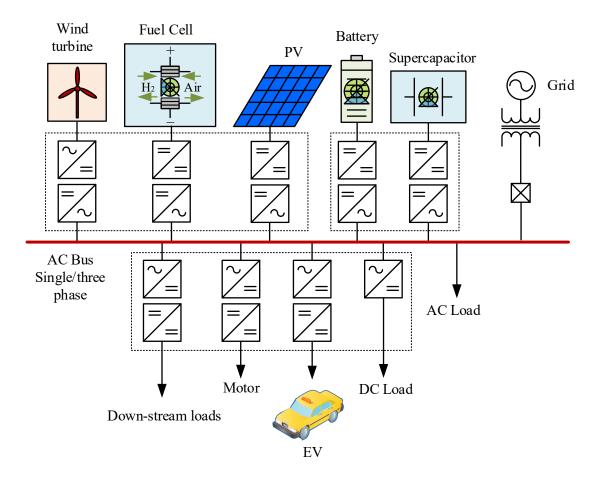

In past decades, AC microgrids have been widely investigated to line up with the existing power system infrastructure. A typical AC microgrid system is shown in Figure 1.6. The RESs are all connected to the common AC bus through power electronics converters, which enable the stable coupling with AC networks [9]. AC loads can be directly connected to the AC bus while AC to DC converters are needed to power the DC loads.

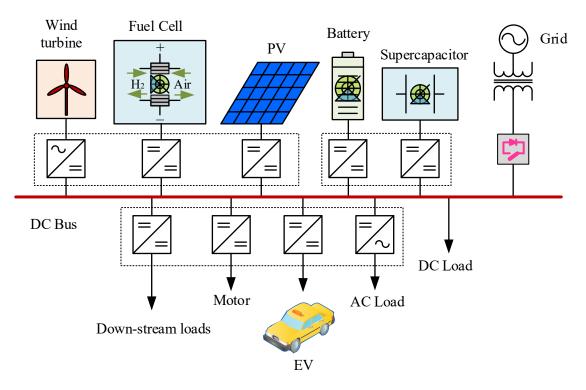

However, many distributed sources and energy storages, such as PV generations, battery banks, supercapacitors, etc., are naturally based on DC. They need additional DC to AC inverters to regulate their voltage to AC so that they can be connected to the common AC bus. Even for the wind turbines, although they can generate AC output, their frequency varies and is not the same as the utility grid. Consequently, they still need to be converted to DC first and then connected to a common AC bus through inverters. Therefore, configuring a DC bus can save the interface

converters cost and reduce the complexity of the system. Besides, it has no frequency in DC system, which enables DC microgrids free from complex control of frequency and synchronisations. A typical DC microgrid configuration is shown in Figure 1.7. DC loads can be directly connected to the DC bus. An interface inverter is required to link the DC microgrid with the conventional grid.

Compared with AC microgrid, the advantages of DC microgrid are summarised as follows [9][10]:

- Higher efficiency of energy utilization due to the reduction of converters;

- No reactive power, harmonics and synchronisations;

- Easier controls and integration of various DC RESs.

Figure 1.6 A typical AC microgrid configuration.

Figure 1.7 A typical DC microgrid configuration.

#### **1.2.2 DC Microgrids**— Applications and State of the Art

Much research has been carried out in DC microgrids [11]. In the USA, the concept of Future Renewable Electrical Energy Delivery and Management (FREEDM) [12][13][14] has been proposed for future smart power distribution. In this framework, DC microgrids are an important part.

Many DC microgrid demonstration sites have been developed, e.g. the DC building at Xiamen University, China [15], the intelligent DC microgrid living lab in Denmark [16], Nushima island DC microgrid in Japan [17], the DC microgrid library conducted by Bath University in UK [18], and Burlington DC Microgrid in Canada [19]. Reference [11] provides further examples of DC microgrids. These applications of DC microgrids mainly focus on industrial buildings and remote island electrification. DC microgrids also have application on ships [20][21], aircraft [22] and in data centres [23].

DC microgrid research involves many topics, including control, stability analysis, protection, system structure and communication protocols. The research reported in this thesis focuses on the study of control strategies and stability issues.

DC microgrids commonly use a hierarchical control scheme. A typical hierarchical control scheme can be seen in chapter 2, section 2.1.2. The lower layers are responsible for the dynamic control of interface converters; the upper layers are responsible for the power management/trade with communication infrastructures. The control of DC microgrids tends to realise intelligent and automatic power distribution, which also corresponds to the future trend of smart grids. Configuring DC microgrids with communications infrastructure can make the power management easier, but complex control structures add to the installation costs of DC microgrids. This is difficult for remote area electrification, especially in developing countries, which is one of important applications of DC microgrids. Therefore, reducing the cost of DC microgrids is important for their wider application. One way to reduce the cost is to remove the upper layer communication infrastructure. As a substitute, low bandwidth communications or spare

communications are used for the power management. For cost-effective considerations, power line communications (PLC) are proposed for the communications between the interface converters. In this case, additional external communication links are no longer needed. The signal can be delivered through the power line. However, dedicated signal modulation and demodulation circuits are still required for conventional PLC methods. The advantages and disadvantages of PLC will be discussed in Chapter 2.

Another option is to remove the communication infrastructure and configure the DC microgrids with original droop control or DC bus signalling. The system will then become load adaptive. However, load adaptive methods lack consideration of the characteristics of distributed sources, e.g. battery banks, and depletion and overcharging will shorten battery life spans. Therefore, it is still worthwhile to investigate a method to actively regulate the distributed sources in the absence of communication infrastructures for low cost DC microgrid applications.

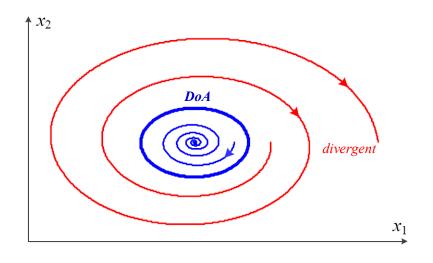

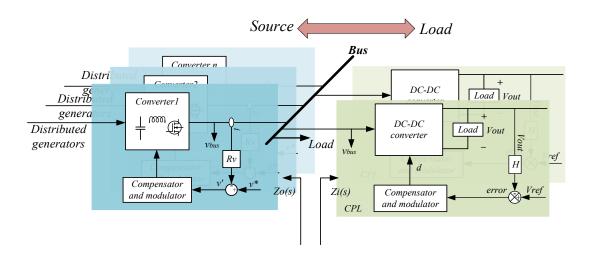

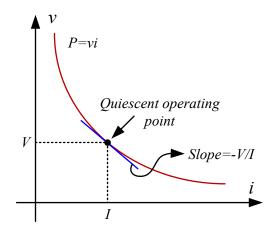

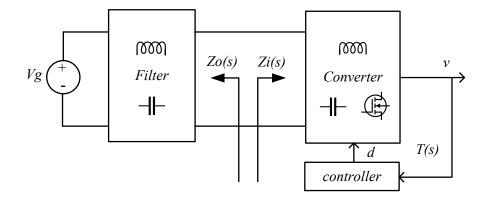

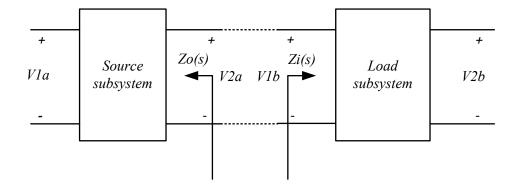

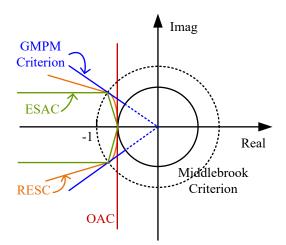

Stability is another essential requirement for DC microgrid operations. Stability issues in DC microgrids are about maintaining the bus voltage stable and avoiding black-out. They will be specifically discussed in chapter 2. One potential cause of instability is the interaction of cascaded converters. A load converter (or point of load converter) acts as a constant power load and will introduce negative incremental resistance. It can interact with the former converters or filters to form a negative oscillator. Two methods of stability analysis are small signal linear analysis and large signal nonlinear analysis. Small signal linear methods are based on Middlebrook's minor loop gain theorem and provide design guidance for cascaded converters. The idea of small signal analysis is to linearize a nonlinear system around its quiescent operating point. Large signal nonlinear analysis concerns an area of convergence that is also called domain/area of attraction. The system will always tend to be stable inside that domain. However, nonlinear analysis is complex and requires massive calculations. Besides, it is difficult to guide the conventional controller design and line up with the industrial applications. The author chooses the small signal linear method as the main analysis method throughout this thesis.

Apart from the instability caused by the point of load converters, the source side converters can also interact with each other. Introducing droop control will impact the quiescent operating point and have the potential to destabilise the system. In addition, interface converter described by non-minimum phase transfer functions have the potential to be unstable. Conventional methods to reduce the impact of non-minimum phase interface converters from a control perspective are mainly based on the parasitic resistance of terminal output capacitor while the resistance introduces the voltage ripples. Therefore, it needs proper control methods to deal with the non-minimum phase and adjust the complex operation conditions in DC microgrids.

#### **1.3 Objectives and Structure of Thesis**

Motivated by the requirement of cost-effective low voltage DC microgrids, this thesis proposes a novel hierarchical control scheme for the operation of a DC microgrid, and provides solutions to the following problems in a DC microgrid system:

- Coordination of distributed sources in a DC microgrid without additional communication infrastructure;

- Mitigation of the impact of non-minimum phase converter transfer functions to ensure the stable and reliable operation of the system;

- Investigation of interactions between interface converters in DC microgrids and provide stable operation suggestions.

- Solve the power imbalance that could occur in the islanded mode when PV generations supply surplus power.

Each chapter includes a brief introduction and a summary. The structure of this thesis is organised as follows,

In Chapter 2, control strategies/methods and stability assessments of DC microgrids are reviewed. Control methods are reviewed under a hierarchical control scheme, in which the details of droop control, DC bus signalling (DBS) and power line communication (PLC) are analysed.

Other control strategies on top layer control for power management are reviewed as well, such as multi-agent control. As for the stability evaluations, the linear analysis will be the main composition of this thesis for the consideration of controller design and modification. The instability factors are discussed from the source to load interactions and source to source interactions under a single DC bus microgrid. The criteria used for evaluating the system stability are reviewed. Finally, previous stabilization methods in DC microgrids are reviewed and classified.

In Chapter 3, the design of a DC microgrid experimental system is described. This system contains four interface converters. Bidirectional boost converters are used as interface converters. Details of each interface converter are provided.

In Chapter 4, a dual-window DC bus interaction (DBI) method for low-bandwidth communication is proposed. The mechanism and principle of this method are explained. Signal series design procedures based on the mechanism of the proposed method are provided and possible drawbacks are discussed. Finally, the feasibility of the proposed method is validated experimentally in a simple case study.

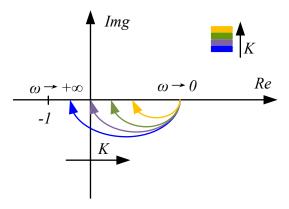

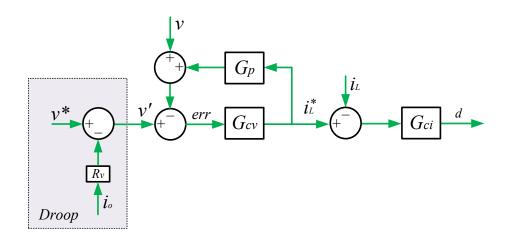

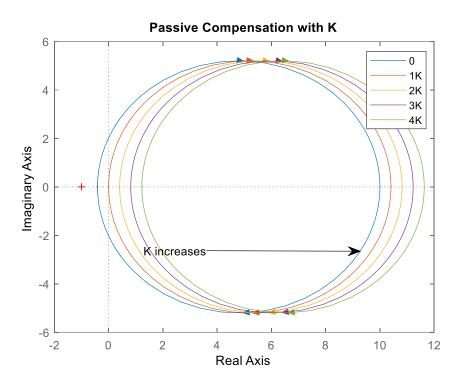

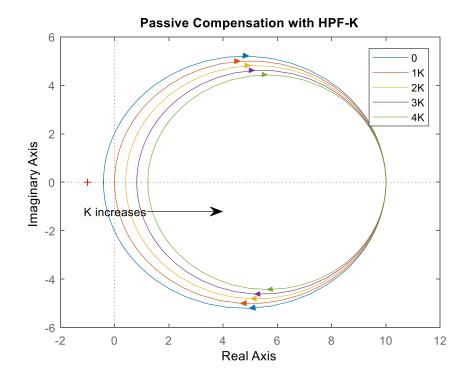

In Chapter 5, a passive stabiliser for compensating non-minimum phase interface converters is proposed. The non-minimum phase makes the outer loop voltage transfer function in the Nyquist plot have the potential to encircle (-1, j0), which results in instability. The passive theory related to this work is briefly introduced. The detailed analysis and design process of passive stabiliser are provided. Finally, the effectiveness of proposed passive stabiliser is experimentally validated.

In Chapter 6, the proposed dual-window DC bus interacting method in Chapter 4 and passive stabiliser in Chapter 5 are constructed under a hierarchical control scheme for household DC microgrid applications. The stability and interactions of each interface converters are evaluated from terminal admittance based on the minor loop gain analysis. The signal series protocol is designed based on assumed rules. The system state machine is illustrated. Finally, the on-grid/off-grid situations and seamless transfer between them are experimentally validated. Besides, for a

special case in off-grid mode, the surplus power from PV generations are limited based on a modified maximum power point tracking (MPPT) algorithm.

In Chapter 7, conclusions are made, and future work is suggested. The contributions of this thesis to the literature are summarised and author's publications are listed.

An appendix provides PCB design of interface converter and equations' calculations and manipulations involved in Chapter 5 and 6.

### **Chapter 2 Literature Review**

Control strategies and stability issues are the two main topics throughout this thesis. In this chapter, previous studies related to control methods/strategies and stability in DC microgrids are reviewed. The control strategies/methods are reviewed based on their functions and roles in a hierarchical control scheme. This chapter focuses on the review of bottom layer control methods, such as droop control, adaptive droop control, and DC bus signalling, etc. The advantages and disadvantages of each control method will be explored. The DC microgrid stability issues are introduced from three aspects. The first is the instability factors in DC microgrids, such as constant power load. The second is the small signal linear stability criteria for cascaded converters in DC microgrids. Their originality, development and variations are reviewed and illustrated. The third is stabilising methods for DC microgrids. Those methods are reviewed, compared and classified. At the end of this chapter, identified problems in this literature review are summarised.

### 2.1 Control Strategies in DC Microgrids

Control methods are essential for the operation of a DC microgrid. There are many reported DC microgrid control concepts, such as hierarchical control, supervisory control, centralised control, distributed control, etc. Some of them have the same objectives but are used in different applications; some of them are used in subordination relationships. Before reviewing the specified control methods, it is necessary to explain these control concepts first.

#### 2.1.1 Control Concepts in DC Microgrids

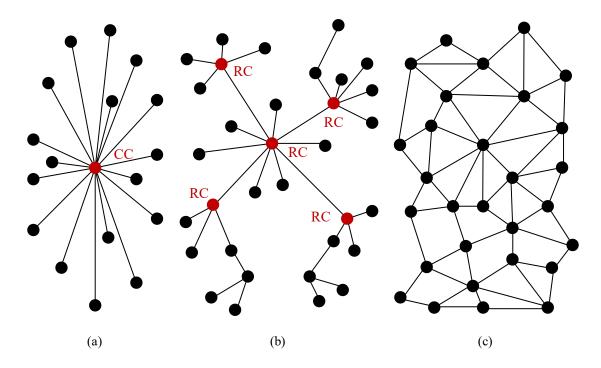

Three concepts are discussed in many papers: centralised control, decentralised control and distributed control. These concepts come from communication networks [24]. Therefore, when they are applied to DC microgrids, the DC microgrid communication infrastructures need to be considered. The control concepts are illustrated as follows.

#### Centralised control

Centralised control is based on a central controller (CC), which is sketched in Figure 2.1(a). It is easy to implement this control network. However, this network is vulnerable in that the failure of the CC will lead to the collapse of the whole system. It is also called single point of failure.

Decentralised control

Decentralised control avoids the single point of failure problem of centralised control. It can be regarded as the expansion of centralised control, as shown in Figure 2.1(b). However, the destruction of the regional controller (RC) will lead to regional collapse.

#### • Distributed control

Distributed control is a relatively reliable network. Every single point is connected to its neighbours. Single point of failure will not impact the rest of the individuals in the system as is shown in Figure 2.1 (c). Therefore, for any complex network with the goal of high reliability, it is advantageous to make the system more 'distributed'.

In DC microgrids, some control methods are non-communication based. For example, conventional droop control does not need any additional communication links if the distributed energy sources work under droop coefficient-based power sharing states, yet they are individually reliable. This means that the system can still work well regardless of any single module failure. Therefore, the conventional droop control is a 'distributed' control method.

Figure 2.1 Diagram [24] of centralised (a), decentralised (b) and distributed (c) control networks.

# **2.1.2 Hierarchical Control Scheme**

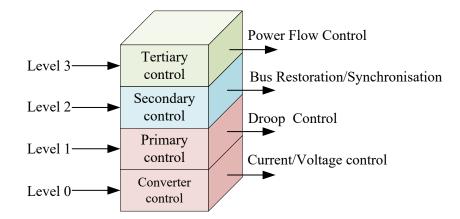

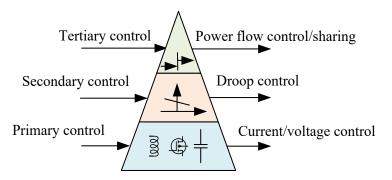

Hierarchical control scheme<sup>1</sup> has been widely applied in microgrids. Paper [8] adjusts the ISA-95 standard [25], which is for enterprise-control systems integration, to microgrids as four control levels or layers, which are shown in Figure 2.2. It has:

- converter control, such as voltage control, current control and double loop control, etc.;

- primary droop control;

- secondary DC bus restorations;

- tertiary power flow or power management control.

Secondary and tertiary control layers need to use low bandwidth communication or sparse communication links.

<sup>&</sup>lt;sup>1</sup> Control scheme here refers to the control configurations that the DC microgrid system is based on. For example, hierarchical control scheme is the most widely applied control scheme in both AC and DC microgrids, and has different control layers.

Figure 2.2 Hierarchical control scheme of interface converters in DC microgrids.

The hierarchical control scheme has different types of configuration. For example, a hierarchical control with upper layer cyber networks for microgrid clusters is proposed in paper [26]. Adding advanced communication infrastructure (cyber networks) to the microgrid can make the system operate more intelligently than the conventional distributed system.

The DC microgrid system with hierarchical control scheme can be regarded as either distributed control or centralised control, which is dependent on the configurations of communication infrastructures. The upper layer<sup>1</sup> communications can update the parameters for the bottom layers according to user demands, such as economy, environment, etc. Among the upper control layers, many control strategies have been proposed, such as master-slave control (MSC), supervisory control (SVC), and multi-agent control (MAC) for power sharing and energy management.

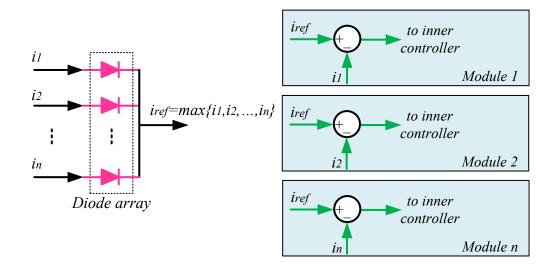

Master-slave control (MSC) [27][28][29] is used for power sharing between parallel connected converters. The master module provides the current reference for the rest of the slave modules. It has advantages over small-scale distributed power systems (DPS) based on its convenience, cost-effectiveness and easy implementation. However, this method suffers from the problem of single point of failure just as the centralised networks. A method [28] has been proposed to avoid single point of failure. An additional diode array is added to controller for selecting a master module whose output current modules is maximum, which is shown in Figure

<sup>&</sup>lt;sup>1</sup> The upper layer control refers to controls that do not interfere with converter dynamics; the bottom layer control refers to the dynamic control of interface converters.

2.3. The maximum current will eliminate the corresponding current reference loop; then the inner loop controller will start the voltage regulation. Therefore, even if the master module collapses, the next maximum output current module will automatically work as the master module. This makes the system more 'distributed' than the conventional MSC.

Figure 2.3 Modified MSC with diode array.

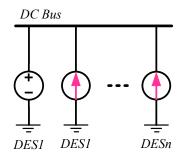

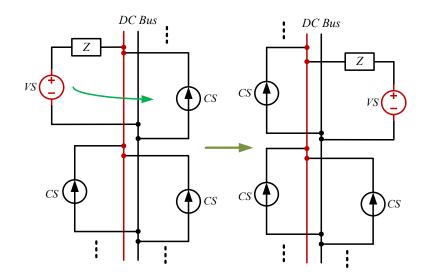

The later development of MSC in DC microgrids comes from an idea in conventional MSC. The master is responsible for maintaining the DC bus voltage, and the slave modules are responsible for the power sharing [30]. Since it must have an interface converter to work as a voltage source to maintain the DC bus voltage, it is usually assigned to the grid connected converter. The master module is operated as the voltage source, and the slave modules are operated as current sources, as shown in Figure 2.4. This control scheme leads to accurate power sharing compared with droop control, which will be further discussed in the next section.

Figure 2.4 Master-slave control for distributed power systems.

Supervisory control (SVC) [31] is applied in the upper layer control of a microgrid system where the system parameter information will be processed and data exchange will be carried out. It provides the optimisation control supervisions to the lower control layers. A mixed concept of supervisory control and multi-agent control methods is proposed in paper [32]. Multi-agent control (MAC) [33] uses peer to peer (P2P) control for the power management of microgrids. The communication links lie between each neighbourhood; therefore, the system is configured in a 'distributed' way. The MAC control [34][35][36][37] uses sparse communication links/networks to regulate the energy storage system in microgrids, which makes the system networks reliable.

The upper layer controls mainly target the energy management in DC microgrids. Their optimisation objectives are based on external factors, while the most important part involving the power electronics control and system performance is made up of the bottom layer controls, such as voltage/current control, droop control and DC bus voltage regulations, etc. Applying communication infrastructure to DC microgrids adds to cost and complexity. Therefore, many methods are proposed for the power management of DC microgrids without additional communication infrastructures, such as DC bus signalling and power line communications.

The next three sections will review the control methods applied in DC microgrids without additional communication infrastructure. Their working mechanism will be introduced, and their applications and roles in a hierarchical control scheme will be set forth.

#### 2.1.3 Droop Control and Variations

Droop control, also known as adaptive voltage positioning [38][39], is one of the most popular control methods applied in microgrids. Unlike the AC system[40], there is no frequency in the DC system. The voltage droop in DC microgrids is introduced by output current multiplying virtual resistances (or output power multiplying droop terms). As for an ideal tightly regulated interface converter, the output impedance tends to be zero. This means that when there are two distributed energy sources are connected in parallel (as is shown in Figure 2.5), there is a large

circulating current between them if a tiny terminal voltage difference exists. Therefore, virtual resistance is introduced to avoid this situation.

Figure 2.5 Equivalent circuit of two paralleled distributed energy sources.

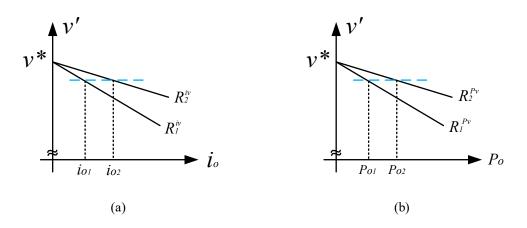

A typical droop curve combination for two parallel-connected interface converters is shown in Figure 2.6, and they can be written as equation (2-1) and equation (2-2).

$$v'_{k} = v^{*}_{k} - i_{ok} R^{iv}_{k} \tag{2-1}$$

$$v'_{k} = v^{*}_{k} - P_{ok} R^{Pv}_{k} \tag{2-2}$$

where  $v_k^*$  is the nominal voltage;  $v_k'$  is the voltage reference for the controller;  $i_{ok}$  is the output current and  $P_{ok}$  is the output power;  $R_k^{iv}$  is the virtual resistance (or droop coefficient) for output current;  $R_k^{Pv}$  is the power droop factor and output power based droop control; k is the k-th converter connected in the system.

Figure 2.6 Droop curves in DC microgrids; (a) output current based droop control; (b) output power based droop control.

When multiple distributed energy sources are connected to the common DC bus, the power sharing between them thus can be adjusted by virtual resistances. In other words, the virtual

resistances are responsible for the power sharing between these distributed sources. Noticing the droop curves in Figure 2.6, these parameters can be varied by upper control layers with communication infrastructure, such as  $R_k^{iv}$  and  $v_k^*$ . Based on this idea, many adaptive droop control methods [41][42][43] are proposed to manage the power distributions in DC microgrids.

However, droop control has several drawbacks. First, the voltage droop introduced by droop control is not desired in some applications requiring constant bus voltage. Second, the values of the droop coefficient affect the accuracy of the power/current sharing. Ideally, the power sharing can be proportionally achieved using virtual resistance. However, for the applications with long power lines, the line resistance cannot be neglected, and this will degrade the accuracy of the power sharing.

Based on the above analysis, much research work has been done to overcome these drawbacks.

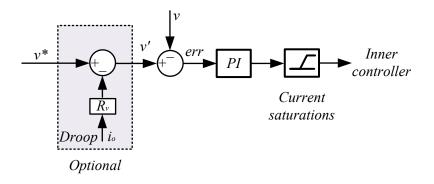

First of all, paper [44] uses a low bandwidth communication (LBC) to realise the DC bus voltage restoration by adding the additional values to the voltage reference, as shown in Figure 2.7. It also points out that a large droop coefficient can provide more accurate current sharing. However, a larger voltage droop will be introduced as a trade-off. Large voltage droop makes shift of quiescent operating point, and system stability might be affected. Related work using low bandwidth communication can be found in papers [45][46][47]. Paper [48] introduces the neighbour terminal voltage to the local controller to achieve DC bus restoration.

Figure 2.7 Bus restoration with low bandwidth communications.

Secondly, regarding the improvement of current/power sharing accuracy, paper [49] proposes a method to automatically adjust the droop coefficient according to the load such that when the load is large, accurate current sharing can be achieved. Paper [50] addresses the circulating current sharing issues of two paralleled interface converters by introducing droop index control. Similarly, a droop index method based on the PV power was proposed in paper [51] to achieve accurate current sharing. Paper [52] introduces secondary control to remove the voltage droop and achieve accurate current sharing by voltage shift and slope adjustment.

Taking line resistance into consideration, paper [53] proposes a droop-based control strategy to achieve accurate current sharing for different working modes, such grid-connected mode and off-grid mode. In addition, papers [54][55] implement droop control under hierarchical control schemes in DC microgrids, in which the proportional current sharing was achieved through communications, and line impedance is no longer a problem. Apart from proportional current sharing, average current sharing is applied in [56]. In addition, some other methods [57] with nonlinear droop coefficients are proposed for meeting power regulation requirements. The fuzzy logic controllers are also applied to achieve accurate current/power sharing in papers [58][59][60].

To sum up, conventional droop control cannot actively optimise current sharing between distributed sources; it only provides a mechanism to achieve power sharing. Much research work has been conducted to modify the droop control method. For energy management, upper layer communication or signalling is required.

Droop control has advantages in regulating energy storage systems, such as battery banks or supercapacitors. The virtual resistance can be adjusted by the battery state of charge (SoC). Paper [61] proposes a double-quadrant SoC based droop control method to regulate battery power in the case of overuse. Similar SoC based droop control methods have also been proposed in papers [31][60][62] for coordinating multiple battery banks, multiple supercapacitors [63][64], and hybrid energy storage [65][66]. A frequency-based droop control for hybrid energy storage systems with function separation is proposed in paper [67], so that the energy storage system can dynamically respond to various situations.

After reviewing the above previous research work, it can be concluded that droop control is applied in the bottom layer control from a hierarchical control scheme perspective, which is directly related to converter dynamics.

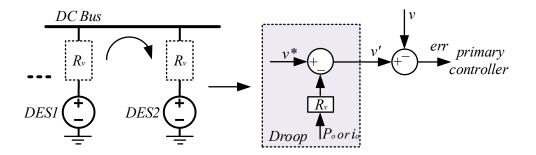

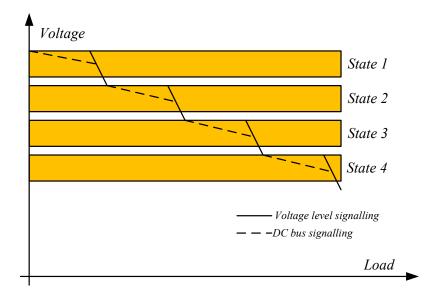

# 2.1.4 DC Bus Signalling

DC bus signalling (DBS) [69][70] is a method that uses different DC bus voltage levels to achieve signalling between distributed sources. This method is developed from voltage level signalling [71]. Voltage level signalling (VLS) is a discontinuous form of voltage droop that allows sources to be scheduled in a certain working voltage window. VLS method is different from the purpose of voltage droop, which is to provide power sharing with minimal voltage deviations on the common DC bus. Large voltage deviations are allowed in VLS since the system is designed to operate within a specified voltage window.

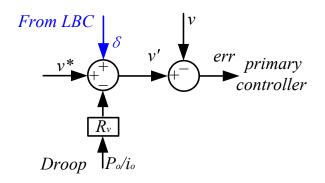

The mechanism of VLS method is to utilise the inner current loop saturation to realise the voltage droop. When the system load increases, the distributed source will step into the current saturation mode, so the DC bus voltage decreases as the load increases until it reaches the next working voltage window to wake up another distributed source to supply the load. This mechanism is similar to MSC shown in Figure 2.4. DC bus voltage stays constant until the inner current loop reaches the saturation limit, which is shown as the solid line in Figure 2.8. However, VLS has its limitations. When new distributed sources are connected to the system, new working voltage windows need to be assigned for their operations. For a system with many distributed sources, the number of working voltage windows will be large.

VLS becomes DBS method by adding the droop loop to each working voltage window, which is shown as the dashed line in Figure 2.8. In this case, when new distributed sources are connected, they can work under the previous working voltage window by droop control with power sharing. Therefore, the power from the original distributed source can be shared with new distributed sources. Meanwhile, the number of working voltage windows can be reduced.

Figure 2.8 Diagram for voltage level signalling and DC bus signalling control methods.

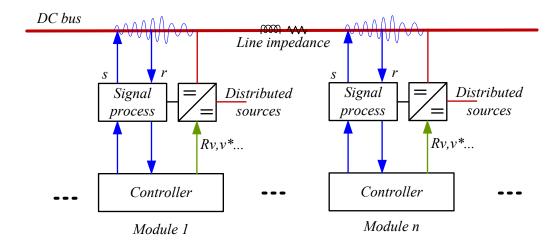

Based on the working mechanisms illustrated above, the control block diagram of the DBS method is shown in Figure 2.9. The advantage of the DBS control method is that it can regulate the distributed source in the DC system automatically without external communication infrastructure. However, the signalling is load-dependent. In other words, the load's power consumption will determine the system's working state.

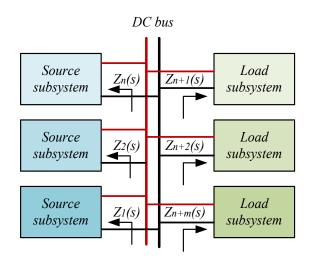

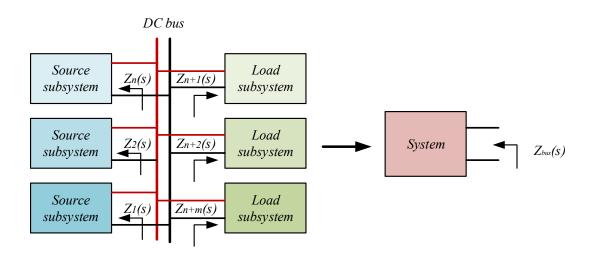

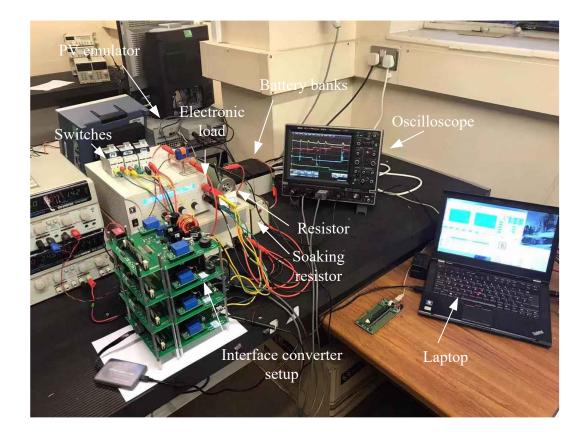

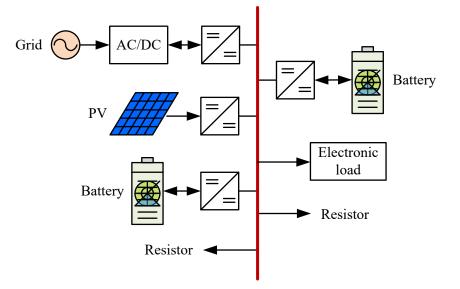

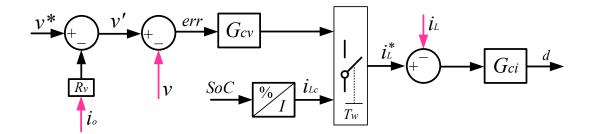

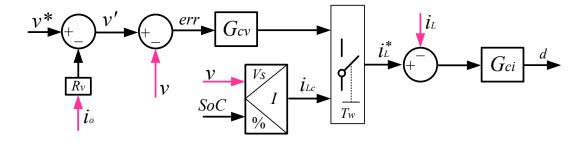

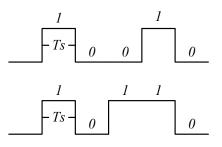

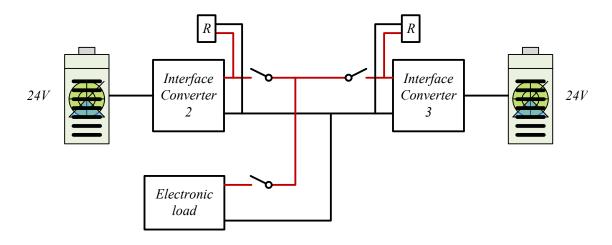

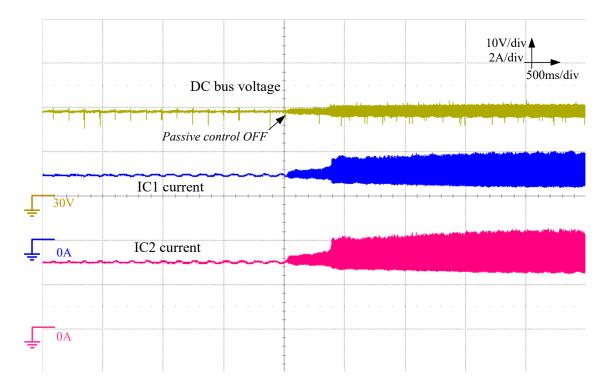

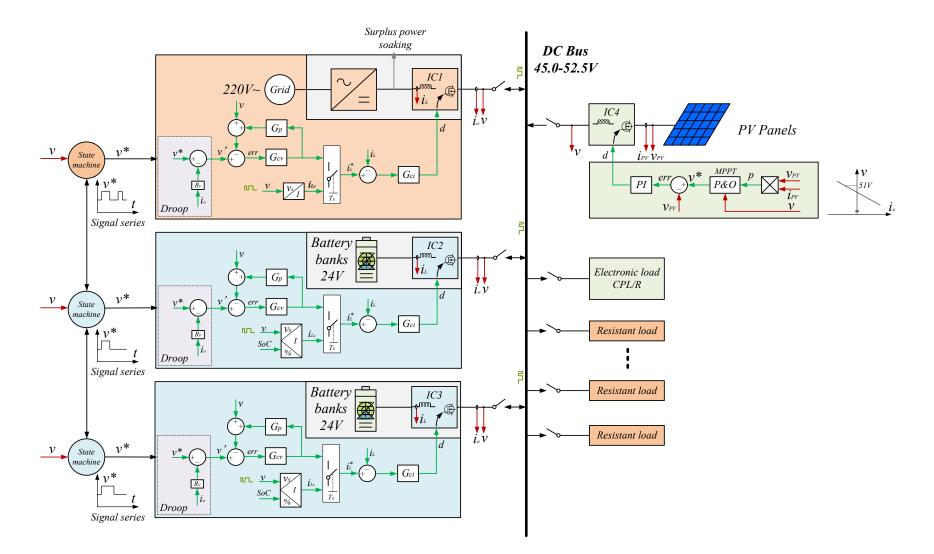

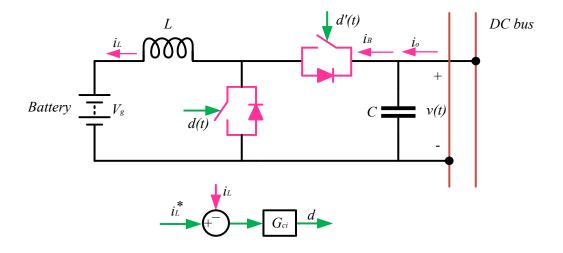

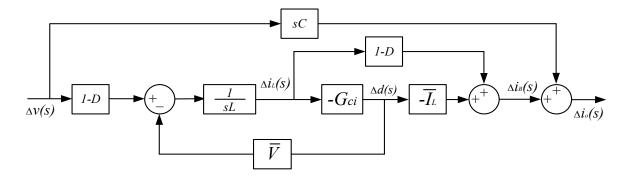

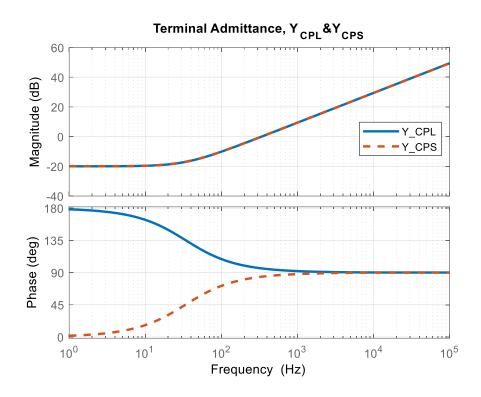

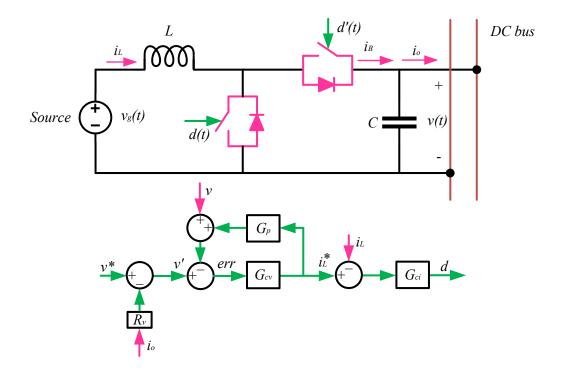

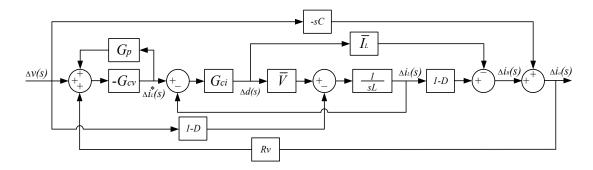

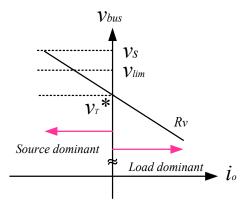

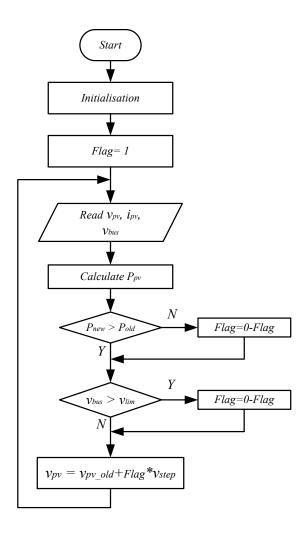

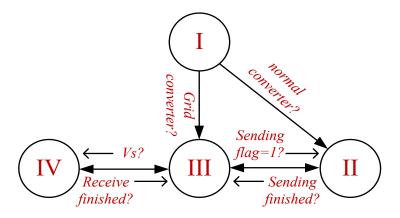

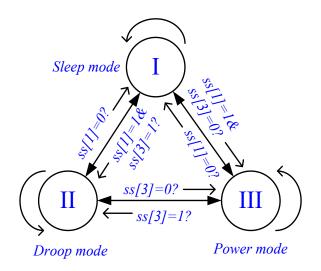

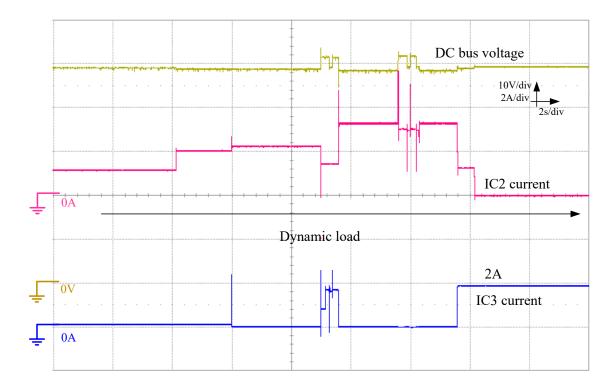

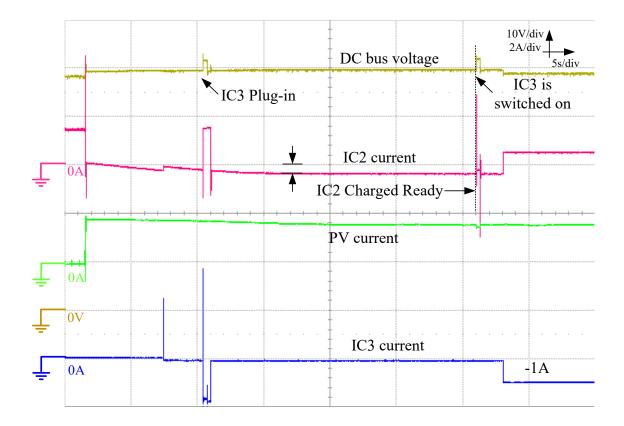

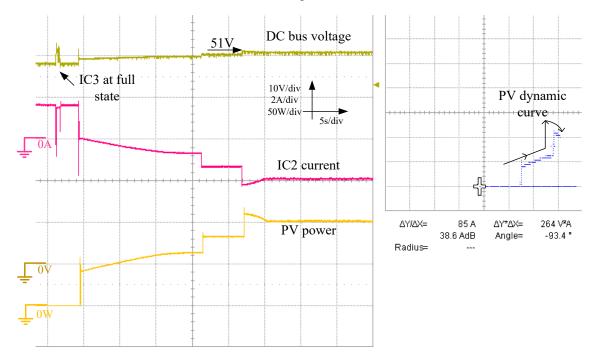

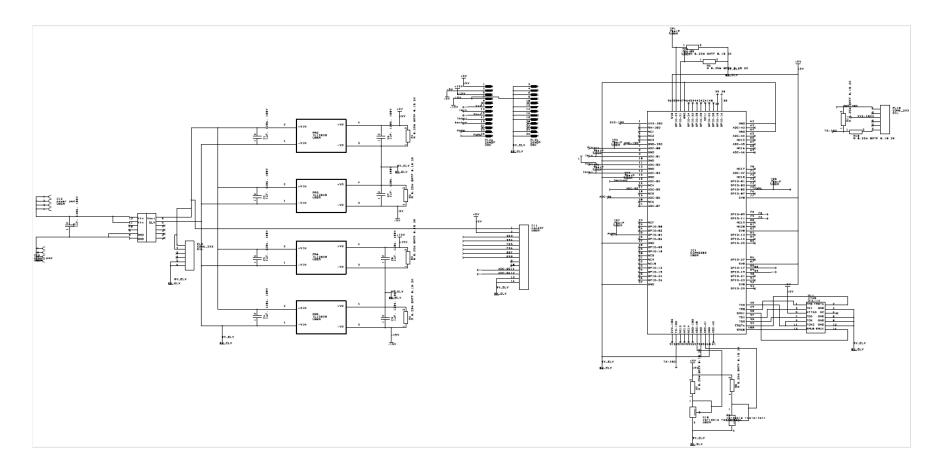

Figure 2.9 Control blocks for DBS method.