# Demonstration and Characterisation of a non-inverting Alloptical read/write regenerative memory

N.C. Johnson, J.A. Harrison, K.J. Blow

Aston University, Photonics Research Group, Birmingham, UK, B4 7ET.

**Abstract:** An all-optical regenerative memory device using a single loop mirror and a semiconductor optical amplifier is experimentally demonstrated. This configuration has potential for a low power all-optical stable memory device with non-inverting characteristics where packets are stored through continuously injecting the regenerated data back into the loop.

**Keywords:** Loop Mirror, All-Optical Memory, Optical Regeneration, Semiconductor Optical Amplifier, SOA, Terahertz Optical Asymmetric Demultiplexor, TOAD.

### Introduction

The capacity of optical communication links has grown significantly in recent years and it is possible to transmit data much faster than it is possible to process it. This is because of the relatively slow electronic technology often found in optical networks. Advances in all-optical processing techniques have been made including components such as all-optical pre- and post-processing buffers [1-3]. Currently there is no all-optical alternative to electronic Random Access Memory (RAM) and so for solving conflicts, such as destination contention and pre-processing buffering, other methods need to be found.

The simplest way to store an optical signal is to propagate it through a medium, such as a length of fibre, where the storage period is defined by the propagation time. However, the length of the storage time is fixed to a (usually) small number of discrete values depending upon the position of predetermined taps (an example of this would be feed forward based packet switching [4]). An improvement over such a static situation can be obtained by incorporating switching in a series of delay lines so that the number of switches is logarithmically related to the number of possible delays. Another way to combat this issue would be to use a feedback architecture [5] where the output of a delay fibre is directed back into the input creating a recirculating loop. The signal thus propagates around the loop in a pulsepreserving manner until the data is required. The limit with all pulsepreserving techniques is the capability to store data for extended periods of time where various physical effects, such as chromatic dispersion and attenuation, start to degrade the signal as they would with long transmission distances. This degradation can be avoided by periodically regenerating the stored data onto fresh pulses [1].

It has been previously demonstrated that a memory device can be created using an inverting shift register [6], this technique has the advantage that it

utilises a single loop mirror as an optical switch, which copies the data stored onto fresh pulses after a period of time and is thus regenerative. However, when data is stored in the feedback loop, the data is inverted during each regeneration cycle, therefore the data can only be read for one cycle out of every two. In this paper we demonstrate a device that has all the advantages of the shift register but, because the data is non-inverting, the time it takes for the data to be accessed once it has been requested, known as the access time, is halved. To promote understanding a detailed characterisation of the operating regimes of such an optical memory is also included.

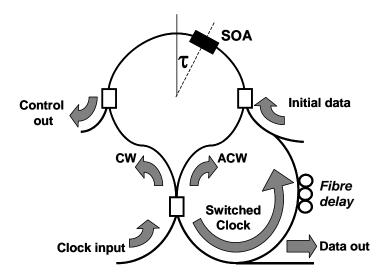

Figure 1 Schematic diagram of the optical memory. The clock input is used to inject a continuous supply of fresh pulses to the optical switch. The Initial data input is used to load the memory.

## **Experiment**

Regeneration is achieved using a Terahertz Optical Asymmetric Demultiplexer (TOAD) [7, 8] which is based on a Sagnac loop mirror [8] with an SOA providing the non-linear element. Figure 1 shows a schematic diagram of the full non-inverting optical memory consisting of a TOAD and fibre delay (feedback loop). Light injected at the clock input will enter the loop coupler and separate into two signals propagating around the loop simultaneously in a clockwise (CW) and anticlockwise (ACW) direction until they re-enter the loop coupler. On re-entering the coupler the two pulses will re-combine, constructively in the case of perfect symmetry, back into a single pulse, which will exit through the port in which it originally entered. However, a  $\pi$  phase shift difference between the two propagating signals re-entering the coupler will cause the light to exit through the opposite port to the clock input. labelled "switched clock" in Figure 1. The phase shifts applied to the counterpropagating pulses depend on the population inversion of the SOA, as this determines the devices refractive index, as well as the position of the SOA in the loop. A control pulse injected into the loop is used to create a time dependant inversion in the SOA. Since the propagating pulse signals arrive at different times they will see different phase shifts and hence the resultant output clock pulse will switch from the reflected clock input port to the transmitted data output port. The SOA offset from the centre of the loop

determines the differential arrival times of the signal pulses and hence the switching window.

During the operation of the device a constant supply of clock pulses is available at the clock input, these pulses enter the loop and are all initially reflected back out of the clock input until data is required to be stored. To store data in the memory a data packet is injected into the control port (marked "initial data" in Figure 1) of the TOAD just once. The data packet pulses act as control pulses and switch out the clock pulses into the feedback loop thereby mapping the data onto the new clock pulses. The switched out clock pulses then re-enter the TOAD but this time through the control port, as control pulses, where they switch out the next set of fresh clock pulses, which are then re-fed back into the feedback loop continuing the cycle. The data pulses are therefore regenerated and the pulses from the previous cycle are discarded. It is possible to clear the stored data by blocking the feedback loop, preventing any switched clock pulses from entering the control port, and hence, breaking the cycle. Having successfully stored the data it is possible to read multiple copies of the data without affecting the data stored in the memory, as the data is continuously present at the data output port.

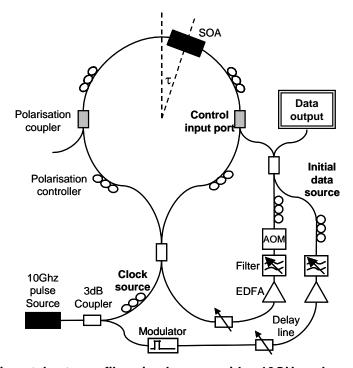

Figure 2 Experimental setup, a fibre ring laser provides 10GHz pulse streams for both the clock and the original data thus operating at the same wavelength. Before fresh data is stored the device is reset by disconnecting the feedback using an Acousto-Optical Modulator (AOM). The data output is located at the end of the feedback just before the data re-enters the TOAD.

The experimental setup is shown in Figure 2, a single fibre ring laser provided the source for both the clock and initial data pulses (10Gb/s RZ pulses with a FWHM of 14ps at a wavelength of 1550nm). After the pulse source a 3dB splitter separated the signal into two streams, one is used to provide the initial data and the other provided the clock pulses. The initial data packet was

constructed by modulating the pulse source using a Lithium Niobate (LiNbO<sub>3</sub>) modulator. This packet was then amplified and filtered before being injected into the loop through the control port (this happens only once to a given packet). In the scheme demonstrated here the clock and the data were at the same wavelength, it should be noted that the device would also work as a wavelength converter by having different clock and initial data wavelengths [9].

It is essential that control pulses be removed from the system, once they have switched out the clock pulses to become the next copy of the stored packet, as redundant pulses would cause the stored data to become corrupted. The control pulses were therefore removed with the polarization coupler after they had transited through the SOA. The reset function was achieved by disconnecting the feedback using an Acousto Optic Modulator (AOM) for a time period matching the length of the loop. The length of the feedback loop (determined by the time taken for a switched out clock pulse to travel from the SOA around the feedback loop and back to the SOA as a control pulse) determines the maximum size of the packet that can be stored. Normally the maximum size would be set slightly lower than this value to allow a guard band between packets. The time taken for one circulation in the experiment described here was  $5.5\mu s$  and so the size of the stored packet must be smaller than this (55kbits at 10GHz).

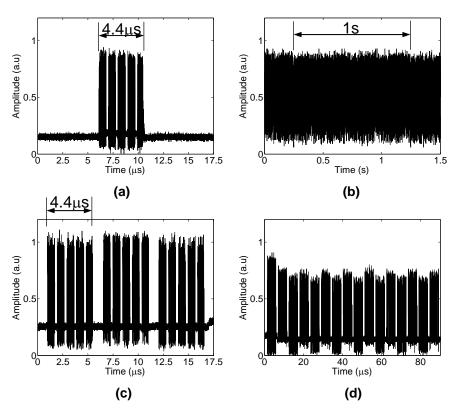

Figure 3 Experimental traces showing the memory function (a) The initial data packet consisting of 44k bits of data (equivalent to 4.4µs), (b) data is stored for one second, (c) the final three blocks of stored data after one second of storage time (d) the initial fifteen circulations of data storage demonstrating the self-levelling transient of the device.

Figure 3(a) shows the original 44kbits data packet or  $4.4\mu s$  of data consisting of five blocks of ones and four blocks of zeros (this simple data pattern was chosen as this could be easily seen on a real time oscilloscope). A space of  $1\mu s$  was included to enhance visual identification of the individual circulations. After the initial data packet enters the loop the data packet is then stored for one second, Figure 3(b). After one second the feedback loop is blocked which clears all data stored in the memory. Figure 3(c) shows the last three blocks taken from Figure 3(b) which can be compared with the initial input packet from Figure 3(a), we can see that the packet has been successfully stored. It can be seen in Figure 3(d) that although the initial stored data is of relatively high amplitude, the pulse amplitudes tend to evolve toward a stabilised level around which the amplitude of the blocks oscillate [10].

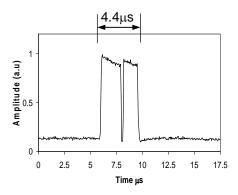

In order to provide a detailed characterisation of the device performance the initial data pattern was simplified to consist of only two blocks of ones separated by a short block of zeros whilst the total length remained at 44kbs, Figure 4. The results demonstrate the response of the device as a function of both peak power and data pulse timing for nine circulations (which is equivalent to 50µs storage time).

Figure 4 Initial data pattern consisting of two blocks of 1s separated by one block of 0s. The total packet length used was  $4.4\mu s$ .

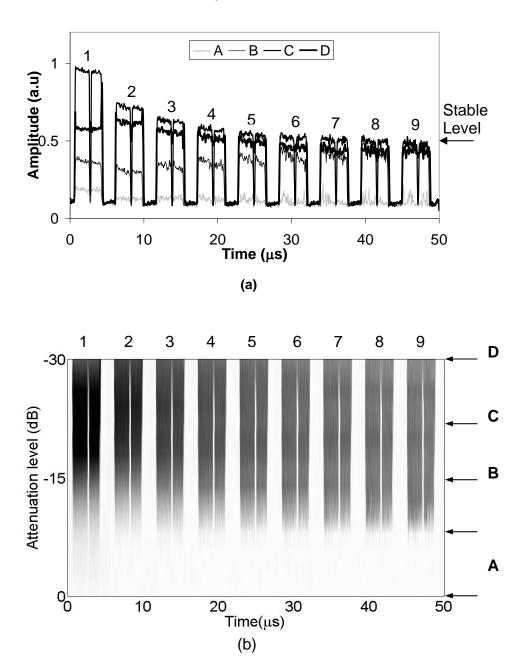

First we study the performance of the memory as a function of the power of the initially injected data packet. Figure 5(a) shows nine consecutive blocks stored in the memory at four different power levels. A more complete characterisation as a function of input power is shown in the intensity plot of Figure 5(b). Block 1 in Figure 5(a) is the first circulation, switched out by the original data packet, followed by blocks 2 to 9. When the initial data packet power is too low, A, the initial switched out clock pulses, block 1, are not high enough in intensity for the device to recover the data to a stable level and so therefore the data is lost. As the data increases in power and a greater phase shift is created between the two-propagating pulses, B, the initial data power is lower than the stable level, however, the transmitted output is sufficient for the data to be stored and after every circulation the level of the ones continues to increase until the stable level is reached. When the initial data power is high enough to cause a full  $\pi$  phase shift, required to provide complete switching, the initial level is higher than the stable level, C. Therefore, the intensity of the preceding levels reduces after every circulation,

until the stable level is reached. During the operation of the device the stable level, defined by the gain in the feedback, is set to provide switching less than pie to reduce the gain in the feedback and therefore suppressing propagating noise in the device. Any further increase of input power will generate a phase shift greater than  $\pi$  and so the intensity of the initial switched out block is reduced, D. In addition, the increase in the energy of the zeros (due a finite extinction level) will cause the zeros to turn into ones, corrupting the data. Figure 5b shows the full sweep from A to D in an intensity graph from the point where no data is stored at the lower levels (A) up to the point where the amplitude of the initial data is too high and the definition of the zeros is lost (D). Further increases in input power were limited by the risk of damage to the SOA, however we have found out that the device will store the data through a variation of 15dB in the initial data power.

Figure 5 Characterisation of the first nine circulations (a) shows data stored recovering to a stabilised level, for changing input data powers, (b) shows the full range of varying initial data input powers, starting from where the initial data is too low and no data is stored, A. increasing to B and C where good contrast between the zero and one levels is maintained and finally the initial data packet power is high enough to cause the zeros to become ones thus corrupting the data, at D.

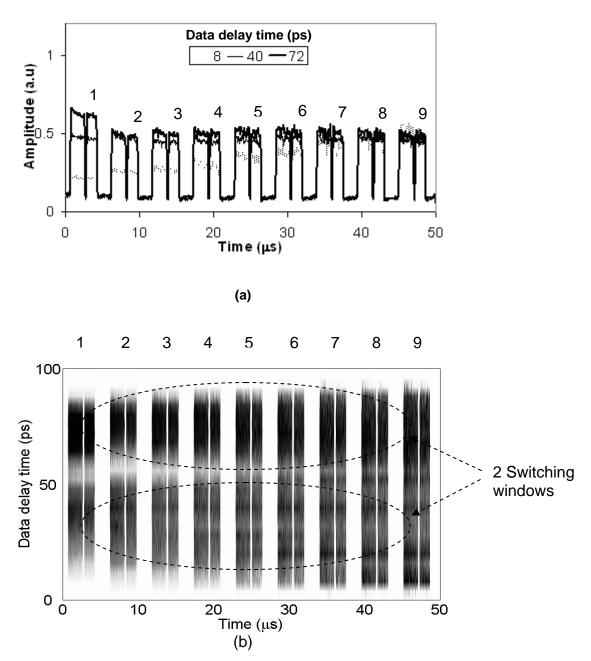

The arrival time of the control pulses at the SOA, with respect to the clock pulses, defines the switching efficiency of the TOAD, hence the optimum arrival time would allow for full switching to be achieved thereby producing maximum intensity at the data output. However, if a poor timing position is used then the TOAD would have a smaller transmission coefficient and thus the power at the data output would be low. Variations of initial data pulse timing with respect to the clock pulses are demonstrated in Figure 6(a) and 6(b). By changing the initial data timing, only, it can be demonstrated how tolerant the device is to phase wander (i.e. timing offset between the injected initial pulses and the clock stream) of the initial data input. We have already seen how the device reacts to a change in initial data power, by adjusting the timing of the initial data similar results should be obtained such that when the timing is in a poor position then there is not enough switched out power for the device to store the data. Alternatively if the timing is moved to a more efficient position then the power of the initial switched out data will increase, therefore the data is recovered and through consecutive circulations the switched out power will increase until a stable level is reached. In Figure 6 a delay time of Ops is defined as the position where the initial data timing is such that no pulses are switched out and hence the data cannot be recovered and therefore no data is stored. As the timing changes to 8ps, Figure 6(a), the differential phase shift generated by the control pulses is increased therefore the intensity of the switched out clock pulses increases, allowing for the consecutive circulations to store the data. Note that there are two prominent switching windows over a delay variation of 100ps, Figure 6(b). The location of the SOA, \(\tau\), is set to a 25ps offset, which means that the counter and copropagating pulses enter the SOA at equally spaced time intervals. In one window the counter propagating pulses will see a saturated SOA and in the other window the co-propagating pulse will see the SOA in a saturated condition, hence two operating windows. By comparing the operating points, 40ps and 72ps, it can be seen that the two windows are not identical, this is the result of the SOA being of a finite length. With the initial data timing at its optimum point of 72ps, defined by the amplitude of the output power, a maximum phase shift will be achieved and therefore the intensity of the output of the first circulation will be higher than the stable level, which is then reduced through consecutive circulations until the stable level is reached. It has been shown that the regenerative nature and the self levelling ability provide for a large tolerance to input phase wander (timing with respect to the bit period) which in this case would be 40ps in the initial data.

Figure 6 Memory performance as a function of delay in the data (a) Variation in data pulse timings for the two optimum positions for each window of 40ps and 72ps and a less efficient operating position of 8ps showing in all cases recovery to a stabilised level. (b) Full sweep of variation in input timings showing the two switching windows expected from a symmetrical SOA offset.

## Conclusion

In conclusion we have demonstrated an all-optical memory device, which utilises only one SOA and a single optical loop mirror. The memory is non-inverting and consists of two inputs, a clock source and a port for loading the memory. The scheme has been experimentally demonstrated and is capable of storing a 4.4kbit data packet for a period of 1 second (or 180,000 circulations of the loop). By varying the initial data input power and phase

wander this has given an indication of the regenerative capabilities and the tolerance to noise. From the results it has been demonstrated that the device is capable of storing data even when there is 40ps of phase wander and a 15dB variation in the optical peak power.

# **Acknowledgements**

The authors would like to thank members of the Photonics Research Group at Aston University for their continued help and support.

### References

- 1. Manning RJ, Phillips ID, Ellis AD, Kelly AE, Poustie AJ, Blow KJ, 10Gbit/s all-optical regenerative memory using single SOA-based logic gate. Electronics letters, 1999. 35(2): p. 158-159

- 2. A.J. Poustie, A.E. Kelly, R.J. Manning, K.J. Blow, *All-optical regenerative memory with full writerread capability*. Optics Communications, 1998. 154(5-6): p. 277-281.

- 3. Tucker RS, Ku PC, Chang-Hasnain CJ, Slow-light optical buffers: Capabilities and fundamental limitations. Journal of lightwave technology, 2005. 23 (12): p. 4046-4066.

- 4. Hunter DK, Chia MC, Andonovic I, *Buffering in optical packet switches*. Journal of lightwave technology, 1998. 16(12): p. 2081-2094.

- 5. Chia MC, Hunter DK, Andonovic I, Ball P, Wright I, Ferguson SP, Guild KM, O'Mahony MJ, Packet loss and delay performance of feedback and feed-forward arrayed-waveguide gratings-based optical packet switches with WDM inputs-outputs. Journal of lightwave technology, 2001. 19(9): p. 1241-1254.

- 6. N. A. Whitaker, Jr., M. C. Gabriel, H. Avramopoulos, and A. Huang, *All-optical, all-fiber circulating shift register with an inverter.* Optics Letters, 1991. 16(24): p. 1999-2001.

- 7. Sokoloff JP, Prucnal PR, Glesk I, Kane M, A Terahertz optical asymmetric Demuliplexor (TOAD). IEEE Photonics Technology letters, 1993. 5(7): p. 787-790.

- 8. Blow KJ, Doran NJ, Nelson BP, Demonstration of the nonlinear fibre loop mirror as an ultrafast all-optical demultiplexer. Electronics Letters, 1990. 26(14): p. 962-964.

- 9. N.C. Johnson, J.A. Harrison, K.J. Blow, All-optical regenerative memory using a semiconductor optical amplifier in a single loop mirror, in Photonics in Switching 2006. 2006: Crete.

- 10. Blow KJ, Manning RJ, Poustie AJ, *Nonlinear optical loop mirrors with feedback and a slow nonlinearity*. Optics Communications, 1997. 134(1-6): p. 43-48.