# Thermal Aspects of a Low Cost Power Electronic Converter for High Capacity, Smart Residential Distribution Networks

A. Amiri\*, A.M. Cross\*, N. Ignadossian\*\*, S. Safari\*\*\*, B. Godfrey†, P. Ward††, M. Owen†††

\*PEPS Group, Aston University, B4 7ET, Birmingham, UK, a.amiri@aston.ac.uk, a.m.cross@aston.ac.uk

\*\*Schneider Electric Ltd, TF3 3BL, Telford, Shropshire, UK, nick.ignadossian@schneider-electric.com

\*\*\*Turbo Power System (TPS), NE11 0QD, Gateshead, UK, ssafari@turbopowersystems.com

† Western Power Distribution, DE74 2TU, Derbyshire, UK, bgodfrey@westernpower.co.uk

†† Anvil Semiconductors Ltd, CV5 9QE, Coventry, UK, peterjward@anvil-semi.co.uk

†† Exception EMS Ltd, SN11 9PT, Calne, Wiltshire. UK, mike.owen@exceptionems.com

**Keywords:** Power electronic converter, SiC MOSFET, thermal design, Computational Fluid Dynamic (CFD)

## **Abstract**

A key challenge facing the UK Distribution Network Operators (DNOs) today is the increasing demand for power being placed on residential networks. Also, the increase in distributed generation (DG) is now resulting in unacceptable local voltage rises and power quality issues. A cost effective solution to these problems can be achieved on the existing infrastructure by increasing the local network phase voltage to 400 V and stepping back down to 230 V at each house, using a DNO-owned, voltage regulated power electronic converter (PEC). The thermal and protection issues associated with the design of such a PEC, which is to be installed in the meter-box of each property, are discussed in this paper.

## 1 Introduction

UK Government low carbon policies, in particular, the targets set by the Department of Energy and Climate Change (DECC) are to reduce greenhouse gas emissions by 80% relative to the 1990's level by 2050, with a significant shift from fossil fuels to renewables [1]. This policy restricts the consumption of gas and fuel for heating purposes in urban areas and drives residential properties to move to electro-heat. In addition, the high cost of fuel for personal transport as well as its high CO2 emissions is resulting in a gradual shift to electrical vehicles (EVs). The associated growth in demand for electrical energy brought about by these changes is placing an increasing burden on the capacity of existing LV residential networks.

The move away from fossil fuels to renewables has seen a promotion of small-scale low carbon technologies, such as photovoltaic (PV) systems – so-called distributed generation (DG). This has resulted in a significant increase in PV penetration on the LV distribution network [2]. However, this has had an undesirable impact on the network in terms of voltage rise, higher levels of imbalance and harmonic distortion. In particular, over-voltage violations are one of the overriding constraints that limit the hosting capacity of LV networks in terms of DG, which may hold back the UK's efforts to meet its CO2 reduction targets.

paper will give a status update This InnovateUK/EPSRC project "A Low Cost, High Capacity, Smart Residential Distribution Network Enabled by SiC Power Electronics". This work follows on from a previous InnovateUK Feasibility Study which showed that a cost effective solution to capacity problems can be achieved on the existing LV network infrastructure by increasing the local phase voltage to 400 V - the existing cable is rated at 600V [3]. To step the voltage back down to 230 V at each house, a DNO-owned, low-cost, high-efficiency power electronic converter (PEC) will be installed in the meter-box of the property. This system will not only increase network capacity, but also overcome the problem of network over-voltages within a customer's premises caused by a high penetration of DG. The overvoltage problem is mitigated since the PEC can be used to regulate the voltage on the customer side to 230 V. As well as these desirable characteristics the PEC can also enable optimised connections for emerging EV charging, DG and energy storage - the so-called "smart-grid" [3,4,5]. The main objective of the project is the small-scale demonstration of several PECs deployed on part of a residential network. The partners involved with this project include Exception EMS, Western Power Distribution, Schneider Electric, Anvil Semiconductors, Turbo Power Systems, and Aston University.

The previous Feasibility Study showed that the PEC must have a target rating of approximately 18 kVA. At this power level the efficiency must be better than 99% in order to avoid over-heating of the meter and derating of the cut-out fuse in the meter-box. The location of the PEC in the meter box therefore poses a number of significant challenges around the PEC design in terms of size, weight, efficiency and thermal requirements.

This paper starts by presenting an outline specification for the PEC. This is followed by a description of the proposed circuit topology and the selection of Silicon Carbide (SiC) transistor devices for the converter. Efficiency and power density are key requirement for the PEC due to its location in the meterbox, and it is found that this is significantly influenced by the protection devices within the consumer unit of the property. Results are presented from thermal analysis using Computational Fluid Dynamics (CFD) software, which were validated against hardware measurements carried out on the meter box and PEC. This analysis allows the cooling

requirements of the converter to be optimised whilst satisfying protection co-ordination within the house.

## 2 Power Electronic Converter (PEC)

## 2.1 PEC Specification

To satisfy the anticipated energy demand from residential properties up to the year 2050, an 18 kVA power rating has been identified as minimum capacity for the PEC [3]. In addition, the requirements of various network standards and regulations [6,7,8,9] as well as the constraints of the meter-box environment, determines the other main electrical and mechanical operating parameters for the PEC. These parameters are shown in Table 1:

| Parameters                     | Min     | Typical | Max      |                  |

|--------------------------------|---------|---------|----------|------------------|

| Power Rating                   |         | 18.4    |          | kVA              |

| Efficiency                     | 99      |         |          | %                |

| Input Voltage                  | 360     | 400     | 440      | V                |

| Input Current                  |         | 46      |          | $\boldsymbol{A}$ |

| No-Load Input current          |         | 0.5     |          | $\boldsymbol{A}$ |

| No-Load Input Power Factor     | 0.9 lag |         | 0.9 lead |                  |

| Output Voltage [8]             | 220     | 230     | 253      | V                |

| Output Voltage THD Level [8,9] |         | 5       | 8        | %                |

| Output Current                 |         | 80      |          | $\boldsymbol{A}$ |

| Input-to-Output Neutral        |         |         | 1        | $m\Omega$        |

| Connection Impedance           |         |         | 1        | ms2              |

| PEC Dimension:                 |         |         |          |                  |

| Height                         |         |         | 50       | Cm               |

| Width                          |         |         | 16       | Cm               |

| Depth                          |         |         | 17       | Cm               |

| Weight                         |         | 5       |          | Kg               |

Table 1. PEC electrical and mechanical specifications

## 2.2 PEC Circuit

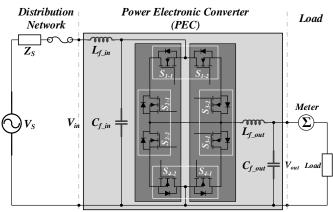

Previous work [4,5] has shown that a bi-directional, AC chopper circuit using SiC MOSFETs is the best candidate to fulfil the above requirements for the PEC, as it requires a minimum number of transistors in the main power path and has a very simple structure and control requirement.

The AC Chopper consists of two bi-direction switches. However, a bidirectional SiC MOSFET switch in a single package is not commercially available at present. Therefore, in order to realise these switches using off-the-shelf products there are two options:

- 1. Using single TO-247 package MOSFETs: the highest rated current available SiC MOSFET in this package is the C2M0025120D (60 A, 1.2 kV, 25 m $\Omega$ ) from CREE. Two devices are connected in series with common Source to provide a bi-directional switch. To achieve 99% efficiency at 18 kW detailed Spice circuit simulation were carried out, where it was found that four of these bidirectional switches were needed. This would result in a total of 16, TO-247 MOSFETs for the AC Chopper.

- 2. Using half-bridge modules CAS120M12BM2 (120 A, 1.2 kV, 13 m $\Omega$ ) from CREE. Here the half-bridge modules have to be connected as shown in Figure 1. In this arrangement the PEC consists of two parallel AC

choppers, where pairs of switches  $(S_{1-1}, S_{2-1})$  and  $(S_{2-2}, S_{4-2})$  form one independent AC chopper and pairs of switches  $(S_{1-2}, S_{3-2})$  and  $(S_{3-1}, S_{4-1})$  form another independent AC chopper. The parallel arrangement gives additional flexibility in the control and utilisation of the devices, for example interleaved configurations are possible with this arrangement [10]. To achieve 99% efficiency at 18 kW it was found 4 half-bridge MOSFET modules were required.

Figure 1. AC chopper realization using half-bridge SiC modules

A bi-directional SIC MOSFET in a single module has previously been announced by Microsemi APTMC120DUM08D3AG, but this device appears to have been withdrawn from the market.

## 2.3 PEC Protection Co-ordination

A comprehensive review of standards, regulations and engineering recommendations and in particular, BS7671:2008 IET Wiring regulation 17<sup>th</sup> Edition, was performed in order to assess the requirements of the PEC in terms of protection. In particular, the PEC overcurrent characteristic must coordinate with the existing protective devices installed within the consumer unit of the house. In modern houses the consumer unit contains a number of Miniature Circuit Breakers (MCBs), which protects the cables and connectors of different rated circuits within the property, for example the ring-main, lighting, kitchen appliances and electric showers. The MCB consists of a two trip mechanisms:

- A thermal, bimetallic actuator, which mimics the behaviour of a traditional fuse and results in a timed overload protection.

- A magnetic actuator, which results in an instantaneous overcurrent protection.

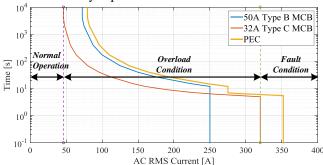

The MCB trip-time versus current characteristic is shown in Figure 2 for a 50 A type B and 32 A type C MCBs from BS EN 60898. The trip-time characteristic for an MCB has three distinct operating regions as shown for the 32 A Type C curve in Figure 2, which are,

- Normal condition Nominal current can be supplied to the load for an unlimited time.

- Overload condition an overload current above the nominal value can be supplied to the load for a limited time. This time is on a scale of tens of seconds to a

number of hours. This characteristic exploits the thermal capacitance of the cables within the house.

Fault condition – Any current exceeding the maximum value – 10 x nominal, which is 320 A for the 32 A breaker – will instantly trip the MCB.

Figure 2. 50 A Type B (blue curve) and 32 A type C (red curve) MCB trip-time versus time characteristics and associated PEC trip characteristic (yellow curve)

In order for the PEC to co-ordinate with these devices, the PEC characteristic must lie above the maximum envelope enclosing the characteristics of all MCB types in the consumer unit. This envelope will mainly be determined by breaker with the largest rating, but will also depend on the breaker type - B, C or D. For example, the envelope of the 50 A type B and 32 A type C characteristics, which are typical of the largest breakers used in domestic housing and are shown in Figure 2, leads to the proposed PEC characteristic shown by the yellow curve in the Figure 2, which includes a 10% current margin to allow for circuit tolerances and noise.

An undesirable outcome from the need for protection coordination is that the PEC has to supply 10x the rated current of the circuit breaker for 5 seconds. This is a very onerous requirement in terms of the PEC semiconductors and means that the 120 A SiC modules that would be suitable for the 18 kW continuous rating, cannot meet the overload requirements. The following sections will show that the 120 A devices therefore have to be uprated to 300 A CREE CAS300M12BM2 devices in order to satisfy the overload characteristic.

## 3 PEC Thermal Constraints

One of the key challenges facing the project is the thermal constraints arising from the location of the PEC in the meter box of a house. This is coupled with the need to co-ordinate the PEC protection with the existing circuit breakers in the consumer unit, which means that the PEC has to provide a large overload capability for a period of several hours. The converter losses during this period are therefore of crucial importance in terms of satisfying the temperature limits of the PEC and its environment, which include:

- The inside temperature of the meter box and the effect on the electricity meter and cut-out fuse.

- The temperature within the PEC enclosure and the effect on the PEC electronics.

- The "Touch" temperature of any exposed parts of the PEC, which may harm the general public.

• The SiC semiconductors junction temperatures.

Under any operating condition the absolute ambient temperature of the electricity meter and the PEC electronic components should not exceed 50°C and 80°C, respectively. The temperature rise of the semiconductor junction temperatures depends on the material and packaging, for current commercially available SiC devices from CREE this limit is 150°C. Based on [6], during normal operation the maximum temperature of any surface of the PEC which may be exposed to human contact should not exceed 80°C for metallic parts and 90°C for non-metallic parts. Due to the poor reliability of fans the cooling of the PEC is to be through natural ventilation.

These constraints have an impact on the design of the heatsink as well as its location in relation to the PEC enclosure and meter box. Therefore in order to investigate these characteristics, temperature measurements were taken from a typical meter box that contained the main thermal components of the PEC such as heat sources, heatsink and any bodies that affected air flow such as the PEC enclosure, meter, meter-box door and any associated ventilation slots. These issues are described in the next section.

# 4 Simulation and Experimental Investigations

#### **4.1 PEC Circuit Simulation**

In order to investigate the effect of the maximum temperature constrains described in the previous section, on the PEC triptime characteristic shown in Figure 2, the relationship between PEC losses and current was calculated using circuit simulation. This consisted of a carrying out a set of simulations using LTspice with detailed Spice models provided by CREE for the SiC MOSFETSs and diodes, for different values of PEC output current. Partial validation of the calculated losses was carried out by comparison against CREE datasheet curves of switching losses against voltage and current as well as drain-source resistance as a function of temperature, which agreed within 5%.

| Parameter                                       |                     | Value   |           |

|-------------------------------------------------|---------------------|---------|-----------|

| Input Voltage                                   | $V_S$               | 400     | V         |

| Input Voltage Source Impedance                  | $R_S$               | 0.1     | Ω         |

| Input Filter Inductor                           | $L_{f\_in}$         | 50      | μН        |

| Input Filter Inductor Resistance                | R <sub>Lf_in</sub>  | 10      | $m\Omega$ |

| Input Filter Capacitor                          | $C_{f\_in}$         | 5       | μF        |

| <b>Input Filter Capacitor Stray Inductance</b>  | $L_{Cf\_in}$        | 7.5     | nН        |

| Output Filter Inductor                          | $L_{f\_out}$        | 100     | $\mu H$   |

| Output Filter Inductor Resistance               | R <sub>Lf_out</sub> | 5       | $m\Omega$ |

| Output Filter Capacitor                         | $C_{f\_out}$        | 10      | μF        |

| <b>Output Filter Capacitor Stray Inductance</b> | Lcf_out             | 3       | nН        |

| Gate Resistor                                   | $R_G$               | 3       | $\Omega$  |

| Switching Frequency                             | $f_{SW}$            | 30      | kHz       |

| <b>Duty Cycle</b>                               | $\boldsymbol{D}$    | 0.575   |           |

| Dead-Time                                       | $T_{DT}$            | 100     | ns        |

| CREE SiC MOSFET – Bare Die                      | CPM2-1200-0025B     |         |           |

| CREE Schottky Diode – Bare Die                  | CPW4-               | -1200-S | 020B      |

Table 2. AC chopper LTspice simulation parameters

Table 2 summarises the parameters used in the simulation, where main circuit component references correspond to those

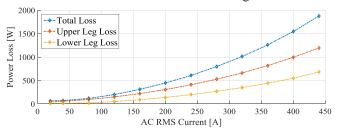

shown in Figure 1. Figure 3 shows the total power dissipation from the semiconductor devices averaged over one 50 Hz cycle of the mains as well as the individual upper and lower device losses of the Chopper leg, as a function of Chopper output current. Input and output filter losses and gate driver losses are not included in results shown in Figure 3.

Figure 3. Total (blue curve), upper (red curve) and lower (yellow curve) Chopper leg power dissipations of the AC chopper with 4 off, 300 A SiC MOSFET modules

## **4.2 PEC Thermal Experimental Measurements**

A complete set of experimental measurements and CFD simulations were performed to find the maximum limits on semiconductor power dissipation that could be achieved for a particular heatsink design and PEC layout for both steady-state and transient conditions.

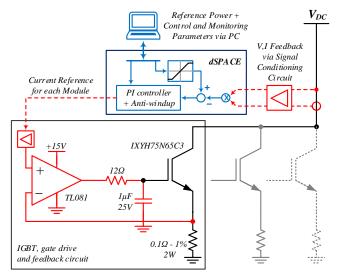

The semiconductors power dissipation was emulated using an IGBT based active load. The active load was implemented using a dSPACE controller and consisted of 16, IXYH75N65C3 (75A, 650V, TO-247) IGBTs connected in parallel, which represented the individual dies within the CREE MOSFET modules. Figure 4 shows the schematic for a single IGBT. Each IGBT had analogue closed-loop current control to ensure current sharing between devices. A hall-effect current sensor measured the total current of all the IGBTs, which was fed back to the dSPACE controller along with a measurement of the IGBT collector-emitter voltages. These measurements were then used to calculate power dissipation which was used as feedback to a closed-loop PI power controller in dSPACE. The controller produced a common current reference for each IGBT.

Figure 4. IGBT based active load for power loss emulation

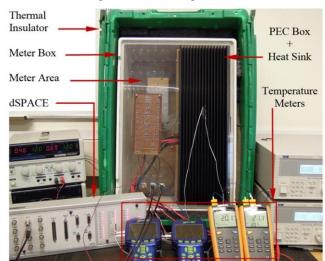

The experimental setup is shown in Figure 5. It can be seen from Figure 5 that the heatsink is mounted outside the meter box through an aperture on the polycarbonate meter-box door – the IGBTs were mounted on the surface of the heatsink which faced the inside of the meter box. The reason for mounting the heatsink on the outside of the meter box is because it was found that if it was mounted inside, the temperature rise around the meter and cut-out fuse is excessive for a 99% efficient converter. The PEC heatsink and enclosure design is shown in Figure 6.

Figure 5. Experimental setup for thermal investigation

Figure 6. PEC heatsink and enclosure design

An extruded aluminium heatsink from ABL with a black anodized surface was used in the tests (ABL-159AB). Two different lengths of this heatsink were used during the tests 50cm and 35cm. The PEC enclosure was represented by an MDF box placed inside the meter box behind the heatsink. A cardboard model of the meter was also placed in the meter box to mimic the disturbance of air-flow within the meter-

box. All the tests ran with an ambient temperature of approximately 23°C. With the system initially at ambient temperature, the dSPACE controller was used to apply a step power dissipation from the IGBTs, and temperature vs. time measurements were taken of (1) the case of the IGBTs, (2) the heatsink, (3) the inside of the PEC enclosure, and (4) the inside of the meter box, close to the meter. The IGBT junction temperatures were estimated from the case temperature using datasheet values of the junction-case thermal resistance.

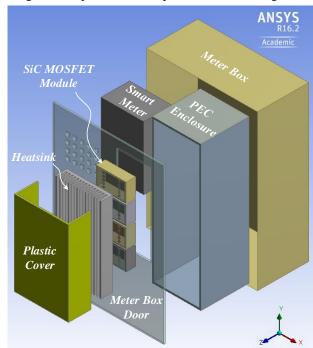

With the arrangement shown in Figure 6, it was found that without the heatsink cover, the heatsink touch temperature was the limiting factor in the PEC design exceeding the maximum 80°C specified in section 3. This is shown in Figure 7, which is a plot of the measured absolute touch temperature of the heatsink and estimated junction temperature for a heatsink length of 50 cm and a step power dissipation of 150 W, which equates to a converter efficiency of 99.2%.

Figure 7. Measured absolute temperature for the estimated transistor junction temperature (blue curve) and heatsink (touch) temperature (red curve) with 150W power dissipation for 50 cm length heatsink

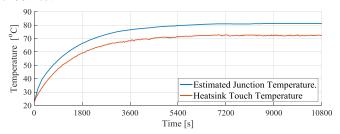

In order to overcome this problem a plastic cover with openings at the top and bottom was placed over the heatsink – see Figure 6. The corresponding temperature transient for the transistor junction temperature, heatsink temperature and heatsink cover, for a 150 W step dissipation is shown in Figure 8, for both the 35 cm and 50 cm length heatsinks.

Figure 8. Measured absolute temperature for the estimated junction temperature (blue curve), heatsink (red curve) and heatsink cover (yellow curve) for 150W power dissipation for 50 cm and 35 cm heatsink

It can be seen from Figure 8 that the effect of the heatsink cover is to increase the steady-state junction temperature by only 4°C, whilst the cover (touch) temperature is it a safe level of 35°C. It may be expected that the inclusion of a heatsink cover would have a detrimental effect on the

junction temperature. However, the modest increase in junction temperature of 4°C arises to the desirable "chimney effect" [11], which occurs as ambient air is forced upward through the vertically oriented heatsink fins by convection.

With the heatsink cover included it was found that for higher values of dissipation, the estimated junction temperature became the limiting factor - maximum 150°C from section 3. For steady-state conditions the maximum continuous power dissipation was found to be approximately 300 W, as presented in Table 3, for both the two heatsink lengths. This resulted in an approximate junction temperature of 140°C.

| Donometer                          |        | Heatsink    |     |         |

|------------------------------------|--------|-------------|-----|---------|

| Parameter                          |        | 50cm   35cm |     |         |

| <b>Continues Power Dissipation</b> | $P_D$  | 300         | 300 | W       |

| Junction Temperature               | $T_J$  | 138         | 146 | $^{o}C$ |

| Cover Touch Temperature            | Trouch | 51          | 54  | $^{o}C$ |

Table 3. Continuous power dissipation capacity of heatsinks

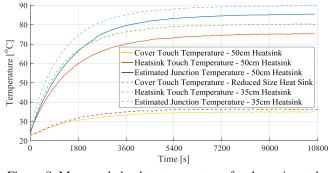

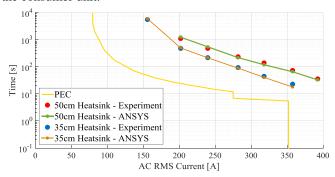

To obtain the PEC overload characteristic, step dissipations were applied starting with the PEC in a steady-state continuous condition with 150W power dissipation. This value of dissipation was chosen as half the maximum continuous rating of 300 W and hence enables an overload region to be realised. The tests were terminated when the estimated junction temperature reached 150°C and the duration of the transient was recorded. The value of step dissipation was converted to a corresponding PEC output current value using the relationship shown in Figure 3. The duration of the transient was plotted against this current to give the PEC overload characteristic for both the 50 cm and 35 cm heatsinks and is shown in Figure 9 along with the PEC protection co-ordination curve from Figure 2 for comparison. Figure 9 shows that with the 300 A CREE modules both the 50 cm and 35 cm heatsinks are above the PEC overload curve as required, and will therefore co-ordinate with the MCBs in the consumer unit.

Figure 9. PEC overload characteristic for the 50 cm (red dot) and 35 cm (blue dot) heatsinks and the corresponding PEC protection co-ordination curve (yellow curve)

## 4.3 PEC Thermal CFD Simulation Results

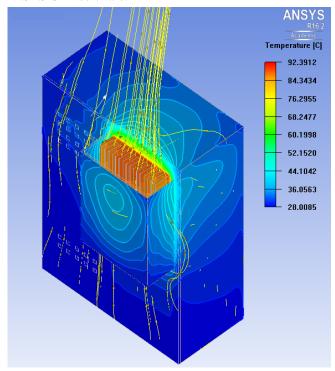

Computational Fluid Dynamic (CFD) software was used to optimise the heatsink design as it was more convenient to examine different scenarios than direct measurement. For this purpose, ICEPAK from ANSYS was selected to simulate and study the PEC under different conditions. The simulation included the meter-box mounted on a table within a volume

of 5m x 5m x 3m. The ANSYS model was validated against measurement and the simulation results are shown by the curves in Figure 9 for both the 35cm and 50cm heatsinks. As shown in Figure 9, the error between the measured and predicted results is less than 5%, which shows good agreement. Figure 10 show a typical graphical output of temperature profiles and air flow streamlines from the ANSYS CFD software.

Figure 10. Temperature and air flow streamline calculations using ANSYS CFD software

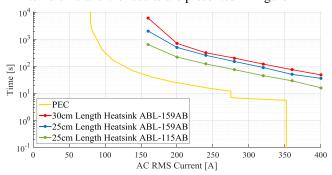

In order to optimise size and weight of the heatsink a set of CFD simulations were performed on smaller 30cm and 25cm length heatsinks as well as a reduced height, 25 cm heatsink (ABL-115AB). In the scenario the model included the actual CREE Modules with the meter-box wall-mounted in a semi-infinite volume and the results are presented in Figure 11.

Figure 11. ANSYS-ICEPAK simulation results for PEC overload characteristic for the 30 cm (red) and 25 cm (blue) heatsinks, thinner 25 cm ABL-115AB heatsink (green) and the corresponding PEC protection co-ordination (yellow)

Again from Figure 11 it can be seen that the overload curves for all three of these heatsink lie above the PEC curve and will therefore co-ordinate with the MCBs in the house.

Further heatsink optimisation is possible; however the size of the CREE MOSFET modules sets the minimum heatsink length at approximately 25 cm.

#### 5 Conclusion

This paper has discussed the thermal and protection issues for a meter-box mounted PEC for residential power networks. The PEC heatsink, which is naturally ventilated, has to be located outside meter box in order to avoid overheating of the meter and cut-out fuse. CFD simulations using ANSYS ICEPAK, which were validated against measurement, were used to optimise the heatsink size and weight.

## Acknowledgements

The authors gratefully acknowledge the financial support received from Innovative UK/EPRSC.

## References

- [1] H. Wanga, A. Saint-Pierreb, P. Mancarellac, "System Level Cost and Environmental Performance of Integrated Energy Systems: An Assessment of Low-Carbon Scenarios for the UK", *IEEE PowerTech*, Eindhoven, Pages: 1 6, (2015).

- [2] A. Navarro, L.F. Ochoa, D. Randles, "Monte Carlo-Based Assessment of PV Impacts on Real UK Low Voltage Networks", *IEEE Power and Energy Society General Meeting* (PES), pp. 1-5, (2013).

- [3] E. Zacharis, A.M. Cross, B. Godfrey, S. Safari, P. Ward, A. Castellazzi, I. Mosely, "High efficiency SiC AC chopper for LV networks", 7th Power Electronics, Machines and Drives conference, PEMD, pp. 1-6, (2014).

- [4] E. Zacharis, A.M. Cross, B. Godfrey, "Power electronic interfaces for low voltage residential networks", 15th European Conference on Power Electronics and Applications, EPE, pp. 1-10, (2013).

- [5] E. Zacharis, A.M. Cross, B. Godfrey, "Power Quality Improvements for LV Networks", *IET Seminar on Power Quality*, pp. 1-2, (2012).

- [6] BS 7671:2008, "Requirements for Electrical Installation IET Wiring Regulation" 17<sup>th</sup> Edition, amendment 3:2015.

- [7] Engineering Recommendation P25/1, "The short circuit characteristics of electricity boards low voltage distribution networks and the coordination of overcurrent protective devices on 230V single phase supplies up to 100A", 1996.

- [8] BS EN 50160:2010, "Voltage characteristics of electricity supplied by public electricity networks", 2010.

- [9] Engineering Recommendation G5/4-1, "Planning Levels for harmonic Voltage Distortion and the Connection of Non-Linear Equipment to Transmission Systems and Distribution Networks in the UK", ENA 2005.

- [10] G. Calderon-Lopez, A.J. Forsyth, "High-Power Dual-Interleaved ZVS Boost Converter with Interphase Transformer for Electric Vehicles" 24th Applied Power Electronics Conference and Exposition, APEC, pp. 1078 – 1083, (2009).

- Conference and Exposition, APEC, pp. 1078 1083, (2009).

[11] G. De Mey, M. Wójcik, J. Pilarski, M. Lasota, J. Banaszczyk, B. Vermeersch, A. Napieralski, M. De Paepe "Chimney Effect on Natural Convection Cooling of a Transistor Mounted on a Cooling Fin", Journal of Electronic Packaging, Volume 131, Issue 1, (2009).