If you have discovered material in AURA which is unlawful e.g. breaches copyright, (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please read our <u>Takedown Policy</u> and <u>contact the service</u> immediately

# All-optical regenerative memory using a single device

## Nigel Christopher Johnson

Doctor of Philosophy

Aston University

October 2009

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis or information derived from it may be published without proper acknowledgement.

Private allegations

e optavi angeliana **vajis**i

## **Aston University**

## All-optical regenerative memory using a single device

**Nigel Johnson**

Doctor of Philosophy

October 2009

In recent years the optical domain has been traditionally reserved for node-to-node transmission with the processing and switching achieved entirely in the electrical domain. However, with the constantly increasing demand for bandwidth and the resultant increase in transmission speeds, there is a very real fear that current electronic technology as used for processing will not be able to cope with future demands. Fuelled by this requirement for faster processing speeds, considerable research is currently being carried out into the potential of All-optical processing.

One of the fundamental obstacles in realising All-optical processing is the requirement for All-optical buffering. Without all-optical buffers it is extremely difficult to resolve situations such as contention and congestion. Many devices have been proposed to solve this problem however none of them provide the perfect solution.

The subject of this research is to experimentally demonstrate a novel all-optical memory device. Unlike many previously demonstrated optical storage devices the device under consideration utilises only a single loop mirror and a single SOA as its switch, whilst providing full regenerative capabilities required for long-term storage. I will explain some of the principles and characteristics of the device, which will then be experimentally demonstrated. The device configuration will then be studied and investigated as to its suitability for Hybrid Integrated Technology

#### Additional keywords and phrases

Non-linear optics, cross-phase modulation, All-optical memory, Terahertz Optical Asymmetric Demultiplexor, Semiconductor optical amplifiers. Hybrid integrated device.

#### Acknowledgements

This thesis would not have been possible without the guidance help and support of many people. Firstly, I would like to thanks my parents for always being there. Not only throughout this thesis but also throughout the total duration of all my studies passed, present and future. Secondly, this research would not have been possible or as enjoyable without the help and support from the excellent staff at Aston University. I would like in particular to thank Dr Paul Harper for his knowledge, experience and friendship without which my research would not have been as successful or as pleasurable. I would also like to acknowledge Dr Jim Harrison for his help, friendship and guidance.

I would like to add a special thank you to Professor Keith Blow who has been much more than just a supervisor. I would like to thank him for the patience he has shown throughout my studies; through him I have learn't so much. Throughout my research his guidance and knowledge has made all the difference.

### Contents

| 1. Introdu  | uction to optical communications           | _1 |

|-------------|--------------------------------------------|----|

| i. iiitioat | OCA equality)                              |    |

| 1.1. Intro  | oduction                                   | 1  |

| 1.2. Opt    | tical fibre                                | 2  |

| 1.3. Dig    | ital transmission over optical fibres      | 6  |

|             | nal degradation effects in optical fibres  |    |

| 1.4.1.      | Attenuation                                | 10 |

| 1.5. Chr    | romatic dispersion                         |    |

| 1.5.1.      | Material dispersion                        |    |

| 1.5.2.      | Waveguide dispersion                       | 13 |

| 1.6. Net    | twork topology                             | 14 |

| 1.7. Typ    | oes of optical memory                      |    |

| 1.7.1.      | Pulse preserving                           | 17 |

| 1.7.2.      | Pulse regeneration                         |    |

| 1.7.3.      | Slow light                                 | 21 |

| 1.8. Ba     | sic operation and types of interferometers | 21 |

| 1.8.1.      | The Mach-Zehnder interferometer            | 21 |

| 1.8.2.      | Sagnac loop mirror                         | 23 |

| 1.8.3.      | Interferometer theory                      | 24 |

| 1.9. No     | n-linear elements                          | 27 |

| 3 1.10. The Semiconductor Optical Amplifier31                                                  |

|------------------------------------------------------------------------------------------------|

| 1.10.1. Wavelength conversion35                                                                |

| 1.10.2. Basic SOA equations used for modelling an SOA in a loop                                |

| mirror                                                                                         |

| 1.11. Discussion40                                                                             |

| 2. Terahertz Optical Asymmetric Demultiplexer proof of                                         |

| principle and setup41                                                                          |

| 2.1. Introduction41                                                                            |

| 2.2. The loop mirror41                                                                         |

|                                                                                                |

| 2.3. Controlled switching configuration42                                                      |

| 2.4. Self-switching experimental demonstration and characterisation 46                         |

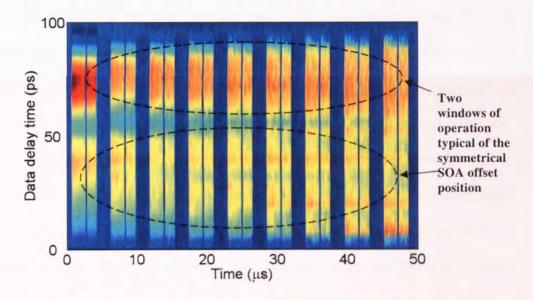

| 2.4.1. SOA offset positioning52                                                                |

| 2.5. Controlled switching experimental demonstration and characterisation53                    |

| 2.5.1. Control pulse timing and SOA offset characterisation56                                  |

| 2.6. SOA symmetrical offset position demonstration59                                           |

| 2.7. Clock power characterisation65                                                            |

| 2.8. SOA recovery measurements and influences69                                                |

| 2.8.1. SOA recovery rate measurements71                                                        |

| 2.8.2. Numerical simulations demonstrating the effect of a slow SOA on the operation of a TOAD |

| 2.9. Discussion79                                                                              |

| 3. Int | roduction to the non-inverting memory                   | 80  |

|--------|---------------------------------------------------------|-----|

|        |                                                         |     |

| 3.1.   | Introduction                                            | 80  |

| 3.2.   | Inverting memory                                        | 80  |

| 3.3.   | Non-inverting memory                                    | 83  |

| 3.4.   | Numerical simulation                                    | 84  |

| 3.5.   | Basic experimental proof of principle                   | 93  |

| 3.5    | i.1. Experimental setup using the clock as reset        | 94  |

| 3.5    | i.2. Experimental Setup using the feedback as the reset | 99  |

| 3.6.   | Results                                                 | 101 |

| 3.7.   | Discussion                                              |     |

| 4. Sir | mple pattern operation                                  | 105 |

| 4.1.   | Introduction                                            | 105 |

| 4.2.   | Initial data power characterisation                     |     |

| 4.3.   | Initial data timing characterisation                    | 108 |

| 4.4.   | Feedback gain characterisation                          | 110 |

| 4.5.   | Feedback timing characterisation                        | 113 |

| 4.6.   | SOA current characterisation                            | 116 |

| 4.7.   | Clock power characterisation                            | 117 |

| 4.8.   | Discussion                                              | 119 |

| 5 | . Bit          | error rate characterisation of the memory12                                                                        | 21  |

|---|----------------|--------------------------------------------------------------------------------------------------------------------|-----|

|   | 5.1.           | Introduction                                                                                                       | 21  |

|   | 5.2.           | Bit error rate measurement considerations12                                                                        | 22  |

|   | 5.2.           | 1. Temperature1                                                                                                    | 22  |

|   | 5.2.           | 2. Operational bit rate1                                                                                           | 24  |

|   | 5.3.           | BER curves measuring the quality of the stored data1                                                               | 25  |

|   | 5.4.           | Q Values of the stored data1                                                                                       | 27  |

|   | 5.5.           | Intensity graphs up to 1000 circulations1                                                                          | 30  |

|   | 5.6.<br>measi  | Initial data power attenuation characterisation using BE                                                           | ΕR  |

|   | 5.7.           | Initial data timing characterisation using BER measurements1                                                       | 39  |

|   | 5.8.<br>using  | Relationship of the initial data timing and attenuation characterisati initial data with good and poor extinctions |     |

|   | 5.9.           | Feedback timing characterisation using BER measurements1                                                           | 50  |

|   | 5.10.          | Feedback attenuation characterisation using BER measurements 152                                                   | nts |

|   | 5.11.          | SOA current characterisation using BER measurements1                                                               | 54  |

|   | 5.12.<br>using | Relationship between the SOA current and feedback attenuations and seedback attenuations                           |     |

|   | 5.13.          | Clock power characterisation using BER measurements1                                                               | 58  |

|   | 5.14.          | 5Gb/s operation using BER measurements1                                                                            | 60  |

|   | 5.15.          | Discussion1                                                                                                        | 61  |

|                                       | brid integrated Mach-Zehnder interferometer (MZI) 163                  |

|---------------------------------------|------------------------------------------------------------------------|

| 6.1.                                  | Introduction163                                                        |

| 6.2.                                  | Introduction to the hybrid integrated Mach-Zehnder interferometer  164 |

| 6.3.                                  |                                                                        |

| 6.4.                                  | Unbalancing the Mach Zehnder Interferometer using SOA current 172      |

| 6.5.                                  | Phase shifters characterisation                                        |

| 6.6.<br>devic                         | Demonstration of non-inverting memory using hybrid integrated e 179    |

| 6.7.                                  | Discussion                                                             |

| 7. Co                                 | onclusions and further work183                                         |

|                                       |                                                                        |

| 7.1.                                  | Conclusion                                                             |

|                                       |                                                                        |

| 7.2.                                  | Conclusion                                                             |

| 7.2.                                  | Conclusion                                                             |

| 7.2.<br><b>8. A</b> r                 | Conclusion                                                             |

| 7.2.<br><b>8. A</b> r<br>8.1.         | Conclusion                                                             |

| 7.2.<br><b>8. A</b> r<br>8.1.<br>8.2. | Conclusion                                                             |

## Figure listings

| 1 - 1 - 1 4 Schematic With a second control of the second control |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-1 Total internal reflection occurs when the angle of incidence (Ø <sub>1</sub> ) is equal to or greater than the critical angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 1-2 Light entering one end of a curved fibre will propagate using internal reflection and exit at the opposite end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 1-3 Propagation of singlemode (a) and multimode (b) fibres and typical dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

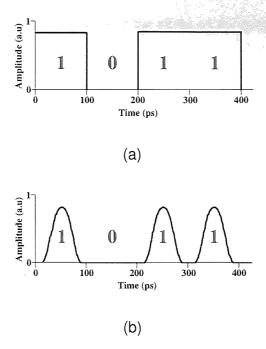

| Figure 1-4 10Gb/s (a) Non-Return to Zero (NRZ), (b) Return to Zero (RZ), modulation formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

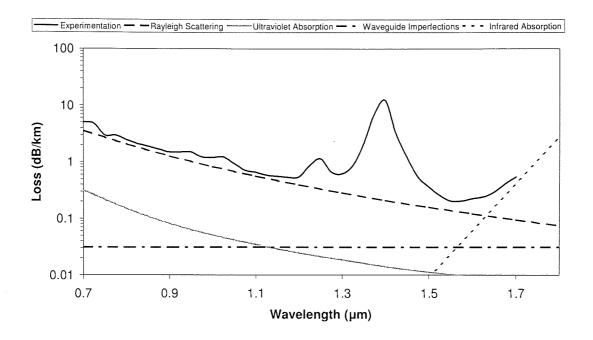

| Figure 1-5 Loss spectrum of Single Mode Fibre (SMF) demonstrating wavelength dependant loss mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

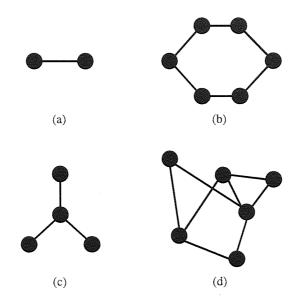

| Figure 1-6 Different types of network architecture, (a) Point-to-point, (b) Ring, (c) Star, (d) Mesh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

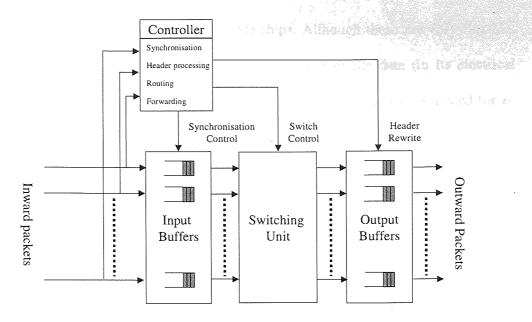

| Figure 1-7 A schematic of a network node showing the Switching unit,  Controller, Input and Output buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

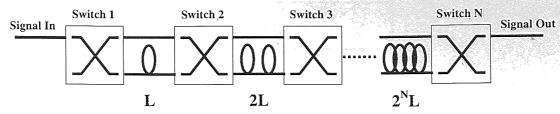

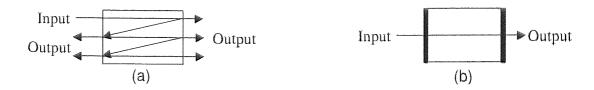

| Figure 1-8 A feed-forward tuneable delay line using 2 x 2 cross switch18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

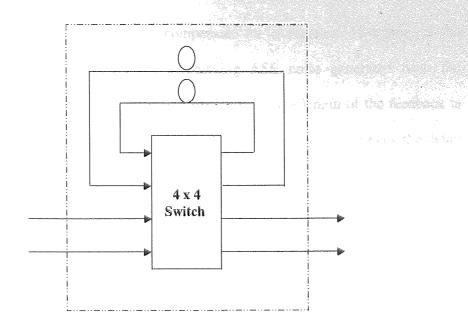

| Figure 1-9 A feedback delay line architecture using a 4x4 cross connect switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

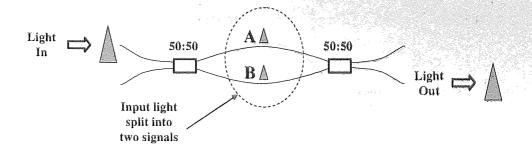

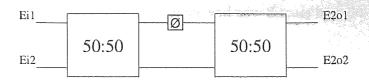

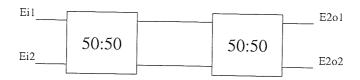

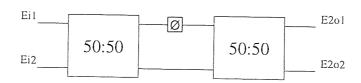

| Figure 1-10 Mach Zehnder interferometer. Light entering the device through the first 50:50 coupler is split into two identical signals A and B. These signals propagate through two identical arms and recombine in the second 50:50 coupler to exit solely out of one port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

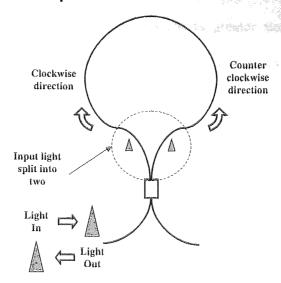

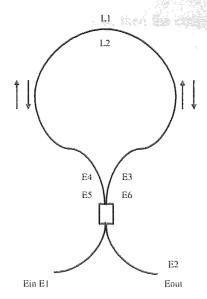

| Figure 1-11 Sagnac loop mirror. Light entering the input port will split into two, propagate around the loop and recombine in the coupler and exit through the initial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

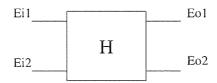

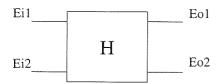

| Figure 1-12 Mach-Zehnder interferometer (MZI)24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 1-13 Sagnac loop interferometer25                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-14 Schematic of a simple 2 x 2 coupler with two inputs and two outputs                                                                                                                         |

| Figure 1-15 Schematic of an interferometer, two 2 x 2 couplers connected output to input                                                                                                                |

| Figure 1-16 Non-linear Amplified Loop Mirror (NALM)28                                                                                                                                                   |

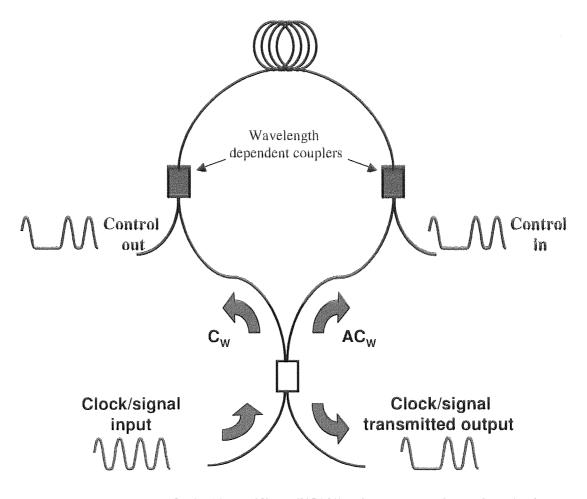

| Figure 1-17 Non-linear Optical Loop Mirror (NOLM) using separated wavelengths for the control and clock signals30                                                                                       |

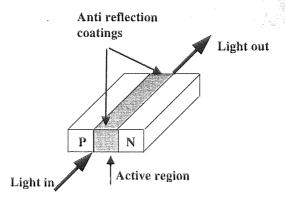

| Figure 1-18 (a) Fabry-Perot (FP-SOA), (b) Travelling Wave TW-SOA32                                                                                                                                      |

| Figure 1-19 PN junction of an SOA showing the active region and the anti-<br>reflection coatings33                                                                                                      |

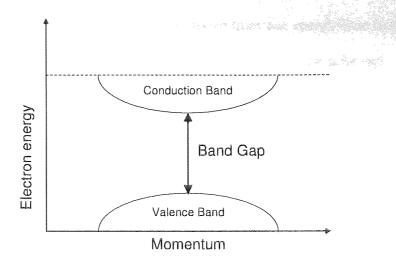

| Figure 1-20 Showing the energy bands of an AGaS SOA, when sufficient energy is absorbed by the electron the electron will move from the Valence Band to the conduction band                             |

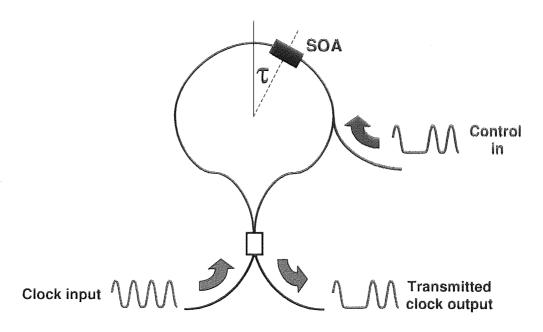

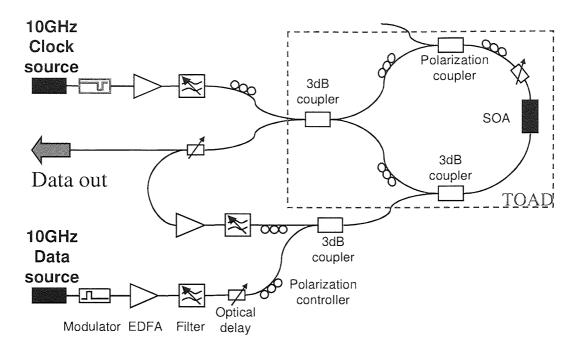

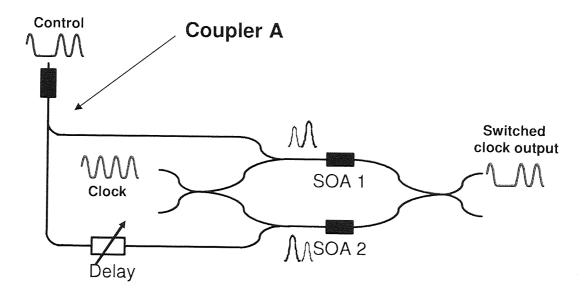

| Figure 2-1 Controlled switching configuration using the two different wavelengths for the clock signal. The control signal separation is achieved using a bandpass wavelength filter on the output      |

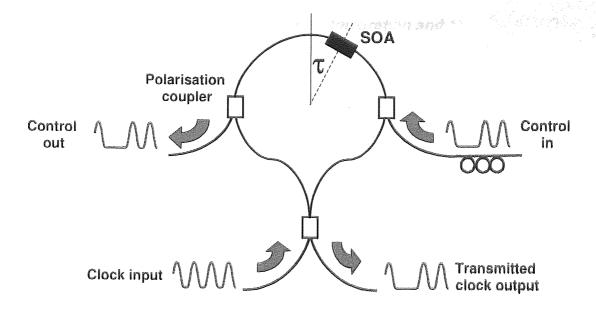

| Figure 2-2 Controlled switching configuration using the same wavelength for both data and clock signals. The original data is split from the clock using polarisation couplers                          |

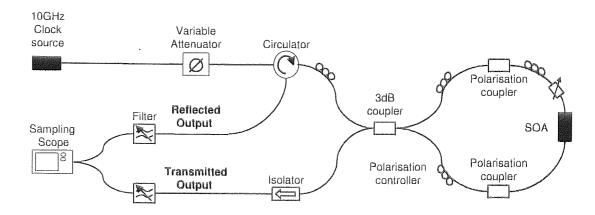

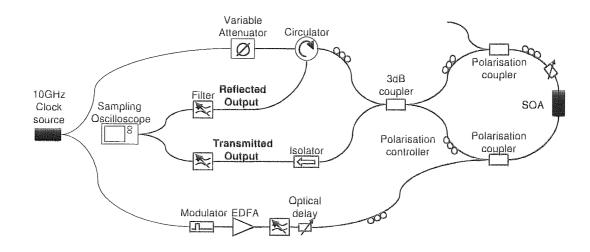

| Figure 2-3 Experimental setup used for self switching configuration results47                                                                                                                           |

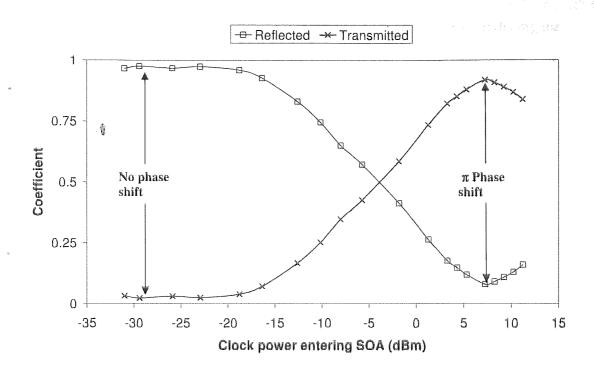

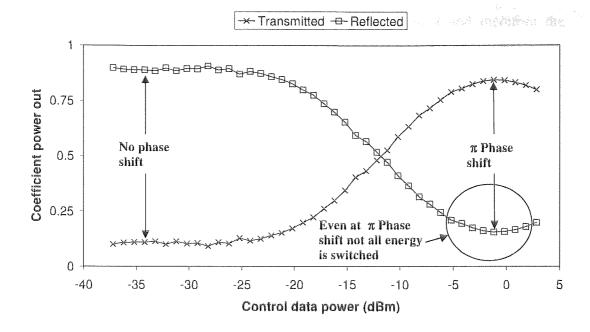

| Figure 2-4 Self-switching output co-efficient for increasing clock powers. As the clock power increases a phase shift is generated so the output is switched from the reflected to the transmitted port |

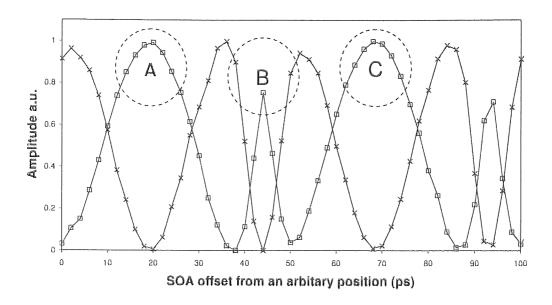

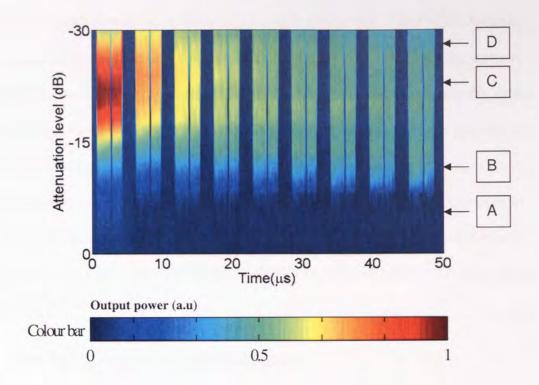

| Figure 2-5 Self-switching against SOA offset, "A" and "C" shows the SOA 25ps from the centre of the Sagnac loop, "B" shows SOA in centre of the Sagnac loop                                             |

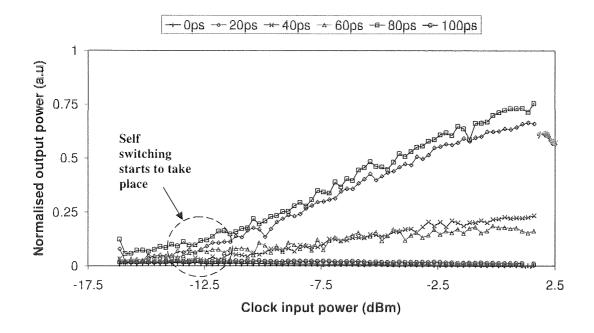

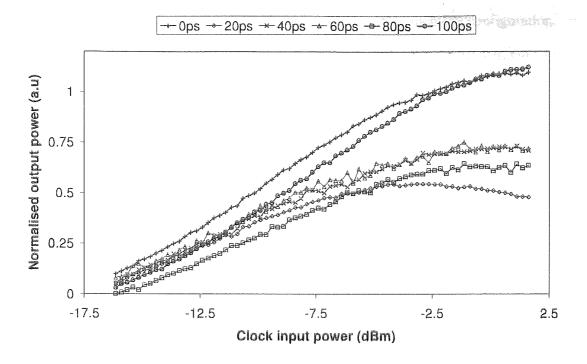

| Figure 2-6 Self switching transmitted outputs for various SOA offsets values of                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| τ                                                                                                                                                |

| Figure 2-7 Self switching reflected outputs for various SOA offset values of $\tau$                                                              |

| 53                                                                                                                                               |

| Figure 2-8 Schematic of the experimental TOAD54                                                                                                  |

| Figure 2-9 Measured transmitted and reflected coefficient for the controlled switching of a TOAD.                                                |

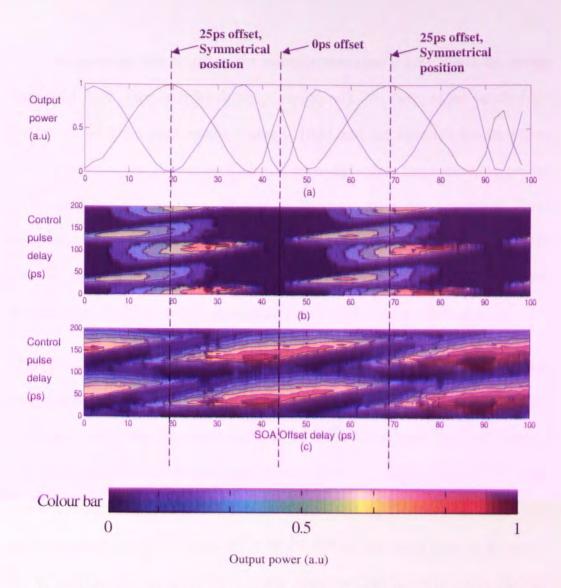

| Figure 2-10 Chart (a) shows the self-switching outputs for the reflected and                                                                     |

| the transmitted outputs, for varying SOA offsets. (b) Shows the                                                                                  |

| transmitted output map for varying offsets and control pulse delays, with (c) showing the output for the reflection                              |

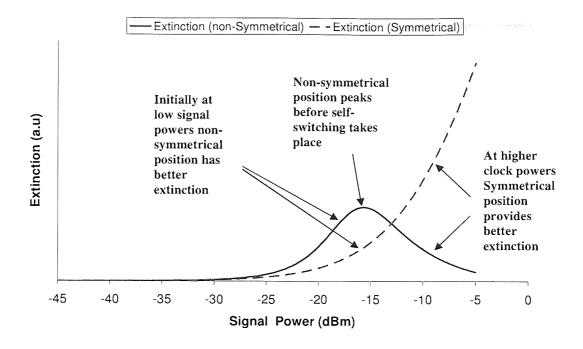

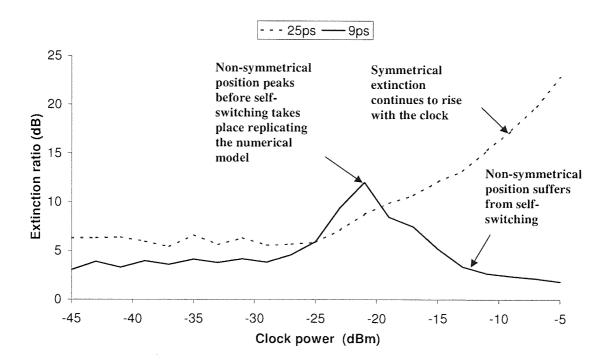

| Figure 2-11 Extinction ratio 10 Log E for varying clock powers for two values                                                                    |

| of $\Gamma$ showing the effects of self switching upon the extinction ratio62                                                                    |

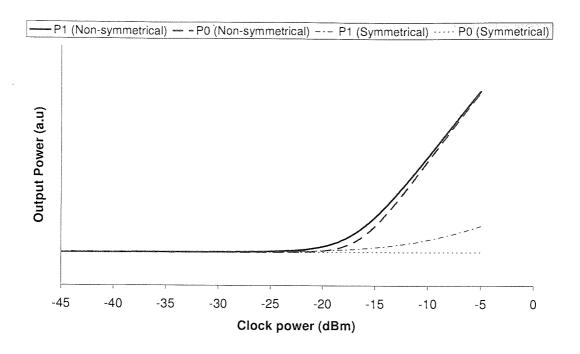

| Figure 2-12 Shows the values for $P_0$ and $P_1$ for the symmetrical and the                                                                     |

| nonlinear operating points against signal power63                                                                                                |

| Figure 2-13 Extinction ratios for varying signal input powers at 9 and 25ps offsets                                                              |

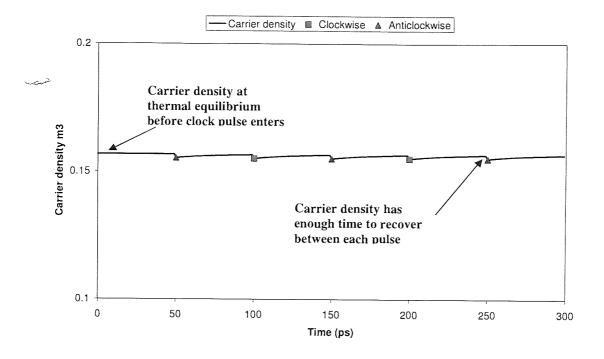

| Figure 2-14 Evolution of the SOAs carrier density when the clock is small enough to allow the carrier density to recover between each pulse66    |

|                                                                                                                                                  |

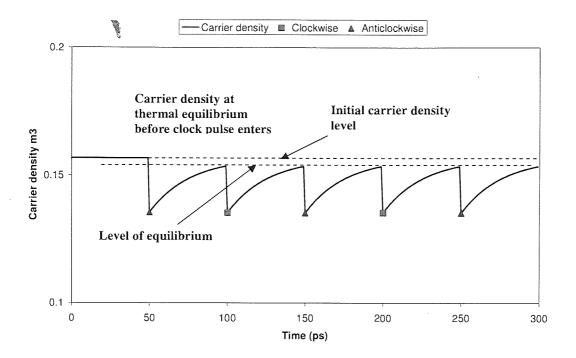

| Figure 2-15 Evolution of the SOAs carrier density when the clock is high enough not to allow the carrier density to recover between each pulse67 |

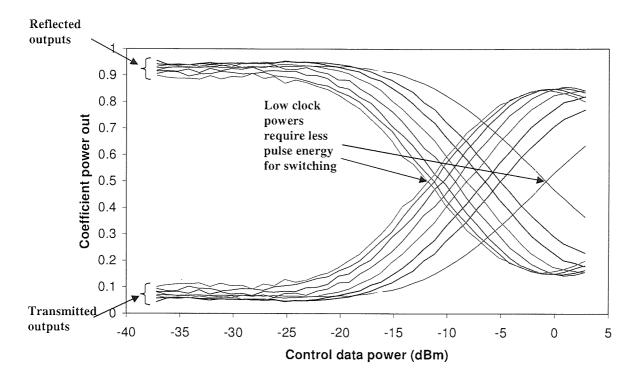

| Figure 2-16 Controlled switching for varying clock powers showing the reflected and transmitted outputs                                          |

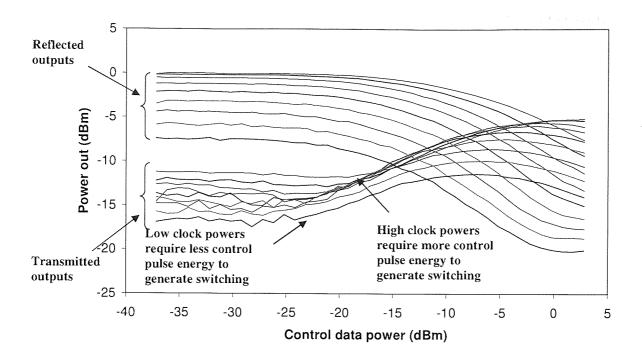

| Figure 2-17 Reflected and transmitted coefficients of switching for increasing                                                                   |

| clock powers. Low clock powers require less control pulse energies to                                                                            |

| provide switching69                                                                                                                              |

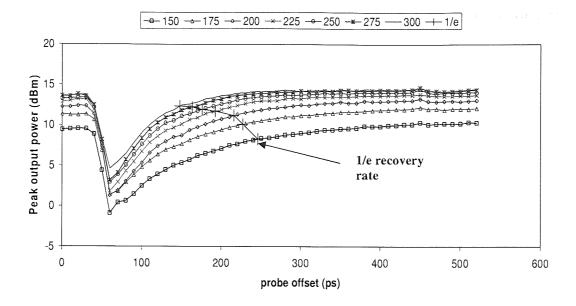

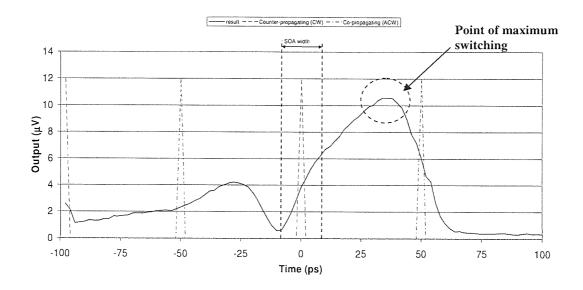

| Figure 2-18 Pump probe results showing the gain recovery of the SOA72                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-19 Plotted recovery time for 1/e for varying forward biasing currents                                                             |

|                                                                                                                                            |

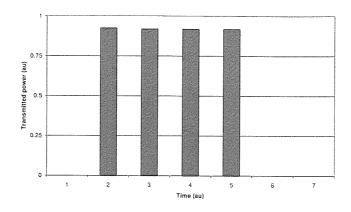

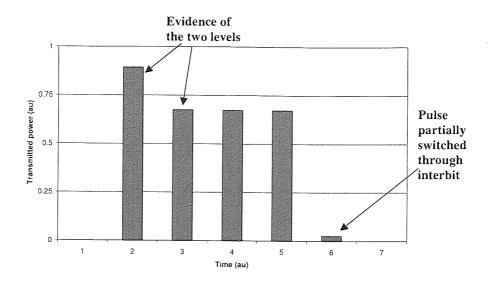

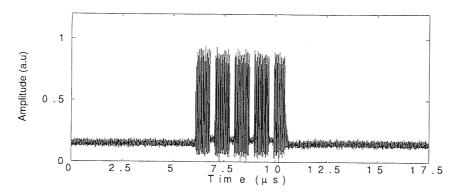

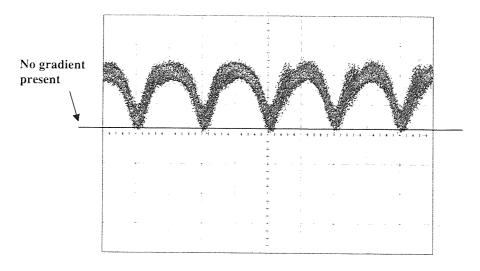

| Figure 2-20 Results of a four bit word (1111) switched out from a TOAD operating at 300ps slow enough for the SOA to fully recover between |

| each bit                                                                                                                                   |

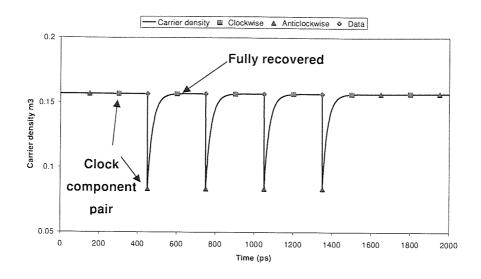

| Figure 2-21 Carrier density chart for the four bit word found in Figure 2-20                                                               |

| demonstrating complete SOA recover between bits                                                                                            |

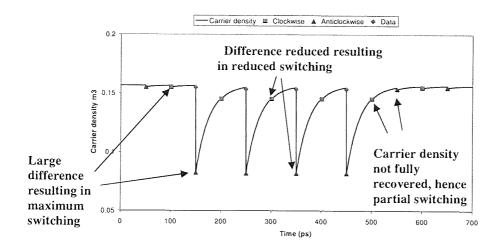

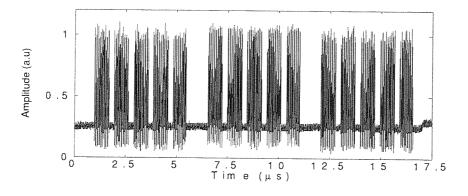

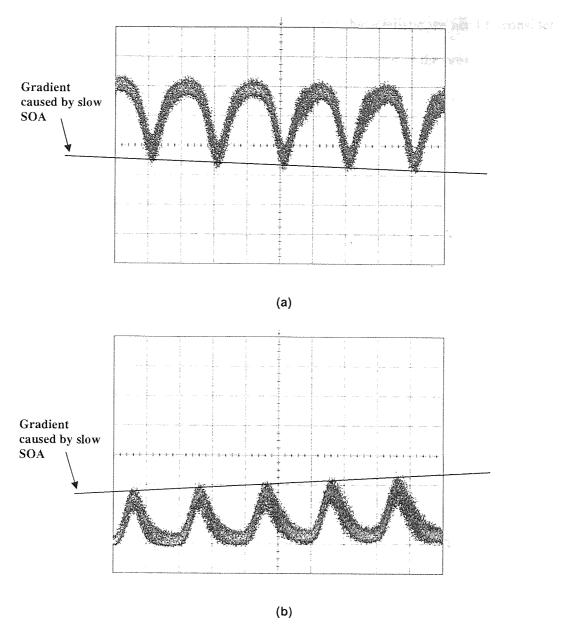

| Figure 2-22 Demonstration of a four bit word consisting of (1111) with a higher                                                            |

| bit rate 10GHz76                                                                                                                           |

| Figure 2-23 Carrier density map for a four bit word 1111 at a higher bit rate. 76                                                          |

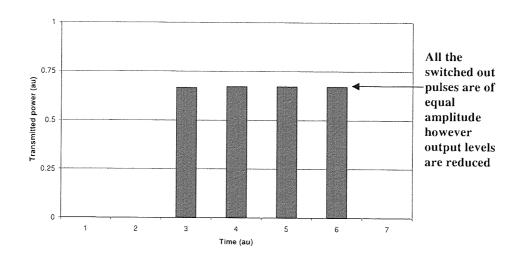

| Figure 2-24 Results of the TOAD operating at 10Gb/s using the four bit word                                                                |

| "1111" when the data pulse arrives before the clockwise pulse77                                                                            |

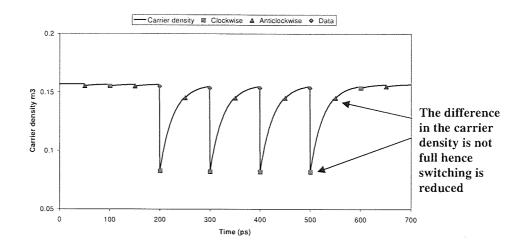

| Figure 2-25 Carrier density map showing the carrier density for the four bit                                                               |

| pattern with the data pulse arriving at the SOA at the same time78                                                                         |

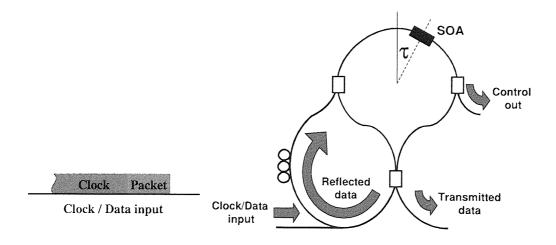

| Figure 3-1 Inverting shift register with the reflected port connected to the feedback                                                      |

| Figure 3-2 Switched output from the inverting memory device. After each                                                                    |

| circulation the data inverts82                                                                                                             |

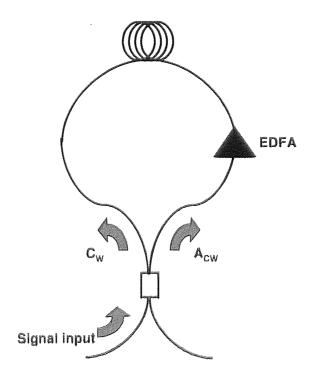

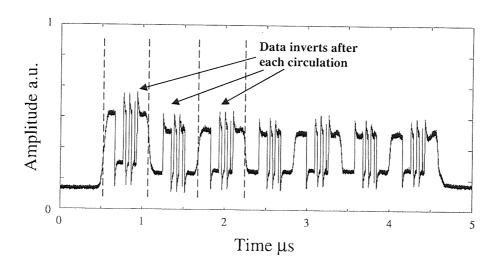

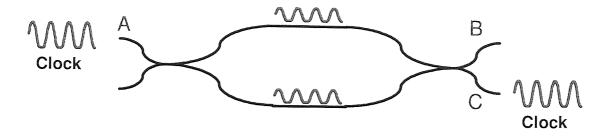

| Figure 3-3 Schematic of the non-inverting memory83                                                                                         |

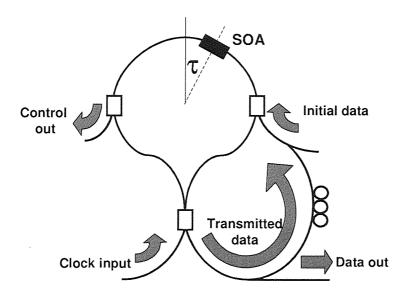

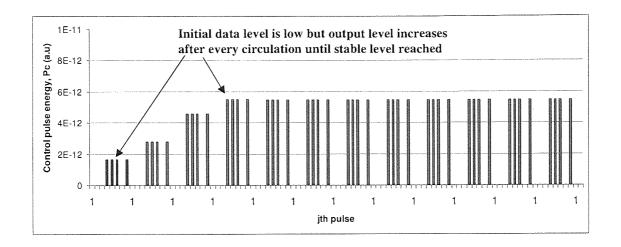

| Figure 3-4 Results for the basic numerical simulation for a device with a                                                                  |

| length of M = 8 bits86                                                                                                                     |

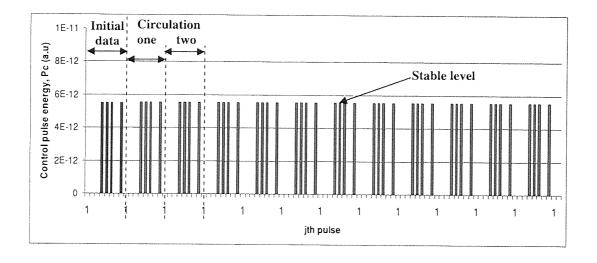

| Figure 3-5 Storage of the data for reduced data input87                                                                                    |

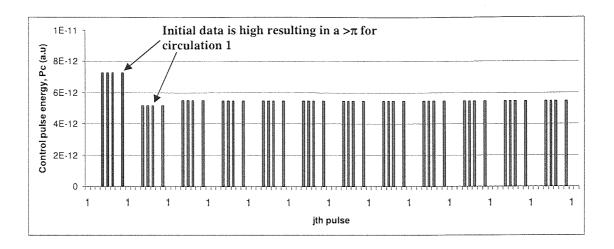

| Figure 3-6 Results showing high data input power. The initial data power                                                                   |

| results in a $> \pi$ phase shift resulting in a reduction in the output of                                                                 |

| circulation 1                                                                                                                              |

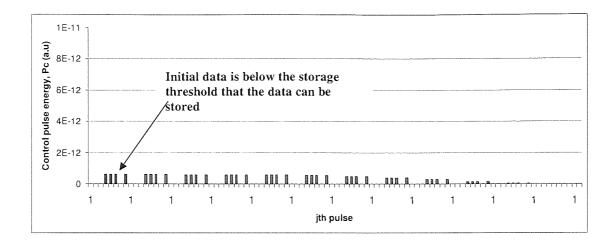

| Figure 3-7 Initial data power too low thus the data is not stored89                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------|

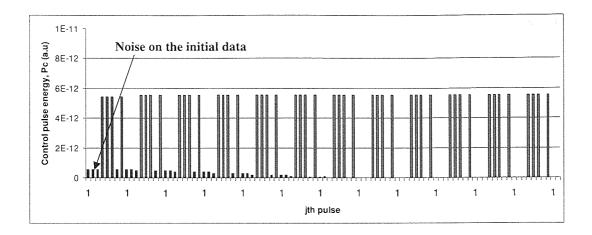

| Figure 3-8 Poor extinction ratio on the initial data. The noise is not above the threshold for storage hence no errors90                     |

| Figure 3-9 Demonstrating the effect of poor extinction ratio on the storage of data. Noise on the zeros is high enough for errors to occur90 |

| Figure 3-10 Data power is high enough but there is not enough gain in the feedback loop to allow for continuous storage91                    |

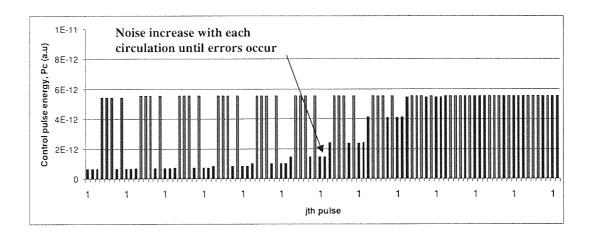

| Figure 3-11 High gain in the feedback loop causes a build up of the zero level leading to errors92                                           |

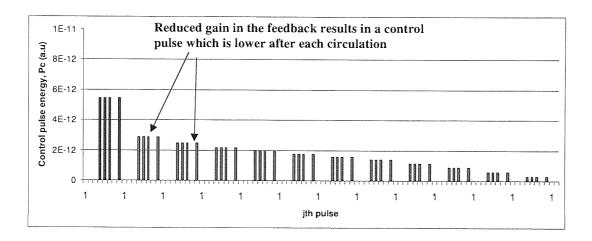

| Figure 3-12 Continuous storage with reduced gain showing reduced stabilisation level                                                         |

| Figure 3-13 Experimental schematic of the memory where reset is achieved by halting the clock pulse supply                                   |

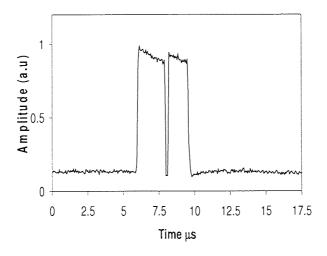

| Figure 3-14 Input clock95                                                                                                                    |

| Figure 3-15 Initial data input                                                                                                               |

| Figure 3-16 First TOAD output96                                                                                                              |

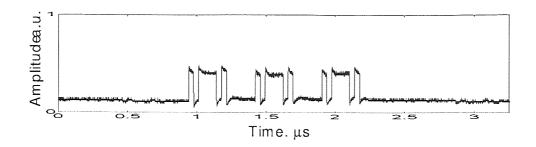

| Figure 3-17 Three circulations of storage97                                                                                                  |

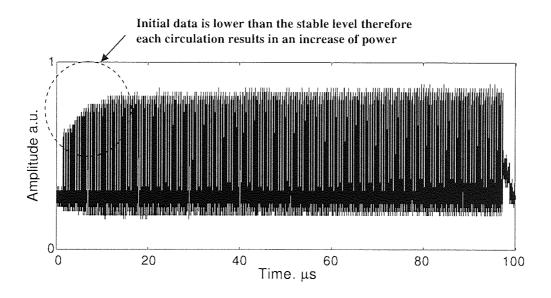

| Figure 3-18 Storage over 100µs97                                                                                                             |

| Figure 3-19 Data output after 100µs98                                                                                                        |

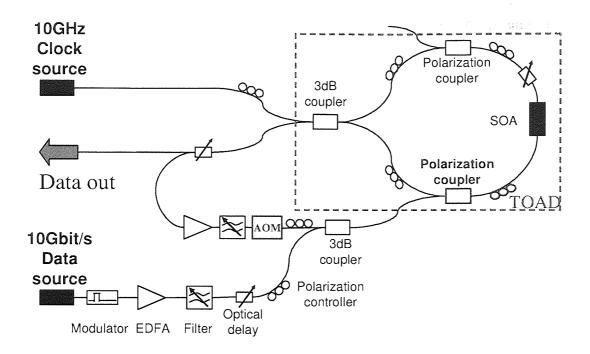

| Figure 3-20 Experimental setup using an AOM in the feedback loop to clear the data                                                           |

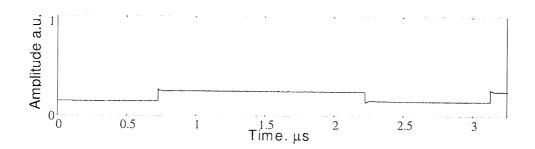

| Figure 3-21 The initial data packet consisting of 44k bits of data (equivalent to 4.4µs)                                                     |

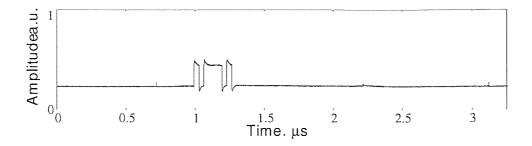

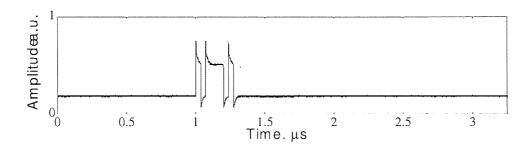

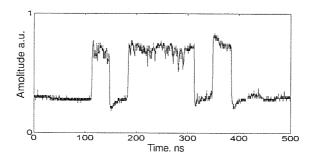

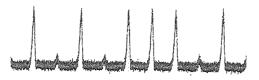

| Figure 3-22 The final three circulations of stored data after one second of storage time                                                     |

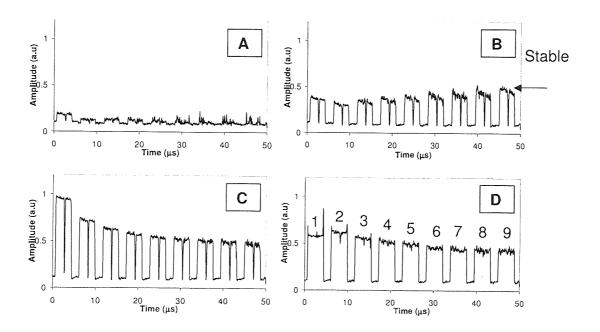

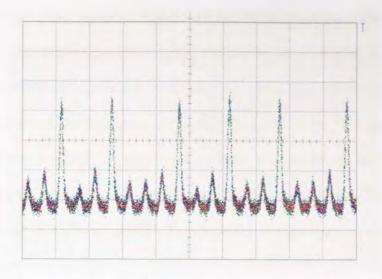

| Figure 4-1 Original data packet entering the device105                                              |

|-----------------------------------------------------------------------------------------------------|

| Figure 4-2 2D diagrams showing data stored for varying initial data input powers                    |

| Figure 4-3 3D chart showing change in original data input power107                                  |

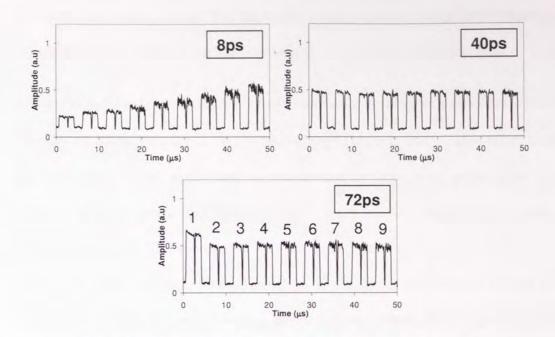

| Figure 4-4 2D results showing storage for various data input timings109                             |

| Figure 4-5 3D chart showing data storage with 100ps variation of the initial data input timing      |

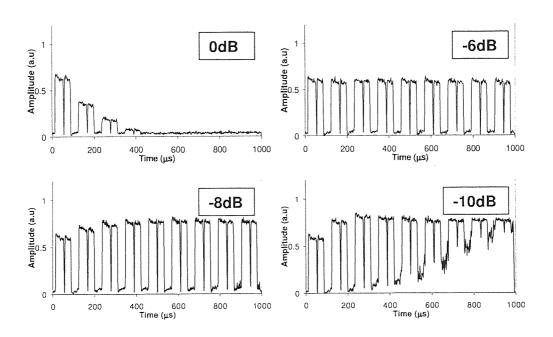

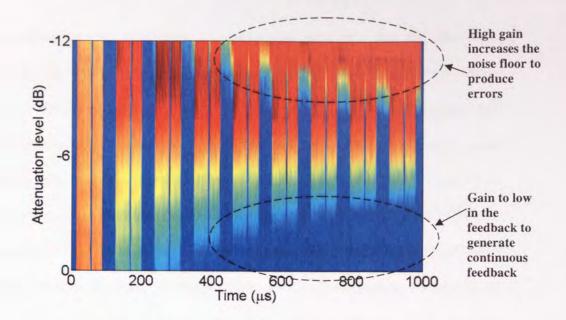

| Figure 4-6 2D diagrams for 0,-6,-8 and -10dB of attenuation111                                      |

| Figure 4-7 Variation in the feedback gain112                                                        |

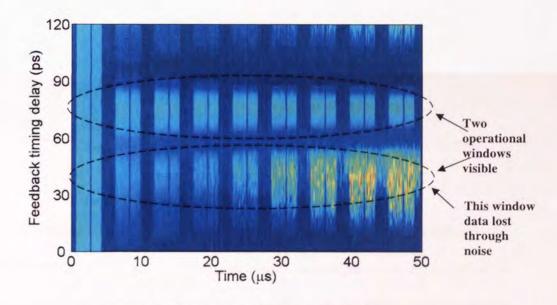

| Figure 4-8 Change in the feedback timing                                                            |

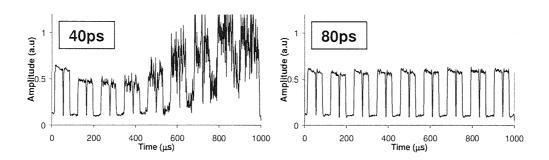

| Figure 4-9 2D results for 40ps and 80ps feedback timing115                                          |

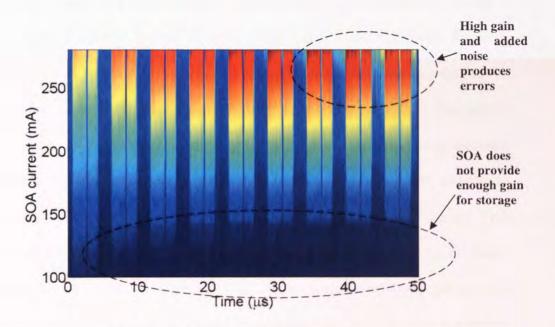

| Figure 4-10 Change in the SOA current116                                                            |

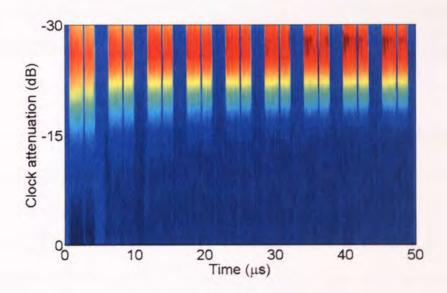

| Figure 4-11 Variation in the clock power118                                                         |

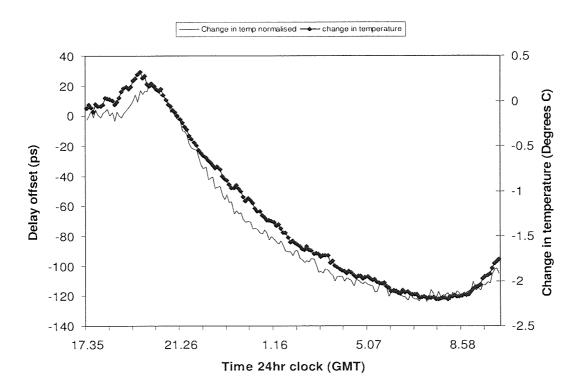

| Figure 5-1 Pulse delay through 1km of SMF fibre as a function of ambient air temperature over 12hrs |

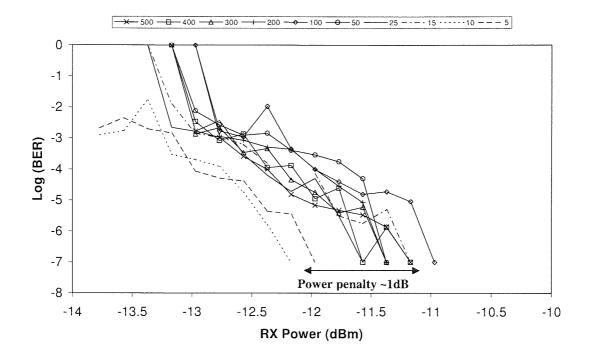

| Figure 5-2 BER curves for varying circulations                                                      |

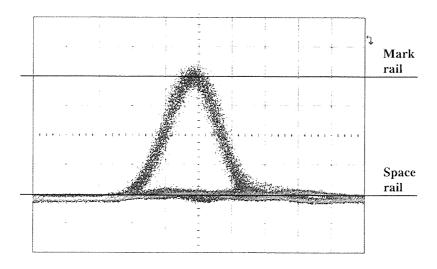

| Figure 5-3 Example eye diagram showing mark and space rail127                                       |

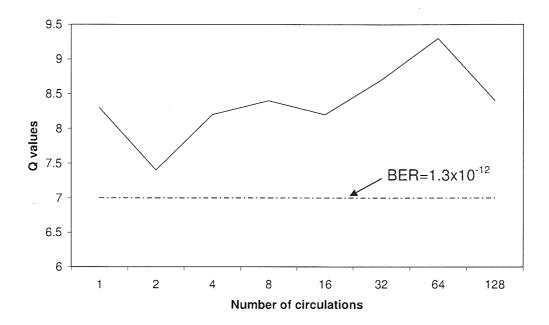

| Figure 5-4 Calculated Q values for varying circulations showing no deterioration of the data        |

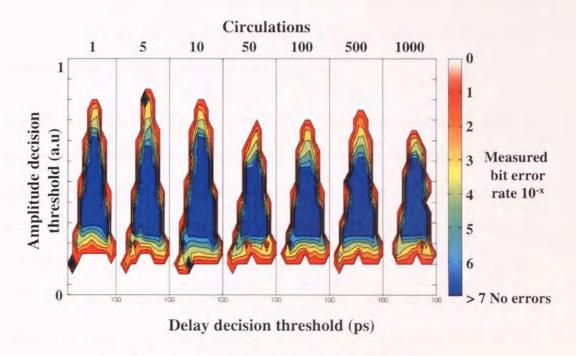

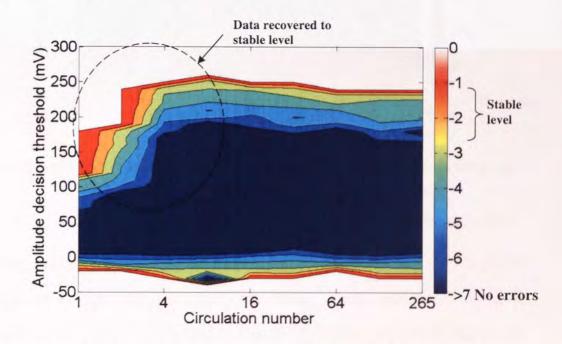

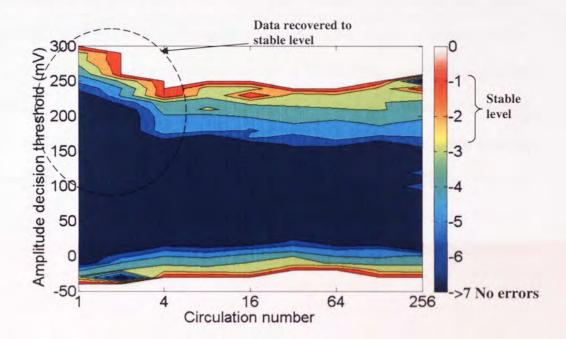

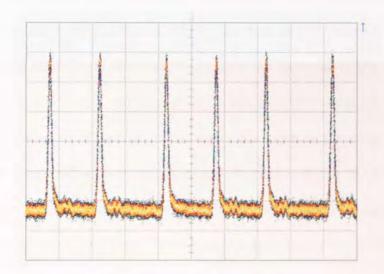

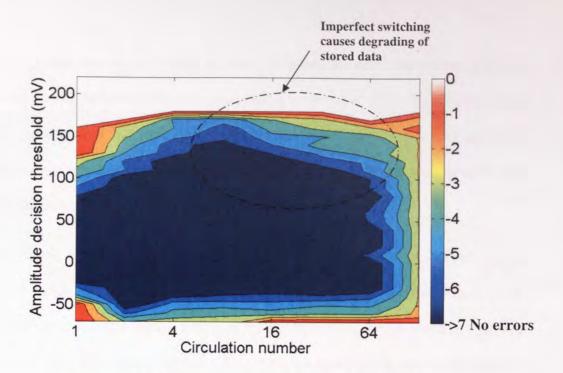

| Figure 5-5 3D bit error rate maps for different circulations130                                     |

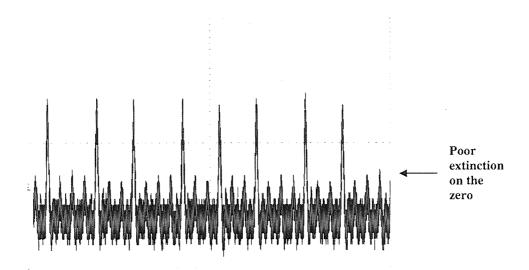

| Figure 5-6 Initial data to be stored at the reduced power and extinction ratio                      |

| Figure 5-7 3D bit error rate map of the initial data packet pulses before entering the device       |

| Figure 5-8 3D BER map of the pulses contained in the packet after 250 circulations                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-9 BER Amplitude threshold of the initial data before entering the loop                                                                        |

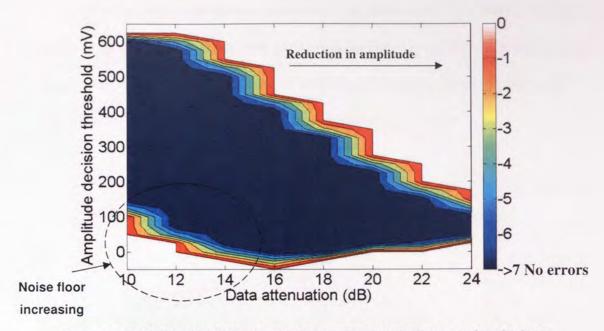

| Figure 5-10 BER amplitude threshold sweep for varying attenuation levels after the first circulation                                                   |

| Figure 5-11 BER amplitude threshold after 250 circulations for changing data attenuation                                                               |

| Figure 5-12 BER amplitude threshold sweep for varying circulations with a initial data input lower than stable level (data attenuation level of 23dB)  |

| Figure 5-13 BER amplitude threshold sweep for varying circulations with a initial data input higher than the stable level (data attenuation =14dB).139 |

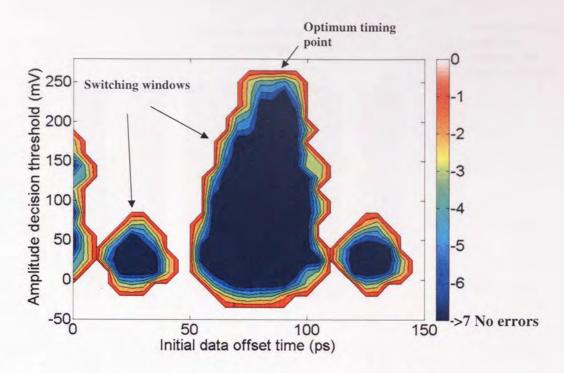

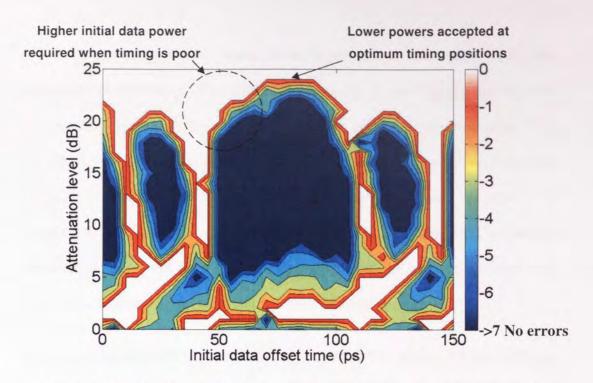

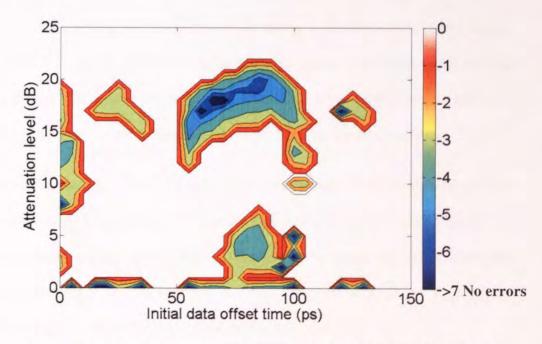

| Figure 5-14 Variation in the initial data input timing against BER threshold after the first circulation of storage                                    |

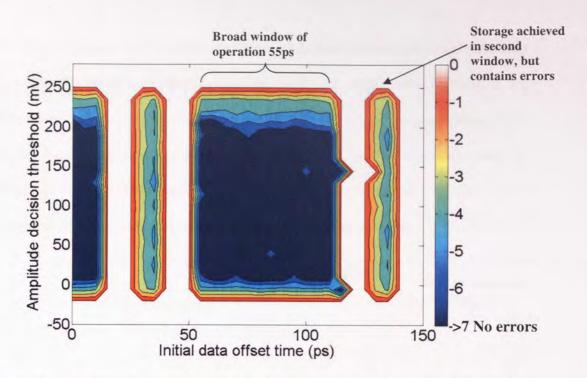

| Figure 5-15 Variation in the initial data input timing against BER threshold after 250 circulations                                                    |

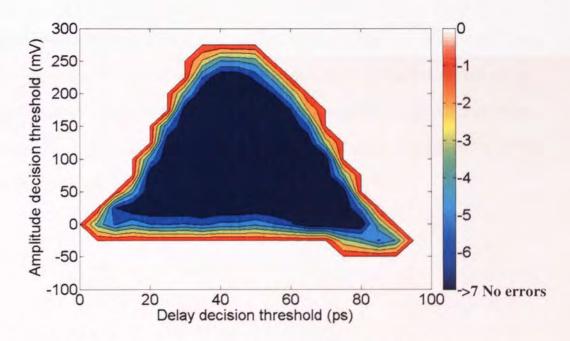

| Figure 5-16 TOAD operating window for varying data input timing offset for 3.3GHz data pattern                                                         |

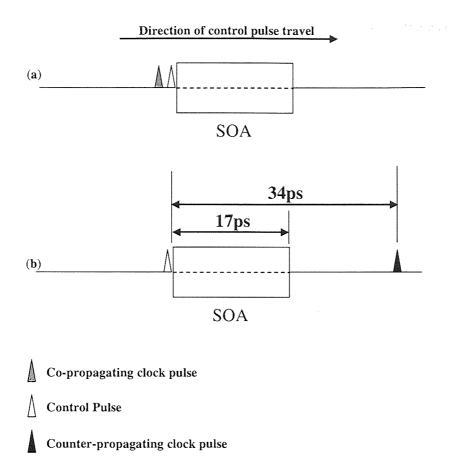

| Figure 5-17 Transit of the control pulses through the SOA a) Co-propagating and b) Counter-propagating clock pulses                                    |

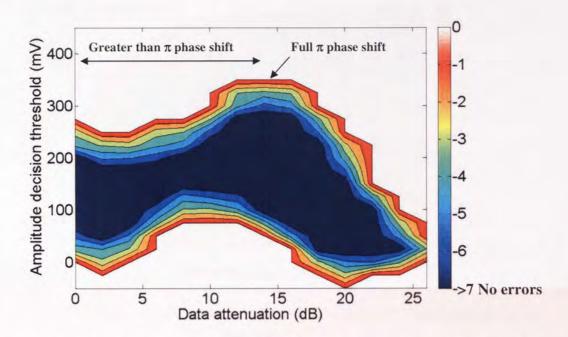

| Figure 5-18 BER chart for initial timing against initial amplitude for an initial good extinction ratio on the data packet after 250 circulations      |

| Figure 5-19 Initial data input with good extinction147                                                                                                 |

| Figure 5-20 Initial data input with poor extinction of ~1:3149                                                                                         |

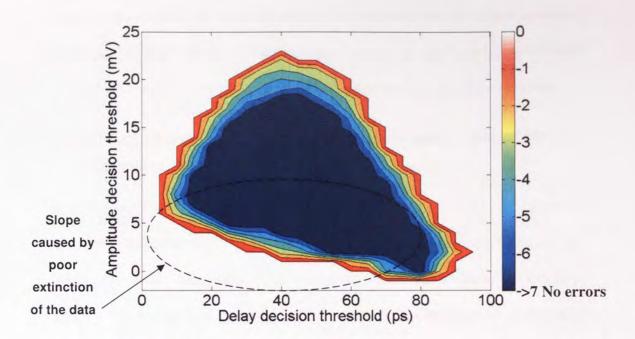

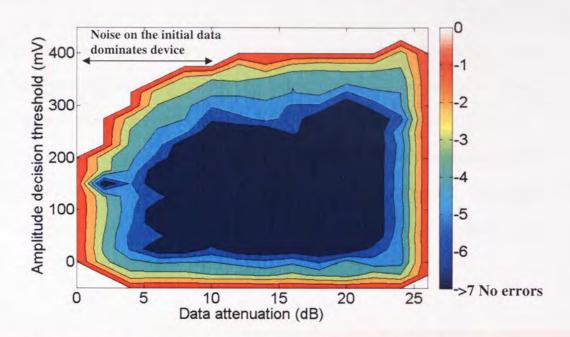

| Figure 5-21 BER chart for initial timing against initial amplitude for an poor extinction ratio on the initial data packet after 250 circulations |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

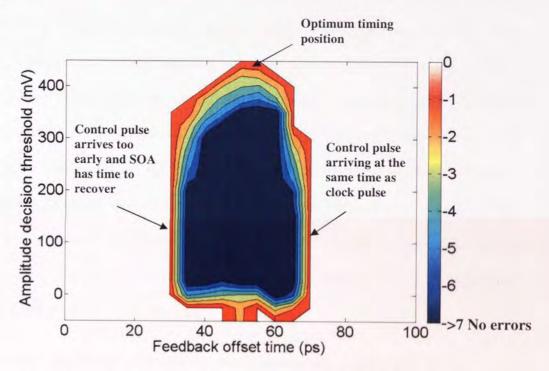

| Figure 5-22 Variation in the initial feedback timing after 250 circulations151                                                                    |

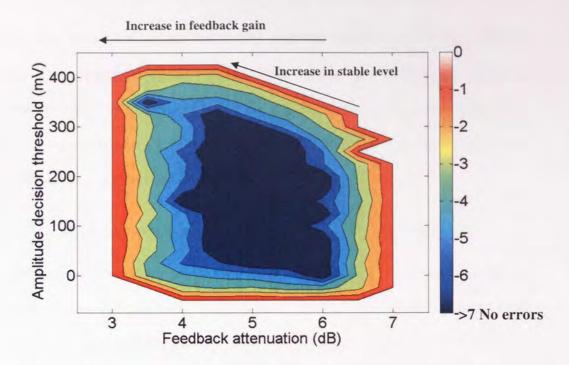

| Figure 5-23 Variation in the feedback attenuation after 250 circulations153                                                                       |

| Figure 5-24 BER amplitude threshold sweep for varying SOA currents after 250 circulations                                                         |

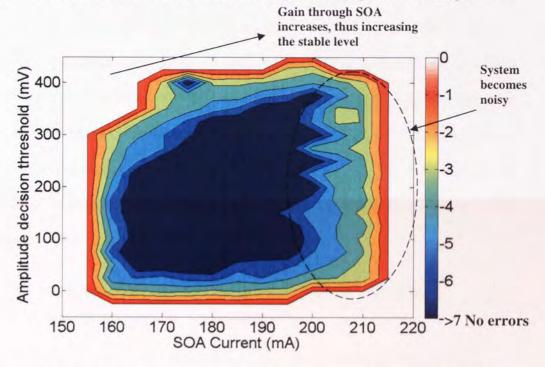

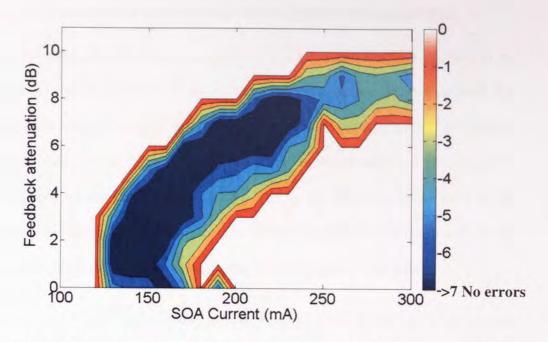

| Figure 5-25 BER map for a change in SOA current and feedback attenuation after 250 circulations                                                   |

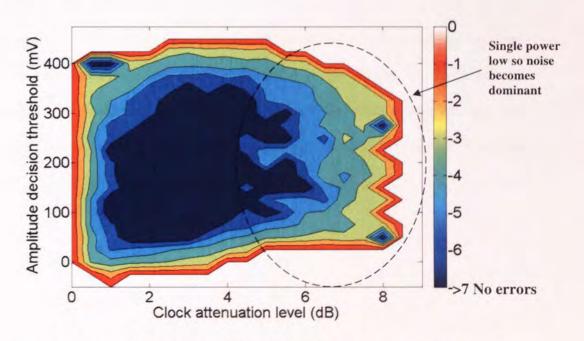

| Figure 5-26 Characterisation sweep for varying clock attenuation levels after 250 circulations                                                    |

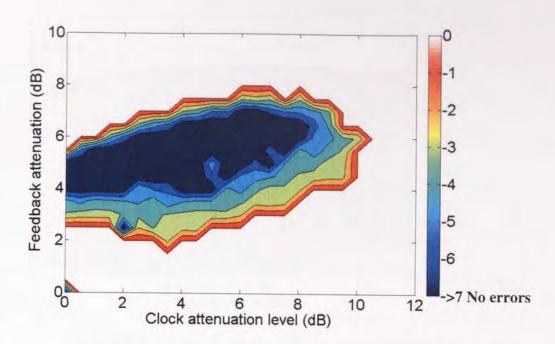

| Figure 5-27 Characterisation sweep for clock attenuation against feedback attenuation levels                                                      |

| Figure 5-28 Deterioration of data quality for 5GHz operation161                                                                                   |

| Figure 6-1 Light entering A will exit through port C when there is no differential phase shift.                                                   |

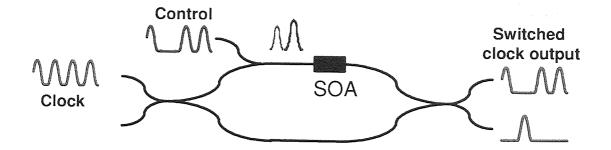

| Figure 6-2 The addition of the SOA as the non-linear element enables switching using a control signal                                             |

| Figure 6-3 Mach-Zehnder interferometer output when CW clock is switched out using RZ data pulses165                                               |

| Figure 6-4 Mach-Zehnder interferometer with the combination of two SOA to form a push-pull configuration                                          |

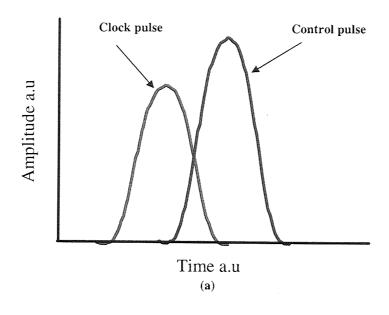

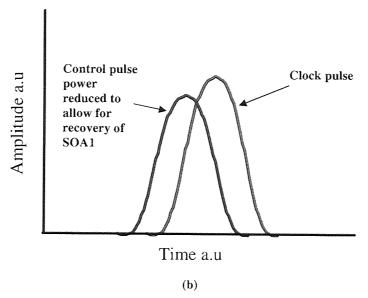

| Figure 6-5 Picture showing the transit of the control and the clock pulse through a) SOA1 and b) SOA2                                             |

| Figure 6-6 Output of a Mach-Zehnder interferometer using push-pull and CW clock input                                                             |

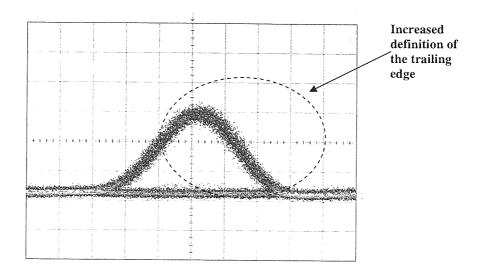

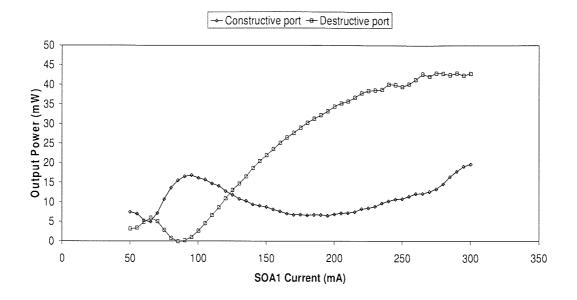

| Figure 6-7 Output from the non push-pull Mach-Zehnder interferometer when    |

|------------------------------------------------------------------------------|

| five "1"s are switched out after a block of Zeros. (a) Is the normally       |

| constructive output (b) is the normally destructive output170                |

| Figure 6-8 The output from the Mach-Zehnder using two SOAs in push-pull      |

| configuration when five "1"s are switched out after a block of Zeros. (a) Is |

| the normally constructive output (b) is the normally destructive output 172  |

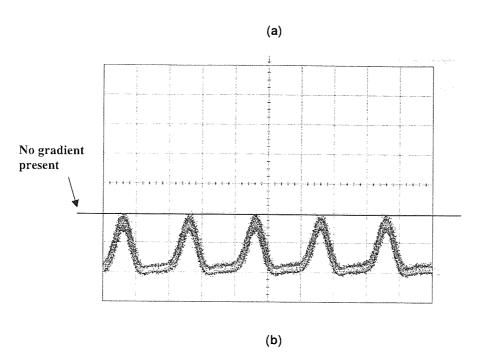

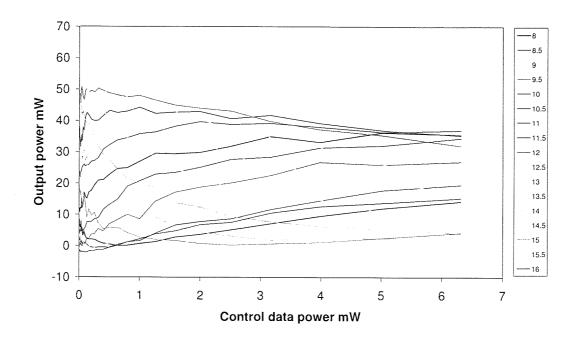

| Figure 6-9 Output from both arms as the current is varied in one of the SOAs |

| 173                                                                          |

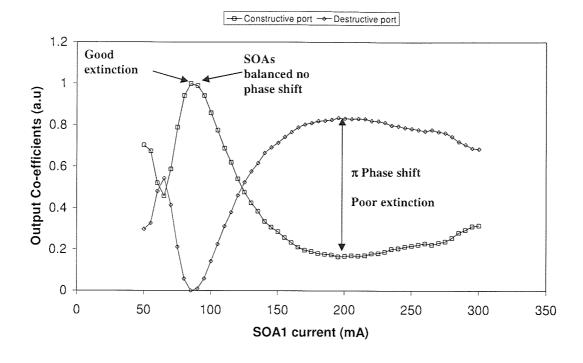

| Figure 6-10 Coefficient of output power as a function of SOA current174      |

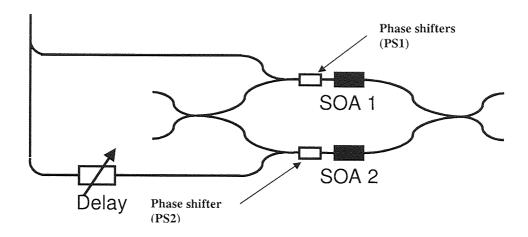

| Figure 6-11 Mach-Zehnder interferometer with phase shifters included 175     |

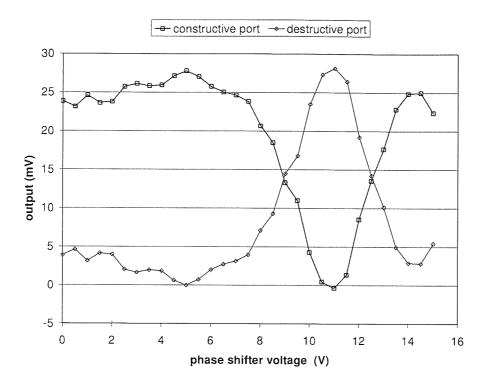

| Figure 6-12 Constructive and destructive outputs for changes in voltage to   |

| PS1176                                                                       |

| Figure 6-13 Switching coefficients for the Hybrid Integrated Mach-Zehnder    |

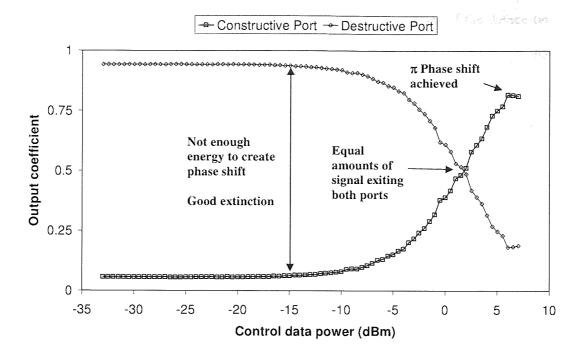

| interferometer177                                                            |

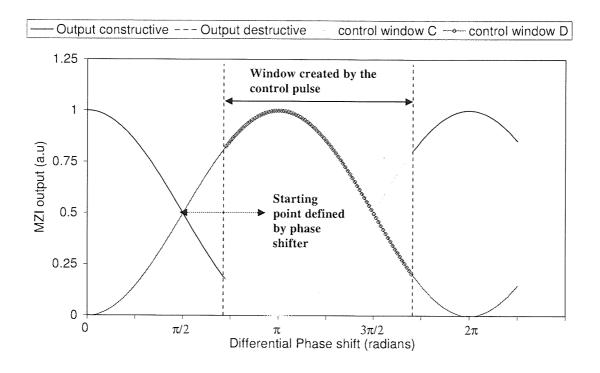

| Figure 6-14 Theoretical chart demonstrating the link between the phase       |

| shifters and the differential phase shift generated by the control pulse 178 |

| Figure 6-15 Output of one of the arms with various voltages applied to the   |

| phase shifters179                                                            |

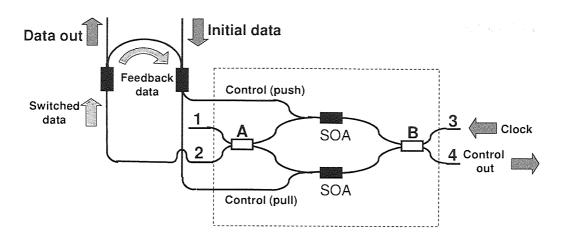

| Figure 6-16 Schematic diagram of the non-inverting memory using a Mach-      |

| Zehnder interferometer180                                                    |

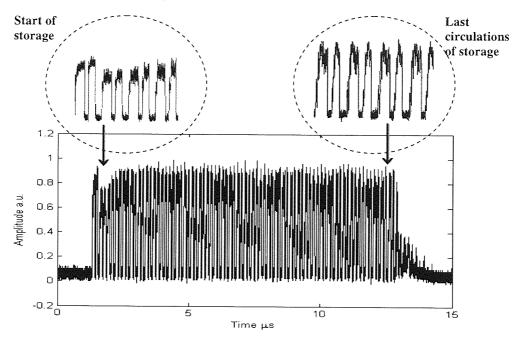

| Figure 6-17 Oscilloscope trace showing operation of the Mach-Zehnder non-    |

| inverting memory181                                                          |

| Figure 8-1 Initial data input of a 10Gb/s signal to be stored205             |

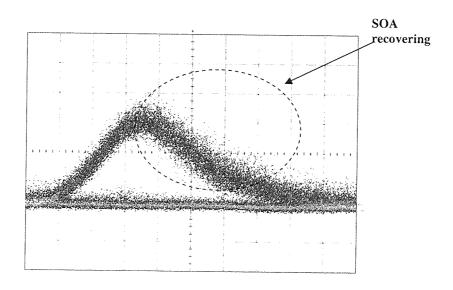

| Figure 8-2 1st circulation of 10Gb/s data showing modulation caused by slow  |

| SOA recovery205                                                              |

| Figure 8-3 2nd circulation of 10Gb/s data showing further degrading of the signal                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------|

| signal                                                                                                                                 |

| Figure 8-4 3rd circulation of 10Gb/s data quality of the data has reduced further                                                      |

| Figure 8-5 Further reduction in quality after 4 circulations of a 10Gb/s signal                                                        |

| 206                                                                                                                                    |

| Figure 8-6 5th circulation using 10Gb/s data and the pulse affected by modulation has almost reduced to the same level as the zeros206 |

| Figure 8-7 6th circulation using a 10Gb/s data and the data is completely lost through the continuous modulation effects               |

#### 1. Introduction to optical communications

#### 1.1. Introduction

One of the earliest and most notable events in the history of telecommunications was the laying of the first transatlantic telegraphy cable in 1858. Although this cable provided the first quai-instantaneous (as compared to post) communication link across the Atlantic, it took 2 minutes to send a single word [1]. After three weeks of operation, during which four hundred messages had been sent, the line finally fell silent. Since this major milestone in communications, many advances have been made using different technologies, notably the Guglielmo Marconi first transatlantic commercial radio transmission service in the 1900s [2] and the launch of the first commercial satellite Telstar in 1962 [3].

Since the 1950s the benefits of using light as a transmission median had been understood. It was during the 1970's, however, that the demand for extra capacity led to the discovery that light could be propagated along a fibre with a loss of less than 20dB/km. With the new improved fibre and the advancements of optical amplifiers, ultra fast optical communication became a reality [4].

In comparison to the move of long haul data transmission from the traditional "copper twisted pair" (which has been the backbone of the telecommunications industry for most of the 20<sup>th</sup> Century), to optical transmission, pre and post transmission processing of the signals is still dominated by electronics. Although processing using electronics is well established and understood it has two major disadvantages. Firstly the speed of the electronics is limited by the switching speed of a transistor, which in high-speed optical terms is relatively slow. In addition this actual process of

transferring a signal from optical to electrical and visa versa produces serious performance bottlenecks [5]. It is these disadvantages that have brought about the interest in all-optical processing [6].

To understand where all-optical processing fits into a high-speed all optical network it is essential to understand some basic system details.

#### 1.2. Optical fibre

A basic optical transmission system consists of three individual components a transmitter, a transport medium and a receiver. The initial component is the transmitter, which converts the payload data to an optical signal that is suitable for optical transmission. The modulated optical signal containing the data, generated by the transmitter, is then sent through a waveguide (typically doped silica fibres) to transport the light signal to its final destination. Finally once the modulated signal has reached its destination the receiver then decodes the received signal and extracts the original data [7, 8].

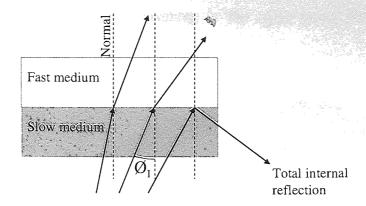

As the name suggests, a waveguide guides a wave of light in a desired direction. In a modern high capacity optical network this is normally achieved through the use of optical fibre. It is well documented that all optical fibres rely on a phenomenon known as total internal reflection, to contain and direct the propagating light [9-11].

Figure 1-1 Total internal reflection occurs when the angle of incidence  $(\emptyset_l)$  is equal to or greater than the critical angle.

Optical fibres are made up of two main components: the core, where most of the light propagates; and a cladding, which surrounds the core. The refractive index (which is the ratio of the speed of light in a vacuum and the speed of light in the subject material, a higher index corresponds to a slower medium) of the core is higher than the cladding allowing for total internal reflection to take place. In an optical fibre the critical angle  $\emptyset_c$ , required for total internal reflection, is dependant upon the refractive index of both the core and the cladding and can be calculated as [11]:

$$\emptyset_c = \sin^{-1} \left( \frac{n_2}{n_1} \right) \tag{1.1}$$

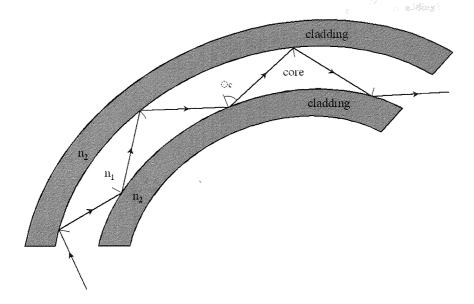

Where  $n_1$  and  $n_2$  represent the refractive index of the fibre core and the fibre cladding respectfully. Any angle of incidence greater than  $\emptyset_c$  will cause the light to reflect inward and therefore be contained within the fibre, hence providing this condition is maintained it is possible to guide light around a bend. Figure 1-2 shows that even though the fibre is curved, providing the bend radius is large enough, light can be guided around a corner using multiple total internal reflections [9]. As the radius is reduced, however, the incident angle is reduced and therefore light will escape the

waveguide causing "bend loss", resulting in the signal being attenuated and a reduction in the received power.

Figure 1-2 Light entering one end of a curved fibre will propagate using internal reflection and exit at the opposite end

The refractive index, or the speed at which light travels through a medium, is dependant upon the material. Usually in optical transmission fibres the core and cladding are made primarily of silica (SiO<sub>2</sub>), having a nominal refractive index of 1.45. To allow for total internal reflection the core and cladding must be different and this is usually achieved by doping the core with a few percent of Germanium (Ge) [12].

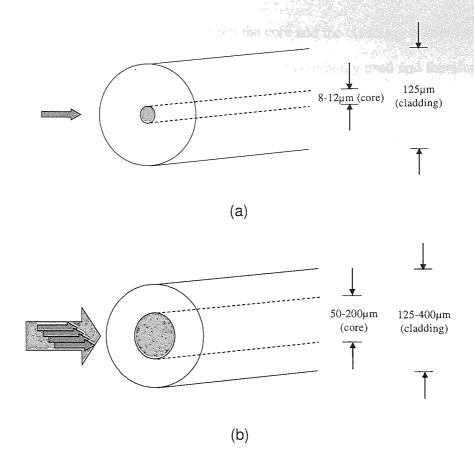

Although some of the propagating light can be found in the cladding, the signal is mainly transmitted through the core. There are two main categories of optical fibre which are classed as either single mode, commonly used in modern systems, or multimode, as can be found in earlier systems [13]. The category to which a fibre belongs is largely dependent upon the size of the core see Figure 1-3.

Figure 1-3 Propagation of singlemode (a) and multimode (b) fibres and typical dimensions

The terms multimode and singlemode are derived from the number of fundamental modes that a fibre uses to transfer light. With multimode fibre the light is transferred through a collection of spatial transverse modes unlike a single mode fibre that uses only one mode Figure 1-3. Whether a fibre is single mode or multimode is determined by the V parameter, which can be defined for a perfect "step-index" core as [14]:

$$V = \frac{2\pi a}{\lambda} \sqrt{n_1^2 - n_2^2} \tag{1.2}$$

Where a is the fibre radius,  $\lambda$  represents the wavelength of the incident light. Single mode fibres, as the name suggests, have only one fundamental mode. Consequently, for a single mode fibre to exist it must satisfy the condition of V < 2.405 [15]. This requirement can be easily achieved, providing the core diameter is kept small and the

difference in the refractive index, between the core and the cladding, is kept low. It is the Single Mode Fibre (SMF), which is now most commonly used and therefore will be used for the rest of this thesis.

#### 1.3. Digital transmission over optical fibres

The ability to send light long distances is not very useful, in a communications environment, unless the light can be modulated to contain data. There are two main categories of modulation: analogue and digital [16]. In optical communications the preferred modulation technique is normally digital. This method was elected for the same reasons that other transmission media such as radio and copper wire have selected it, for instance the technique is resilient to noise.

One of the most popular and simplest ways of transmitting data digitally through fibre is by using On Off Keying (OOK), where the data consists of a sequence of "0"s and "1"s. When data is applied to a pulse train the absence of light within a bit slot represents a "0" and the presence of light within a bit slot represents a "1".

Figure 1-4 10Gb/s (a) Non-Return to Zero (NRZ), (b) Return to Zero (RZ), modulation formats

The modulation technique OOK, can be broken down into two further categories, Non-Return to Zero (NRZ) and Return to Zero (RZ), Figure 1-4 [17]. The NRZ modulation scheme is generally more common than the RZ format. To create a NRZ signal, data is modulated directly onto a Continuous-Wave (CW), Figure 1-4 (a). Again the presence of light ensures a "1" and the absence of light ensures a "0", with the light filling the whole length of the bit slot. Hence, when there are two simultaneous "1"s the signal level does not return to zero. With the RZ format the data is modulated onto a pulse stream, Figure 1-4 (b), usually consisting of gaussian pulses. In this scheme the intensity always returns back to zero. Both the switching devices that are to be used later in this research can only operate when RZ signals are used. Therefore, it is the RZ modulation technique that will be used for the rest of this thesis.

Other modulation schemes include Differential Phase Shift Keying (DPSK) [18, 19] and Quadrature Phase Shift Keying (QPSK) [20], which utilise RZ pulses but unlike

OOK the amplitude remains constant and the phase of the pulses is modulated with the data.

A transmitter will modulate the data onto an optical signal, which then propagates along a transmission medium until it reaches its destination. Once its destination has been reached, a receiver converts the optical data into electrical pulses ready for processing. The receiver achieves this by measuring the intensity of the light at a set timing point for each bit. Once the amplitude has been measured the receiver then has to make a decision as to whether the bit represents a "1" or a "0". To help the receiver make this decision it is provided with a decision threshold level, where pulses measured lower than the threshold level represent a "0" and pulses measured above the threshold level represent a "1". The level at which the decision threshold is set is critical to reduce the numbers of errors received, for instance if the threshold was too low then a "0" could read as a "1" and if the threshold level was too high then a "1" could be read as a "0", hence giving rise to errors.

The extinction ratio is a measure of how much power is in a "1" bit compared to the power in a "0" bit [21]. This is expressed as

$$Ex = \frac{P_1}{P_0}$$

(1.3)

Where  $P_1$  and  $P_0$  represent the power in a "1" bit and a "0" bit respectively. To provide the maximum potential for recovery of data at the receiver, it is desirable to have an infinitely large extinction ratio. However, in reality this is not possible as most sources and modulators generate a non zero optical power output for "0" bits.

To keep the errors received to a minimum it is essential to provide the best quality signal possible. One of the fundamental reasons for a reduction in signal quality is

noise. The noise in a transmission system can come from any of the main components: the transmitter (Laser intensity noise); the transport medium (Crosstalk and Amplified Spontaneous Emission (ASE)) and the receiver (Thermal noise and Quantum noise) [22]. All of these sources of noise reduce the signal quality at the decision point and can potentially cause errors. The proportion of the signal power to noise power is measured as the Signal to Noise Ratio (SNR).

The total noise in a system is a stochastic process which is a combination of both multiplicative and additive components. Multiplicative noise components such as laser intensity noise [22] are only produced in the presence of a signal and additive noise, such as ASE, is produced independently of the presence of a signal.

If the input power to the transmission line is too low and the noise at the receiver is too high then through degradation effects, such as attenuation (section 1.4), the resultant signal present at the receiver is low enough to cause a "1" to be read incorrectly as a "0". Likewise if the input signal power is too high then non-linear effects become prominent, degrading the signal hence increasing the probability of errors (section 1.6). It is these degradation effects which require that the optical signal powers in the network are finely balanced to ensure the probability of receiving an error is kept to a minimum.

#### 1.4. Signal degradation effects in optical fibres

When an optical signal propagates along a length of fibre the signal received is never the same quality as that transmitted. The process of signal propagation can cause degradation effects such as pulse shaping (as caused by dispersion) or nonlinearity. All of these degradation effects can contribute to the generation of errors at the receiver and thus limit the bit rate-distance product. The effect of degradation is

partially reduced through the introduction of repeaters and signal amplifiers situated at various locations along the transmission fibre. After travelling a specified distance the signal enters a repeater where the pulses are regenerated and amplified before retransmission. Once the regenerated signal exits the repeater it will then continue its propagation along the fibre until it reaches its destination or the next repeater. Repeaters greatly add to the cost of installation and operation of a system [23]. In addition each amplifier located in the repeaters adds self-generated noise in the form of ASE and thus limits the total number of amplifiers, which can be used in a system. Therefore, it is desirable to minimise the degradation effects influencing a propagating signal, thereby increasing the distance that a signal can propagate unaided and hence reduce the number of repeaters required.

Degradation effects are classified as linear and non-linear. The former of the two includes attenuation, which occurs as a result of the losses of the fibre. Attenuation is not dependant upon the signal intensity as opposed to the non-linear effects, such as Four Wave Mixing (FWM) [24] and Self Phase Modulation (SPM) [25].

Due to the short lengths associated with the devices demonstrated in this thesis, the effects of signal propagation are not a salient consideration. However, it is necessary to be aware of the mechanisms, which affect the optical signals. This will provide an understanding of the choice of wavelengths used for telecommunications and the benefits gained from using a regenerative device.

#### 1.4.1. Attenuation

One of the most important considerations when designing an optical based telecommunication system is attenuation. Power is lost simply through the cladding (i.e. bend loss) or through effects such as Raleigh backward scattering [23] or through

normal absorption. Every length of fibre has its associated loss that is normally measured in units of dB/km. Typical values for loss in silica in 1966 measured 1000dB/km. However, during the 1970s through constant development in the purification of silica fibres this value was reduced to approximately 0.2dB/km [26].

Figure 1-5 Loss spectrum of Single Mode Fibre (SMF) demonstrating wavelength dependant loss mechanisms

Attenuation is wavelength dependant, and therefore the correct wavelength must be chosen to reduce the amount of propagation loss, thus improving the efficiency of the system and reducing the amplification needed. Figure 1-5 shows a typical loss profile for SMF. The graph shows how the four main attenuation influences, Raleigh Scattering, Ultraviolet Absorption, Waveguide imperfections and Infrared Absorption change with wavelength. It is seen from the graph that the window for minimum loss is around 1550nm. The telecommunications industry widely uses wavelengths from 1530nm to 1565nm and this is the International Telecommunication Union ITU-T standard range known as the C band [27]. It is therefore around these wavelengths that the experiments contained in this thesis will be based.

#### 1.5. Chromatic dispersion