The Design of a Real Time, Fault-Tolerant, Multiprocessor System.

Volume 1 of 2.

Timothy Edwin Sharp.

Submitted for Ph.D. Degree. The Computer Centre, The University of Aston in Birmingham. June, 1983.

1

i

The University of Aston in Birmingham

Summary

The Design of a Real Time, Fault-Tolerant Multiprocessor System. Thesis submitted for Ph.D. Degree, 1983. Timothy Edwin Sharp.

It is essential that real-time computers should be reliable. The majority of methods used to achieve fault tolerance in such systems employ a substantial duplication of hardware. This thesis suggests an alternative approach by placing a greater emphasis on firmware.

It is shown that a greater degree of control can be obtained in a microprogrammed computer. Furthermore, this control can often be maintained after a component failure. The use of bit-slice components is proposed as a suitable medium for the implementation of such a microprogrammed, fault-tolerant system.

It is also suggested that it is useful to overlay a high level language onto the microcoded system. A suitable language, Concurrent Pascal, is outlined. The architecture of the bit-slice processor, which has been built and tested, is described.

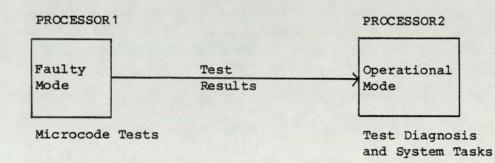

A set of tests, performed at microcode level, to diagnose a fault are proposed. It is shown that these tests depend upon the cooperation of another error-free processor within the system. The special problems which occur when running microcode on a faulty processor are also discussed.

The final chapter concludes that the use of microcode to achieve fault-tolerance can reduce the amount of hardware required. Suggestions for further research are also included.

Keywords: Bit-slice, Fault-Tolerance, Concurrent Pascal.

To Pam, Mum and Dad.

### Acknowledgements

First and foremost, I should like to thank Dr. Malcolm Walker, my supervisor. The fact that he guided me through all the important stages in this project, whilst still allowing me to conduct the research in my own way, is much appreciated. Also, I should like to thank Neil Toye for attempting to restore sanity to some of the computing facilities and nearly always succeeding. I should like to thank Geoff Clarke for wire-wrapping some of the hardware. Finally, there are many people to whom I am grateful for their spiritual guidance, but particularly John Runchman and Steve Jamieson.

# List of Contents

Volume 1 - Main Text

| Introduction              | 1                                                                                                                                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lt-Tolerant Computing     | . 1                                                                                                                                                                                             |

| amic Redundancy           | 3                                                                                                                                                                                               |

| Loosely-Coupled Systems   | 3                                                                                                                                                                                               |

| Tightly-Coupled Systems   | 6                                                                                                                                                                                               |

| tic Redundancy            | 9                                                                                                                                                                                               |

| Triple Modular Redundancy | 9                                                                                                                                                                                               |

| Self-Checking Checkers    | 12                                                                                                                                                                                              |

| Alternative approach      | 14                                                                                                                                                                                              |

| s and Objectives          | 17                                                                                                                                                                                              |

| 1                         | At-Tolerant Computing<br>amic Redundancy<br>Loosely-Coupled Systems<br>Tightly-Coupled Systems<br>tic Redundancy<br>Triple Modular Redundancy<br>Self-Checking Checkers<br>Alternative approach |

# Chapter 2 Concurrent Pascal 2.1 Advantages of a High Level Language 2.2 Languages Considered

| 2.3 A B | rief Overview of Concurrent Pascal | 28 |

|---------|------------------------------------|----|

| 2.3.1   | The Language                       | 28 |

| 2.3.2   | The Implementation                 | 31 |

| 2.3.3   | Adaptability                       | 34 |

20

20

25

| Chapter 3 | Bit-Slice Hardware                     | 36 |

|-----------|----------------------------------------|----|

| 3.1 The   | principles of a Bit-Slice architecture | 36 |

| 3.1.1     | Construction of a bit-sliced ALU       | 37 |

| 3.1.2     | A Simple Bit-Slice Architecture        | 38 |

| 3.1.3     | An Advanced Bit-Slice Architecture     | 44 |

| 3.2 The   | Super Sixteen Processor                | 46 |

| 3.2.1     | Origin of the Super Sixteen            | 46 |

| 3.2.2     | Hardware Description                   | 48 |

V

| 3.2.2.1 | The Processor            | 48 |

|---------|--------------------------|----|

| 3.2.2.2 | Memory and Input/Output  | 54 |

| 3.2.3   | Control of the Processor | 56 |

| Chapter 4 Fault-Tolerance Theory                           | 61 |

|------------------------------------------------------------|----|

| 4.1 A Multiprocessor Architecture                          | 61 |

| 4.2 Microcode Tests - The Faulty Processor                 | 65 |

| 4.2.1 The Arithmetic Units                                 | 65 |

| 4.2.2 The Datapath                                         | 70 |

| 4.3 High Level Test Evaluation - the Operational Processor | 76 |

| 4.3.1 Problem Specification                                | 76 |

| 4.3.2 The Solution                                         | 79 |

| Chapter | 5 Fault     | t-Tolerance | Implementa  | ation  | 85  |

|---------|-------------|-------------|-------------|--------|-----|

| 5.1     | Assumptions | s Made      |             |        | 85  |

| 5.2     | Trapping of | f Errors    |             |        | 87  |

| 5.2     | .1 Norma    | al Error En | try         |        | 87  |

| 5.2     | .2 Timer    | r Interrupt | Test Routi  | ines   | 88  |

| 5.2     | .3 Fault    | ty Timer In | terrupt Har | rdware | 91  |

| 5.2     | .4 Fault    | ty Mapping  | PROM Decode | er     | 94  |

| 5.3     | Microcoding | g Technique | s           |        | 96  |

| 5.3     | .1 Fault    | ty Test Res | ults        |        | 96  |

| 5.3     | .2 Messa    | age Transmi | ssion       |        | 102 |

| 5.4     | Summary     |             |             |        | 106 |

| Chapter | 6 Conclusions and Proposals for Further Work | 108 |

|---------|----------------------------------------------|-----|

| 6.1     | Conclusions                                  | 108 |

| 6.2     | Suggestions for Further Research             | 110 |

| 6.2     | .1 System Improvements                       | 110 |

| 6.2     | .2 Further Research                          | 113 |

vi

# References

# Volume 2 - Appendices

| Appe | endix 1   | The Software and Firmware Development System       | 1  |

|------|-----------|----------------------------------------------------|----|

|      | 1.1 Intro | oduction                                           | 1  |

|      | 1.1.1     | A Conventional Microcode Development System - The  |    |

|      |           | AMD System 29                                      | 2  |

|      | 1.1.2     | Facilities Available                               | 6  |

|      | 1.2 The C | Concurrent Pascal Development System               | 9  |

|      | 1.3 The M | Microcode Development System.                      | 10 |

|      | 1.3.1     | Microcode Assembly                                 | 10 |

|      | 1.3.1.1   | Using an Ordinary Machine Code Assembler to        |    |

|      |           | Assemble Microcode                                 | 10 |

|      | 1.3.1.2   | Producing a Loadable File                          | 15 |

|      | 1.3.2     | Producing a Mapping PROM                           | 16 |

|      | 1.4 The H | PR 1ME-AMD Interface                               | 18 |

|      | 1.4.1     | The Motorola M6809 Microprocessor Board            | 18 |

|      | 1.4.2     | Transfer from the PR1ME to the Super Sixteen       | 20 |

|      | 1.5 Testi | ng the Microcode                                   | 21 |

|      | 1.5.1     | Intelligent Memory                                 | 21 |

|      | 1.5.2     | The Logic Analyser                                 | 23 |

|      | 1.6 Disad | avantages of this system vs. a conventional system | 24 |

|      |           |                                                    |    |

| App  | endix 2   | The P-code Interpreter                             | 26 |

|      | 2.1 Intro | oduction                                           | 26 |

|      | 2.2 Initi | Lalisation                                         | 26 |

|      | 2.3 Envir | conment Simulation                                 | 31 |

2.4 Code Interpretation 36

vii

| 2.5 Oper | rational Details        | 40 |

|----------|-------------------------|----|

| 2.5.1    | P-code Utility Programs | 40 |

| 2.5.2    | Running the Interpreter | 42 |

| 2.5.3    | Interpreter Performance | 45 |

46

Appendix 3 Interpreter Source Listings

| Appendix 4 Microcode Development System User Guide  | 90 |

|-----------------------------------------------------|----|

| 4.1 Microcode Assembly                              | 90 |

| 4.2 Generation of the Mapping PROM File             | 93 |

| 4.3 Transfer to the Motorola and Programming EPROMs | 94 |

| 4.4 Use of The Intelligent Memory                   | 98 |

# Appendix 5 Development System Listings 102

|--|

| Appendix 7 P-code Description |         |                        | 163 |

|-------------------------------|---------|------------------------|-----|

|                               | 7.1 The | P-code Machine         | 163 |

|                               | 7.2 The | P-code Instruction Set | 165 |

| Appendix 8 Concurrent P-code Documentation | 241 |

|--------------------------------------------|-----|

| 8.1 System Data Structures                 | 241 |

| 8.2 Subroutines                            | 252 |

| 8.3 Monitor Policing P-code Instructions   | 254 |

| 8.4 Process Scheduling                     | 255 |

| 8.5 Real-Time and I/O Instructions         | 258 |

# Appendix 9 Microcode Source Listings 260

| Appendix | 10 Amendments to Concurrent Pascal | 451 |

|----------|------------------------------------|-----|

| 10.1     | Sequential Pascal Programs         | 451 |

| 10.2     | The io command.                    | 452 |

| Appendix | 11 FTOS Documentation              | 454 |

| Appendix | 12 FTOS Source listings            | 465 |

| Appendix | 13 FTOS User Guide                 | 491 |

| 13.1     | The Command Interpreter            | 491 |

| 13.2     | Fault Detection and Analysis       | 496 |

# List of Diagrams

Volume 1 - Main Text

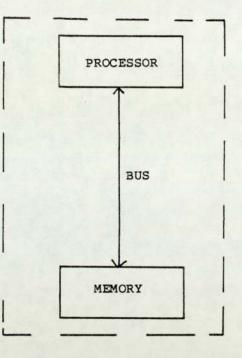

| Fig. | 1.1. Breaking a computer processor up into three conceptual |    |

|------|-------------------------------------------------------------|----|

|      | parts.                                                      | 5  |

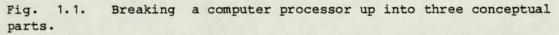

| Fig. | 1.2. An example of a loosely-coupled multiprocessor         |    |

|      | connection scheme.                                          | 5  |

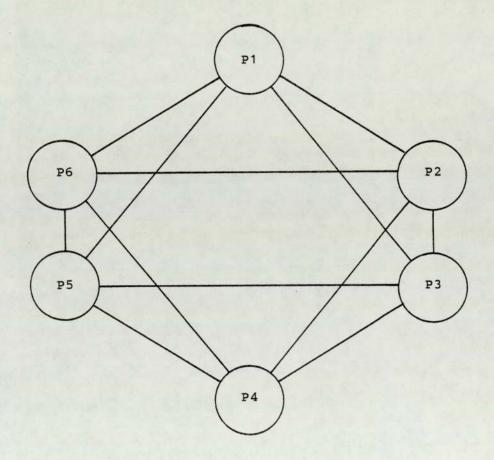

| Fig. | 1.3. An Example of a Tightly-Coupled Architecture.          | 7  |

| Fig. | 1.4. Triple Modular Redundancy.                             | 10 |

| Fig. | 1.5 a). A non-redundant ALU.                                | 10 |

| Fig. | 1.5 b). An ALU implemented using TMR.                       | 10 |

| Fig. | 1.6. Use of a self-checking checker to implement an ALU.    | 13 |

| Fig. | 1.7. A one-bit self-checking checker.                       | 13 |

| Fig. | 2.1. The three levels of Software Development.              | 21 |

| Fig. | 2.2. Implementation of a HLL.                               | 23 |

| Fig. | 2.3. A Monitor.                                             | 33 |

| Fig. | 2.4. An Access Graph of two processes P1 and P2             |    |

|      | communicating via a Monitor M.                              | 33 |

| Fig. | 2.5. A Gate.                                                | 33 |

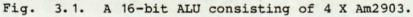

| Fig. | 3.1. A 16-bit ALU consisting of 4 X Am2903.                 | 39 |

| Fig. | 3.2. A Simple Bit-Slice Computer.                           | 45 |

| Fig. | 3.3. An Advanced Bit-Slice Architecture.                    | 45 |

| Fig. | 3.4. P-code Addressing Requirement.                         | 50 |

| Fig. | 3.5. Block Diagram of the Super Sixteen Processor.          | 51 |

| Fig. | 3.6. Constructing a 16-bit memory with word and byte        |    |

|      | addressing from 2 X 8-bit memory boards.                    | 55 |

| Fig. | 4.1. The Basic Redundancy of a High Speed Bit-slice         |    |

|      | Computer.                                                   | 63 |

| Fig. | 4.2 a). Processor Status - Both processors non-faulty.      | 63 |

| Fig. | 4.2 b). Processor Status - One processor Faulty.            | 63 |

X

| Fig. | 4.3. | Transfer of data between the ALU and the PCU.          | 66  |  |  |  |  |

|------|------|--------------------------------------------------------|-----|--|--|--|--|

| Fig. | 4.4. | Transfer of data through the Datapath.                 | 71  |  |  |  |  |

| Fig. | 4.5. | Access Graph for FTOS.                                 | 81  |  |  |  |  |

| Fig. | 4.6. | Sequential/Concurrent allocation of FTOS functions.    | 83  |  |  |  |  |

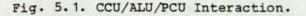

| Fig. | 5.1. | CCU/ALU/PCU Interaction.                               | 92  |  |  |  |  |

| Fig. | 5.2. | A Typical Concurrent P-code program stored in EPROM.   | 92  |  |  |  |  |

| Fig. | 5.3. | A Concurrent P-code program with no procedures.        | 92  |  |  |  |  |

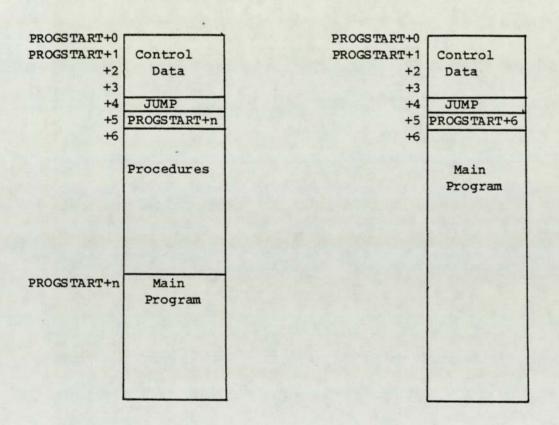

| Fig. | 5.4. | Fault detection in the Super Sixteen                   | 93  |  |  |  |  |

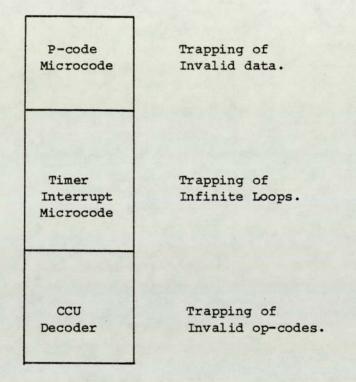

| Fig. | 5.5. | Function of the Mapping PROM Decoder.                  | 95  |  |  |  |  |

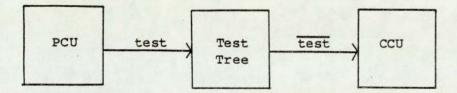

| Fig. | 5.6. | PCU/CCU Interaction. 1                                 |     |  |  |  |  |

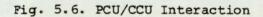

| Fig. | 5.7. | Test evaluation in the bit-sliced ALU. 1               |     |  |  |  |  |

| Fig. | 5.8. | Use of the Am2904 Test Status Multiplexer to generate  |     |  |  |  |  |

|      |      | the ALU Carry-in.                                      | 105 |  |  |  |  |

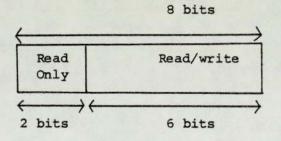

| Fig. | 5.9. | PIA Control Register.                                  | 105 |  |  |  |  |

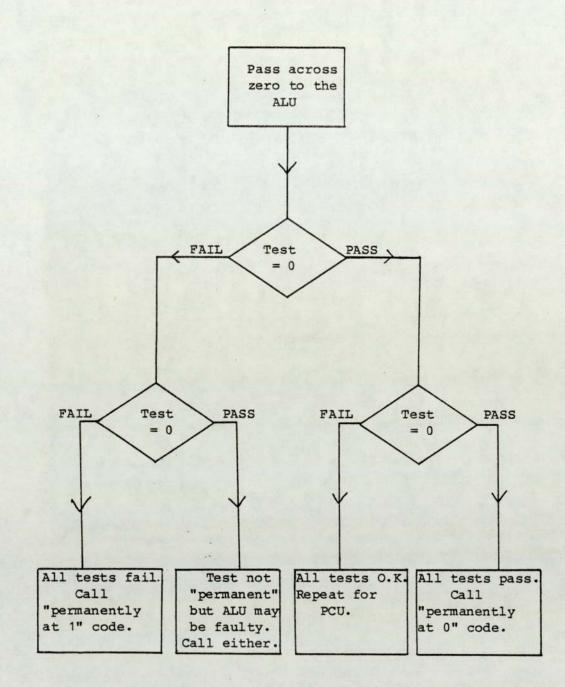

| Fig. | 6.1. | An algorithm for deciding whether to call "permanently |     |  |  |  |  |

| •    |      | at 0" microcode or "permanently at 1" microcode.       | 112 |  |  |  |  |

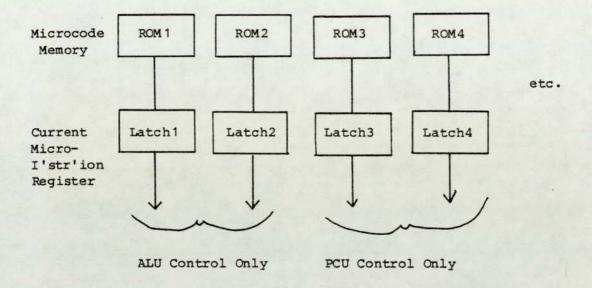

| Fig. | 6.2. | Partitioning of microcode in memory to achieve greater |     |  |  |  |  |

|      |      | reliability of the CCU.                                | 114 |  |  |  |  |

# Volume 2 - Appendices

| Fig. | 1.1. | A Conventional Firmware Development Scheme Using the |     |

|------|------|------------------------------------------------------|-----|

|      |      | AMD System 29                                        | 3   |

| Fig. | 1.2. | A Microcode Development System Using The Facilities  |     |

|      |      | Available.                                           | 8   |

| Fig. | 1.3. | Logical and Physical Microcode Format.               | 17  |

| Fig. | 2.1. | Initial Memory Structure.                            | 27  |

| Fig. | 2.2. | Initial Parameter Structure.                         | 30  |

| Fig. | 4.1. | The Transfer Switch Box.                             | 96  |

| Fig. | 7.1. | Exception handling.                                  | 168 |

| Fig. | 7.2. | The AND SET instruction.                             | 173 |

xi

| Fig. 7.3. The BUILD SET instruction.                      | 173 |

|-----------------------------------------------------------|-----|

| Fig. 7.4. The CALL PROGRAM Instruction.                   | 178 |

| Fig. 7.5. The COPY BYTE Instruction.                      | 181 |

| Fig. 7.6. The COPY REAL Instruction.                      | 181 |

| Fig. 7.7. The COPY SET Instruction.                       | 183 |

| Fig. 7.8. The COPY TAG Instruction.                       | 184 |

| Fig. 7.9. The CASE JUMP Instruction.                      | 193 |

| Fig. 7.10. The COMPARE REAL Instructions.                 | 195 |

| Fig. 7.11. The COPY STRUCTURE Instruction.                | 195 |

| Fig. 7.12. The ENTER PROCEDURE Instruction.               | 200 |

| Fig. 7.13. The ENTER PASCAL PROGRAM Instruction.          | 202 |

| Fig. 7.14. The ENTER CLASS Instruction.                   | 204 |

| Fig. 7.15. The ENTER MONITOR Instruction.                 | 206 |

| Fig. 7.16. The EXIT PROCEDURE Instruction.                | 211 |

| Fig. 7.17. The FUNCTION VALUE Instruction.                | 213 |

| Fig. 7.18. The INITIALISE CLASS Instruction.              | 215 |

| Fig. 7.19. The INITIALISE POINTER VARIABLE Instruction.   | 218 |

| Fig. 7.20. The OR SET Instruction.                        | 223 |

| Fig. 7.21. The PUSH ARRAY COMPONENT Instruction.          | 225 |

| Fig. 7.22. The SUBTRACT SET Instruction.                  | 234 |

| Fig. 7.23. The TEST IN SET Instruction.                   | 239 |

| Fig. 8.1. Concurrent Pascal Machine Memory                | 242 |

| Fig. 8.2. Concurrent P-code System Pointers.              | 244 |

| Fig. 8.3. A Gate.                                         | 244 |

| Fig. 8.4. A process Queue.                                | 246 |

| Fig. 8.5. A Process Head.                                 | 246 |

| Fig. 8.6 Allocation of Process Data Space.                | 249 |

| Fig. 8.7. Process Data Space.                             | 249 |

| Fig. 8.8 Memory-Mapped I/O Devices.                       | 250 |

| Fig. 8.9. Allocation of Concurrent and Sequential P-code. | 251 |

# List of Tables

# Volume 1 - Main Text

| Table | 3.1. | Am2903 Operand Source Control.                       | 40 |

|-------|------|------------------------------------------------------|----|

| Table | 3.2. | Am2903 Function Control.                             | 41 |

| Table | 3.3. | Am2903 Destination Control.                          | 42 |

| Table | 3.4. | PCU Register Assignment.                             | 50 |

| Table | 3.5. | Non-pipelined execution of a typical P-code          |    |

|       |      | instruction.                                         | 57 |

| Table | 3.6. | Pipelined Execution of a typical P-code Instruction. | 58 |

| Table | 4.1. | The set of microcode tests performed by the          |    |

|       |      | Faulty Processor.                                    | 74 |

| Table | 4.2. | Test Results and their Diagnosis.                    | 75 |

### Volume 2 - Appendices

| Table 4.1. | Exorciser | Memory | Assignment af | ter | Transfer. | 96 |

|------------|-----------|--------|---------------|-----|-----------|----|

|------------|-----------|--------|---------------|-----|-----------|----|

Chapter 1

#### Introduction

#### 1.1 Fault-Tolerant Computing

Today, the applications of computers in real-time systems cover a multitude of uses, especially since the advent of microprocessors. Computers are entrusted with very important tasks. These include process control applications in power stations, chemical plants and oilfields and electronic applications in telephone switching systems. Also, computers are used in space systems for controlling satellites and deep space probes.

All of these real-time systems share one basic requirement. <u>It</u> is vitally important that the control be reliable. In other words the computer controlling them must continue to function correctly at all times. In some cases this may be essential to avoid halts in production. In spacecraft control a computer fault could mean the failure of the entire mission. More importantly, in many cases it could mean the loss of human life. It is for this reason that much computing research has been aimed at producing fault-tolerant computers ([1.1] and [1.2] for example). In line with any other field of research, once a goal has been achieved further research has been conducted to try to improve the original developments.

Several different approaches have been adopted to achieve reliability in computer systems. These approaches have varied, especially since the requirements of different fault-tolerant systems vary. For example, a telephone switching system could

easily be repaired within, say, twenty-four hours, whereas a deep space probe may have to work for up to ten years without any maintenance. All of these approaches share one thing in common; to achieve fault tolerance there must be redundancy in the hardware. In other words extra hardware units must be added at some level so that if one unit fails then the others will continue to operate.

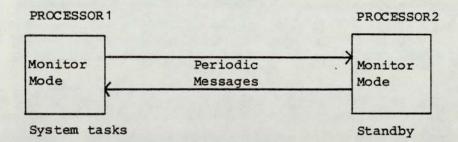

There have been two basic approaches to this problem. The first is termed dynamic or standby redundancy. This is where an outward approach is adopted. No attempt is made to improve the reliability of an individual processor or memory module. Processor units and memory modules are duplicated and some of these units remain on standby ready to take over if other units become faulty. The second approach is known as static or masking redundancy. The philosophy here is to adopt an inward approach. An attempt is made to improve the reliability of a single processor by duplicating its individual constituent components.

The following two sections in this chapter will discuss these two approaches. Following this, a common weakness of these methods is suggested and an alternative is proposed which will help to remedy this problem. Finally, in this chapter, the general aims and objectives of this project are presented.

### 1.2 Dynamic Redundancy

When dynamic redundancy is employed a single computer processor is broken down into three essential parts; the processing unit, the memory and a bus to communicate between the two (Fig. 1.1). Dynamic redundancy makes no attempt to improve the reliability of a single unit. However, all of these modules are duplicated. This reduces the probability of a catastrophic failure since if one component develops a fault then the system as a whole continues to function. Furthermore, the probability that two identical units will develop a fault during any given period is far less than the probability that one such unit will be faulty. If many more redundant units are added on to the system then multiple failures can also be accommodated. There are two classes of dynamic redundancy; tightly-coupled systems and loosely-coupled systems.

#### 1.2.1 Loosely-Coupled Systems

A loosely-coupled system is one in which complete processors are duplicated and operate with a degree of independence from one another. Each processor has its own private memory which cannot be accessed by any other processors although they would have some means of inter-communication.

The simplest form of loosely-coupled system consists of a dual processor architecture. One processing unit works in main mode and the other operates in backup mode [1.3]. The main processor performs all the functional tasks required. Whenever an alteration to any vital system data is made the backup processor will be

informed. Therefore, the backup system keeps a complete record of all the data stored on the main processor. This means that if the main processor fails, then the backup unit can assume responsibility and the system as a whole will suffer no loss of continuity or availability.

However, this system is very limited since if a fault of any kind develops then half the total processing power is immediately lost. Furthermore, it may take an appreciable time to repair the fault. There is no backup facility during this period. It is quite possible that the one remaining operational processor could develop a fault and thereafter no service would be available.

It is for these reasons that more recently developed loosely-coupled systems have used more than two processors [1.4,1.5]. The way in which they are linked together can vary considerably. If there is a reasonably large number of processors in a system then it will be impractical to connect every processing unit to every other one. Generally, therefore, some subset connection scheme is adopted whereby there is a limited number of links. Not all processors would be able to communicate directly with each other. Fig. 1.2 shows a typical example.

Needless to say, in such systems additional software is required to control the processor interaction and make them appear to higher levels as one complete unit.

One advantage of a loosely-coupled system is that if a processor does fail then it will not have access to memory other than its own. This helps to prevent propogation of errors. On the other hand, it

could be argued that since a processing module consists of a processor and a memory then the fault will have occurred in either, but not both, of these. This means that the complete processing unit, which contains either an operational processor or an operational memory, is disabled. Therefore, in hardware terms it could be argued that a fault causes twice as much damage than necessary.

### 1.2.2 Tightly-Coupled Systems

The second way that dynamic redundancy can be achieved is by means of a tightly-coupled system. This is where a multiprocessor consists of a common pool of processing units and a shared set of memory modules. All processors will have access to any memory module. The essential difference between a tightly-coupled system and a loosely coupled one, therefore, is that the former has shared memory and the latter does not.

The most common architecture employed within a tightly-coupled system is one in which processors and memory modules are connected by duplicated shared buses. Fig. 1.3 gives an example of such a scheme, although many variations are possible [1.6].

A failure of any one unit (this includes a bus failure) means that only a small part of the processor is out of service. However, there are hardware problems since the memory modules must have a separate port for each bus, i.e. a multi-port memory is required. Also, there is a very real danger of a faulty processor "running wild" and corrupting memory which is being used by other units. It

Fig. 1.3. An Example of a Tightly-Coupled Architecture.

is for this reason that hardware protection registers are employed. A processor would have to access a memory module via one of these registers. The registers would contain preset upper and lower addresses and they would not allow a processor to access an area of memory outside this range. In other words each processor has a section of memory which it is allowed to use and this protection is enforced by hardware registers. Tightly-coupled systems thus require extra hardware. On the other hand, they require less memory than loosely coupled ones.

As with loosely-coupled systems there is an additional overhead in terms of the amount of software needed to control the multiprocessor. There are many control schemes. The processors may be regarded as an anonymous pool of resources as in the Plessey System 250 [1.7, 1.8, 1.9] or they may each have separate tasks to perform as in the JPL-STAR [1.10]. Some systems use a combination of tightly and loosely coupled schemes so that there will be a pool of shared memory but each processor will also have a private store [1.11].

### 1.3 Static Redundancy

An alternative approach that has been taken to achieve fault-tolerance is to make single processors more reliable by utilising intra-processor redundancy. Rather than duplicating processors an attempt is made to maximise the internal reliability of a single processor. There are two types of static redundancy; Triple Modular Redundancy (TMR) and Self-Checking checkers.

#### 1.3.1 Triple Modular Redundancy

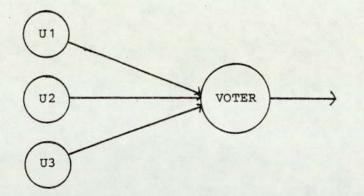

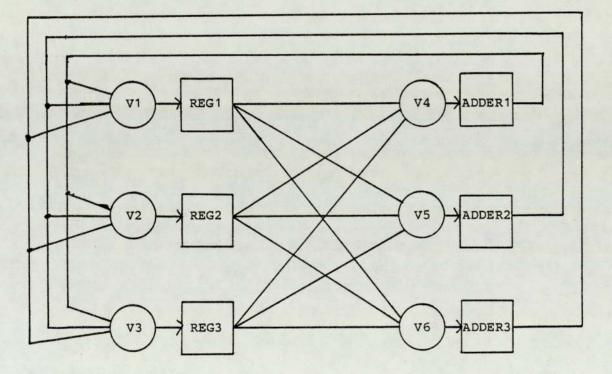

If a computer is built using Triple Modular Redundancy (TMR) then all vital components are triplicated. Also, a voting circuit is added to allow the three identical units to ignore the output from a faulty unit. In Fig. 1.4 there are three identical units; U1, U2 and U3. The voter chooses their majority output. Normally, if all units are non-faulty then all three outputs will agree. However, if one unit is faulty then the voter will choose whichever two outputs agree. If two or more units are faulty then the voter may choose the incorrect outputs.

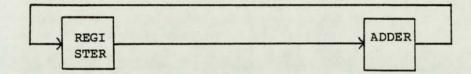

Although the failure of a single unit can be tolerated a fault in the voter will cause the circuit to fail. Fortunately, the structure of a digital computer is such that most components are constantly passing values between one another. As an example take a register and an adder (Fig. 1.5). In a normal non-redundant system the register will produce one of the inputs of the adder and the results of the addition will be placed back in the register. If the register and the adder are triplicated then there will be six

Fig. 1.4. Triple Modular Redundancy.

Fig. 1.5 a). A non-redundant ALU.

Fig. 1.5 b). An ALU implemented using TMR.

voters. Each one of these will be associated with the input to a particular unit. If a voter fails then it will have the same effect as if the unit it was feeding had failed. If, for example, in Fig. 1.5 b) the voter V1 failed then REG1 would contain incorrect data. However, this fault would not propogate since the three voters feeding the adders would mask out the incorrect data.

TMR is, in one sense, an ingenious solution since it requires no additional software and can tolerate any single fault within each sub-system. TMR can even be used at higher levels since the units which were given as examples in Fig 1.5 could equally well have been processors and memories [1.12]. TMR, however, does require an increase in hardware by a factor of greater than three. This is because voting circuitry is required in addition to triplication of units. This increase in hardware can increase the probability of a fault occurring and although the system can tolerate this, it could not withstand a multiple failure. In order to be able to tolerate two faults of any description five units of each type would be required. TMR, therefore, although requiring no extra software, requires a large increase in the amount of hardware.

#### 1.3.2 Self-Checking Checkers

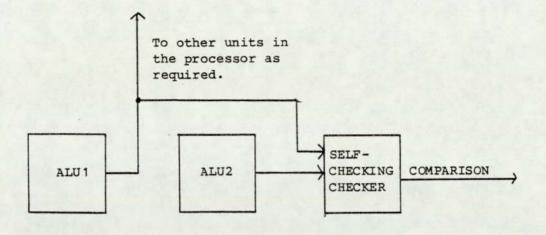

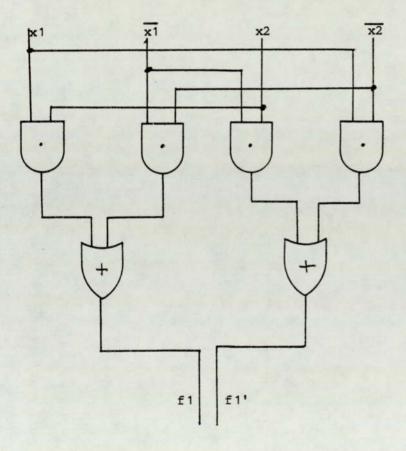

Another form of static redundancy which can be a useful aid for fault-diagnosis is in the use of self-checking checkers [1.13]. In this situation a functional unit within a processor is duplicated but only one of the two units produces an output which is used by other parts of the processor. The second redundant unit is used to check the output of the first one, using a self-checking checker. Fig. 1.6 gives an example of this using an ALU. A self-checking checker produces one particular output if the two units agree and another output if they disagree or the checker itself is faulty. The circuitry becomes more complicated when comparing 'n' bits but the manner in which it operates can be illustrated in Fig. 1.7. This shows a self-checking checker for comparing the two bits x1 and x2. It can be seen by examination that if x1 = x2 then the outputs (f1, f1') will be either (0, 1) or (1, 0). If the outputs (f1, f1') of the checker are either (0,0) or (1,1) then either its two inputs are unequal or the checker itself is faulty. A description of how this is implemented for n-bit comparisons can be found in [1.14].

Unlike the other methods described so far in this chapter self-checking checkers are used to assist in fault diagnosis rather than fault tolerance. This is nevertheless useful for two reasons. First, it is important to be able to detect and diagnose a fault when it occurs in order to isolate it. Second, failed components can be replaced more quickly, thus reducing the probability of multiple faults. Self-checking checkers perform a similar function to parity and error-code checks, both of which are well established and documented [1.15]. However, self-checking checkers are more reliable since they can detect faults of any multiplicity [1.14,

Fig. 1.6. Use of a self-checking checker to implement an ALU.

Fig. 1.7. A one-bit self-checking checker.

1.16, 1.17, 1.18].

### 1.4 An Alternative approach

There are many variations on the basic themes described in the previous two sections. However, it is hoped that this chapter has outlined the various methods that can be used to achieve All of the approaches discussed require a fault-tolerance. disproportionate amount of resources to achieve fault-tolerance when compared with normal systems capable of performing the same tasks without fault tolerance. These methods always require additional hardware to achieve redundancy and they may, in many cases, require special software. Furthermore, a situation is rapidly reached where the addition of further hardware produces very little increase in reliability. The author believes that some so called non-redundant systems contain a certain amount of duplication. This can be regarded as a form of redundancy if used correctly. If this were exploited fully it would help to reduce the amount of redundancy required at other levels using the methods that have been described. This section will attempt to outline the rationale behind this statement.

Consider an ordinary computer processor which is made up from thousands of components. A failure of any one of these will render this processor useless although the vast majority of its components are still operational. Since these components are mutually interactive and dependant it would be impossible to isolate a fault at this level. However, if a processor is regarded as being split up into a few separate subsystems then the same argument can be

applied. A processor could, for example, be regarded as being split up into a memory module, a bus, an arithmetic unit and a control unit. If the memory bus were to become faulty then the processor as a whole would be inoperable. However, the processor, consisting of a control unit and an arithmetic unit would still be functioning correctly. Once it is unable to access memory to obtain the instructions the complete processor becomes inoperable.

In the past it has been practical to regard a computer system as being made up of two essential elements; hardware and software. An additional, third element is used in many digital systems; firmware.

If a computer processor employs a microprogrammed control structure [1.19] then it will be arranged as follows. A11 sub-systems within the processor such as the ALU, the memory, etc. will be directly under the control of the Microprogram Control Unit (MCU). The MCU consists of the microcode memory together with some means of sequencing the accesses to this memory (the Microcode Sequencer). Each word of microcode memory consists of a series of bits (ones and zeroes) which will be routed directly to the sub-system they are controlling. Since there can be many sub-systems with several functions a fairly large number of control pulses are required. The length of a word of microprogram memory can be quite large when compared to main memory (usually between 64 and 128 bits). However, the number of words required is comparatively small (typically between 1/2K and 4K). Consequently, the addressing mechanism tends to be fairly simple.

There are two advantages to a structure of this type when used

with fault-tolerance. First, since the MCU is relatively simple in terms of its addressing mechanism it is less likely to develop a fault than other functional units. Second, if the main memory does become inaccessible then the MCU offers an alternative source of control. This source is located entirely within the processor itself. Consequently, it may be able to make use of the sub-systems within the processor that are still operational.

Some commercially available computers already employ a technique known as micro-verification. This involves checking the hardware status of the machine at microcode level. One example of this is the current PR1ME range of minicomputers [1.20]. The microverify routines on the PR1ME consist of a set of 11 tests. These are always executed at the start of the power-on sequence. They can also be explicitly called by the operator at the control console and they are also called in the event of a processor parity error being detected. If a test fails then the machine will halt and the number of the failed test can be displayed on the front panel of the machine (assuming it is still operational).

These tests consist of passing values through various registers and of testing buses, ALU functions (add, subtract, shift etc.), parity, the I/O bus, and main memory. These tests prevent a faulty machine from being put into operation after being powered up, thus preventing it from corrupting vital data in areas such as the backup store.

### 1.5 Aims and Objectives

Microcoded control can take place to a limited extent under degraded conditions on commercially available computers. This indicates that it is a viable proposition to investigate its further use in fault-tolerant systems. It would be useful to analyse thouroughly the structure of a microcoded computer to see how its architecture can be used to obtain a level of fault-tolerance. The limited scope of a project such as this means that the amount of time available is small. It is for this reason that two specifications of the research to be carried out should be as follows. First, only one existing computer architecture will be selected and analysed rather than proposing a general theory of fault-tolerance. Second, the research, when completed, will be in such a state that it will be easy for subsequent researchers to continue the work.

After a processor architecture has been selected and analysed a basic fault-tolerance philosophy for this type of microcoded machine will be derived. Following this, an attempt will be made to implement it. It is felt by the author that this is important for two reasons. First, since little work has been done in this field it would be prudent to prove by experimentation that any principles derived are correct. Second, it could be useful for future researchers to have access to a working system. This could be used as a vehicle for further research.

There are two ways in which the proposed research could be carried out. The system can either be simulated or the appropriate hardware can be built. Simulation is a powerful tool. However, it was rejected for the following reasons :-

1) Simulation requires powerful computing facilities. It was felt that the level of detail involved in such a simulation would result in considerably more computing power being required than was available.

2) The structure of any processor, chosen for simulation, would involve several layers. In addition to the hardware levels there would need to be simulation of the microcode, machine code and (possibly) the high level language. This could be a complex structure to simulate.

3) It was felt that considerable benefit would be gained by designing and implementing a processor, rather than merely simulating the structure.

4) This processor would then be available for future work.

A means is required whereby a fault-tolerant computer system can be built economically, but which uses an architecture that is specific to requirements. One of the developments in commercial microprocessors in recent years has been the advent of bit-slice computers. Bit-slice elements allow a computer designer to implement a processor from individual sub-systems. This can be done using commercially available devices rather than buying a complete "off the shelf" processor. In order to be able to define the architecture of a processor completely the designer needs to be able to specify the machine instruction set. Consequently, a microprogrammed control structure is an inherent requirement of a bit-slice processor. This would, therefore, make an ideal vehicle on which to conduct the proposed research.

Some research has already been conducted in this area [1.18]. The approach that will be adopted here will vary from this earlier work. First, the research already carried out used some additional hardware. Second, a faulty sub-system attempted to analyse itself by using its own internal components. The approach described in this thesis allows a faulty sub-system to be analysed by external functional units. Therefore, the difference between these two approaches is that the fault diagnosis will operate at different levels. More importantly, an attempt will be made to maximise the degree of fault tolerance available from an existing architecture without using any additional hardware.

The rest of this thesis describes the work that has been undertaken. Chapters 2 and 3 describe the decisions that were made in choosing a suitable design and also describe the system itself. Chapter 4 describes the fault-tolerant principles derived and Chapter 5 outlines the problems that were found when an attempt was made to implement them. Finally, a conclusion is presented in Chapter 6.

### Concurrent Pascal

### 2.1 Advantages of a High Level Language

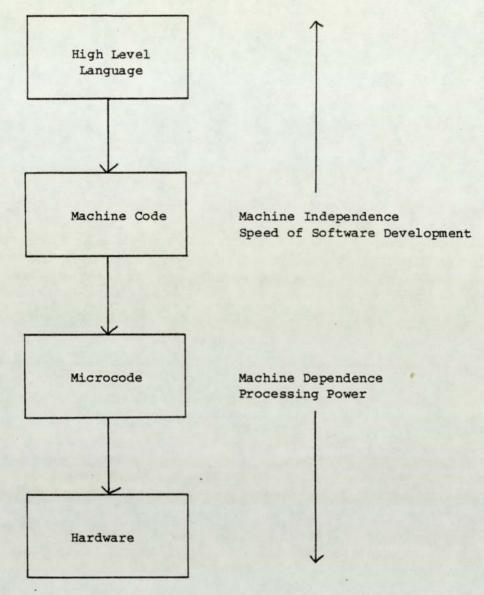

An important decision that had to be made at the beginning of this research project was whether the multiprocessor, when built, should have the ability to support a High Level Language (HLL). Since the hardware was to be built from Bit-slice components the system programming could take place at either HLL, machine code or microcode level (Fig. 2.1). A HLL programming capability does not diminish the ability to program at other levels.

As one moves from a high to a low level there is a decrease in software productivity and an increase in the amount of detailed machine knowledge required. The advantages of programming in a HLL are obtained at the expense of code efficiency. The amount of time taken to process any given algorithm written in microcode is significantly shorter even than in machine code but a detailed knowledge of the processor architecture is needed. At machine code level it is usual to require only an awareness of the register transfers that take place within the computer. However, machine code is still one and a half to two times faster in execution than a good real-time language. If a HLL is used then virtually no knowledge of the machine architecture is required. All that might be necessary are any specific details that are peculiar to the language implementation on the particular machine. It will be shown in Section 2.3 and Appendix 11 that, in the solution eventually adopted, these are negligible. The one level of software which

```

High Level

```

Low Level

Fig. 2.1. The three levels of Software Development.

could not be entirely eliminated is the microcode level. This is because whatever permutation of the three levels is used they must be implemented in firmware.

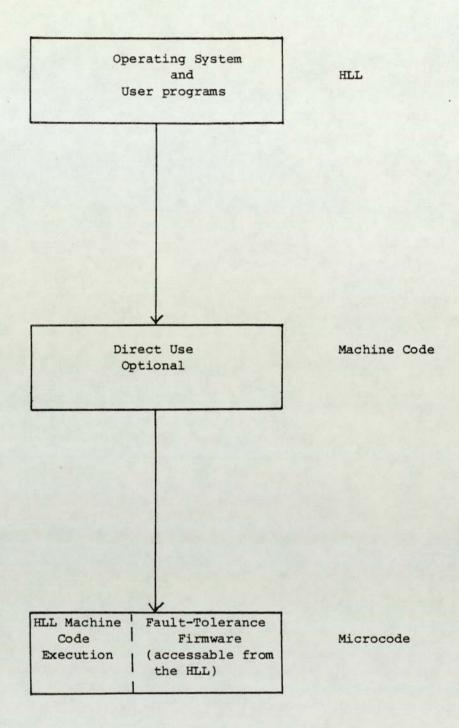

If a HLL is implemented in microcode (Fig 2.2), as opposed to machine code on a conventional non-microprogrammable processor, it can be more efficient. This is because an optimum machine instruction set can be chosen as the compiled and executable form of Furthermore, once the basic firmware implementation of the code. the HLL has been achieved it would be possible for much of the development to be performed at a high level. This would make it possible for any future researchers to continue with the project and program the computer with no knowledge of the machine architecture being required. The use of a HLL, therefore, would give an enhanced rate of code development with the first steps being undertaken in microcode and the latter stages using a HLL. The choice of whether to use machine code need not be taken until the HLL has been implemented. Once a HLL capability has been attained the ability to program in machine code still remains. However, the use of machine code is at the software designers discretion.

The use of microcode at low level can be used to advantage in providing fault-tolerant test routines. If a set of fault-tolerance routines are imbedded in the firmware and can be called from higher levels then the effectiveness of these routines can be efficiently evaluated. This can be done, for example, by calling them at different times and in different orders. Again, this is merely an option while the HLL is being developed. The software designer is still able to write code at the microprogram level after a HLL has been implemented.

Fig. 2.2. Implementation of a HLL.

To summarise then, a HLL implemented in microcode minimises the loss in processing power whilst retaining the speed of software development attributed to such a tool. It would make the system more approachable to new researchers. Also, it would allow certain software design decisions, such as where the fault-tolerance code should appear and the expandability of the system, to be deferred until after the HLL had been implemented.

It was therefore decided that the processor should have the ability to execute programs written in a HLL. One of the main arguments which influenced this decision was that a microcode implementation could be very efficient. It was felt necessary to choose the HLL before the processor architecture was selected. This was because an architecture which could efficiently execute the HLL was required. The main indicator of whether a processor structure is suitable is the run-time machine code produced by the HLL compiler. It was therefore necessary to select a processor architecture that was well matched to the run-time machine code. This made the choice of a suitable HLL the next logical step in the research.

## 2.2 Languages Considered

A suitable language for this type of project would be, as the title of this thesis suggests, one designed for a real-time application. Alternatively, a systems programming language could be suitable. In order to achieve a working system within the timescales allowed, it was important to choose a language which had a readily available compiler and needed little effort to transport it. Therefore, in the end, practical considerations prevailed in choosing between theoretically equally matched languages.

Five languages were investigated for use on this project. They were CORAL 66 [2.1], RTL/2 [2.2], MODULA [2.3,2.4,2.5], ADA [2.6] and CONCURRENT PASCAL [2.7].

Coral 66 was the oldest of the languages. It has been a popular real-time language for many years, especially in industry. It was felt, however, that a more modern language with greater flexibilty should be employed.

The second real-time language that was considered was RTL/2. This was a language that was rapidly gaining popularity and was quite suitable. It was more modern than Coral in its design philosophy. There was also a good portable compiler available.

Another language that was considered was the most recently designed of, the five; Ada. It was designed as a general-purpose language and incorporated facilities normally found in both real-time and system-programming languages. Unfortunately, Ada was so new that no compiler existed and, although it would have been highly suitable, it was immediately discounted.

The fourth language that was investigated was Modula which was designed as an operating systems language and was based on Pascal. The structure of the language was such that it was possible to maximise the amount of software written in Modula and minimise the amount written in machine code. Modula is a multiprocessing language and embodies the concept of concurrent processes. At the time of the investigation the author was not aware of the location of any readily available compilers.

The final language that was considered was Concurrent Pascal which was also based on Pascal. It was designed for implementing small operating systems and was therefore suitable for the application required. Again, like Modula, Concurrent Pascal is a multiprocessing language. However, the multiprocessing concepts are applied in different ways. It is beyond the scope of this text to critically compare Modula and Concurrent Pascal but the author preferred the approach to multiprocessing that the latter took. Also, Concurrent Pascal was found to be more readable. These factors, combined with the lack of availability of a compiler for Modula, led the author to select Concurrent Pascal out of the two multiprocessing languages.

Having eliminated Modula for the above mentioned reasons, Coral on the grounds of its age and Ada due to the lack of a compiler the author was left with a choice between RTL/2 and Concurrent Pascal. The factor which eventually swayed the balance was not the high level features of the languages but an aspect at a lower level. In order to achieve portability both RTL/2 and Concurrent Pascal use

Intermediate Level Languages (ILL). The ILL used by Concurrent Pascal, called P-code, is at a lower level than the one used by RTL/2. P-code is actually a hypothetical machine code. This means that it would not be necessary to design a machine instruction set if Concurrent Pascal were used. This would mean that there would be one fewer task to perform, thus allowing more time and effort to be spent on the fault-tolerance aspect of this project. Designing a machine instruction set to implement a HLL is difficult in terms of achieving the optimum solution. Also, P-code is based on a zero-addressing (or stack-machine) architecture which is particularly efficient for the execution of a high-level block-structured language such as Pascal [2.8].

Therefore, the use of Concurrent Pascal would ensure that by writing microcode to execute P-code an efficient implementation of the language could be obtained. This fact, coupled with the relative ease of obtaining and transporting a compiler, led to its selection as the HLL to be used. However, this choice virtually closed another design option. P-code, although very suitable for the execution of a HLL, should not be considered as a general purpose programming language. This is because the programmer needs to keep track of the current state of a frequently used stack. Also, P-code makes many more memory (stack) accesses than a normal 1 or 2-addressing machine code. These memory accesses would occur in any implementation of a block-structured language but not in software written directly in machine code. There would therefore be very little gain in processing speed obtained by writing software directly in P-code. This meant that it was only practical to write software at the HLL or the microcode level. This restriction did not seem to be particularly important for two reasons. First, an

extremely efficient implementation of the HLL would be obtained. This meant that some code requiring fast processing could be written in Concurrent Pascal. Second, programs which would normally be written in machine code could be implemented in microcode which is faster.

# 2.3 A Brief Overview of Concurrent Pascal

## 2.3.1 The Language

In subsequent chapters a description of the high-level, fault-tolerance software will appear. In this section a description of the basic concepts of Concurrent Pascal will be presented. Hopefully, this will help to give the reader an understanding of the design decisions that were taken. For a more detailed description of Concurrent Pascal the reader should consult [2.9].

Per Brinch Hansen, the designer of Concurrent Pascal claims that his aims were to achieve simplicity, reliability, adaptibility, portability, efficiency and generality. The language was designed for implementing small operating systems, although Brinch Hansen has stated that it could be used for larger operating systems. This has been done to implement a time-sharing system in [2.10]. The language is based on the well-known and popular Pascal programming language. The language is structured so that the hub of the operating system is written in Concurrent Pascal and all the user and application programs are written in Sequential (ordinary) Pascal. One of the main aims of the language is to ensure that any time-dependent, and possibly non-predictable, errors caused by concurrency cannot occur. To this end, the language depends very

heavily on the compiler to trap any such potential errors, thus reducing or even eliminating them.

Concurrent Pascal extends Sequential Pascal by the use of three concepts, Processes, Monitors and Classes.

A typical Concurrent Pascal program would consist of two or more processes each one merely being a piece of code. All processes would run concurrently. Thus, for example, one process might handle input, another run user programs and a third handle output.

The main problem that occurs with concurrency is that of process communication. In order to achieve this, processes must share data in memory. However, if they attempt to write to a shared-data area simultaneously then it may be corrupted. There are several means of overcoming this, Concurrent Pascal uses Monitors as a solution.

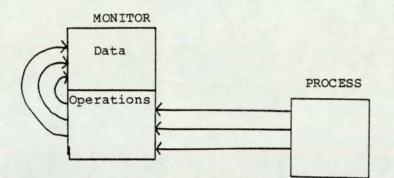

A Monitor consists of some data (in the form of VAR declarations) and some operations (in the form of Procedures) to access this data. A process that uses a Monitor cannot access its data directly, it can only call the operations that act upon this data (Fig 2.3). To ensure that there are no concurrency problems, only one process can use the Monitor at a time. If a Process attempts to call a Monitor which is already being used then it must enter a queue and await its turn to obtain exclusive access.

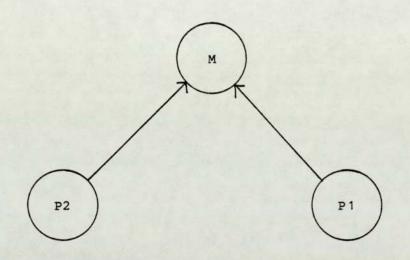

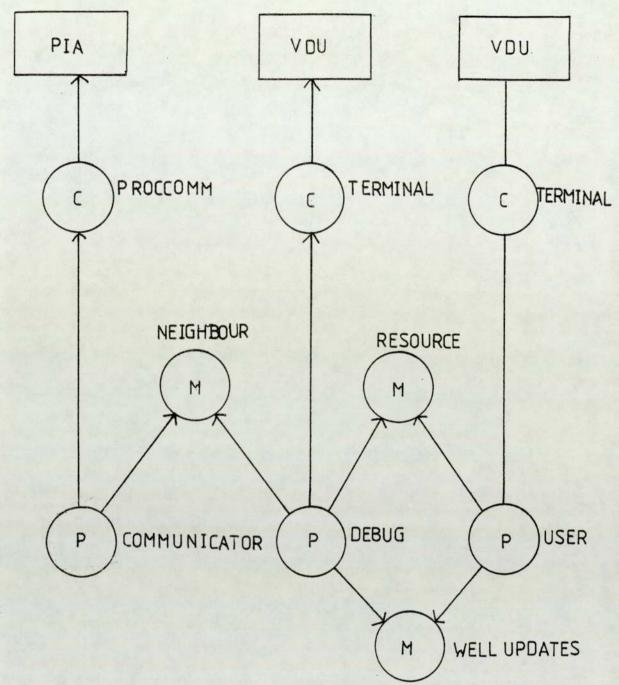

The way that Processes communicate to each other via Monitors can be shown diagramatically using access graphs (Fig 2.4).

Therefore, in this way, only one Process can access a shared

data area at a time. However, a Process is unaware of the detailed structure of the data. For example, a Monitor might consist of a buffer (an array) together with a set of operations. There might be an operation to read an item from the buffer and another one to write to the buffer. It is because a Process is only aware of the existence of data and not its structure that Monitors are referred to as Abstract Data Types.

Because a Monitor call carries a large run-time overhead another structure called a <u>Class</u> is also employed. This is similar to a Monitor as it contains some data and a set of operations to act upon the data. However, it is ensured at compile time that only one Process has access to a Class. A Class therefore posseses the data abstraction of a Monitor but it reduces the run-time overhead. This concept has been adapted from the language Simula 67 [2.11].

There are also some Process scheduling facilities in Concurrent Pascal. Suppose a Process calls a Monitor to read an item from a buffer which is empty. A Monitor has the ability to <u>Delay</u> the Process using a <u>Queue</u> which is simply another variable type. When the buffer becomes full again (i.e. another Process puts data into it) the Monitor has the ability to Continue a Delayed Process.

There also exists a real-time primitive called <u>Wait</u> which delays the calling Process for one second, thus allowing long-term real-time scheduling.

A Concurrent Pascal program has the ability to call a Sequential Pascal program in virtually the same way as it might call a Procedure. However, it is responsible for first ensuring that the Sequential Pascal program is ready to run. For example, by reading it in from disc into memory.

## 2.3.2 The Implementation

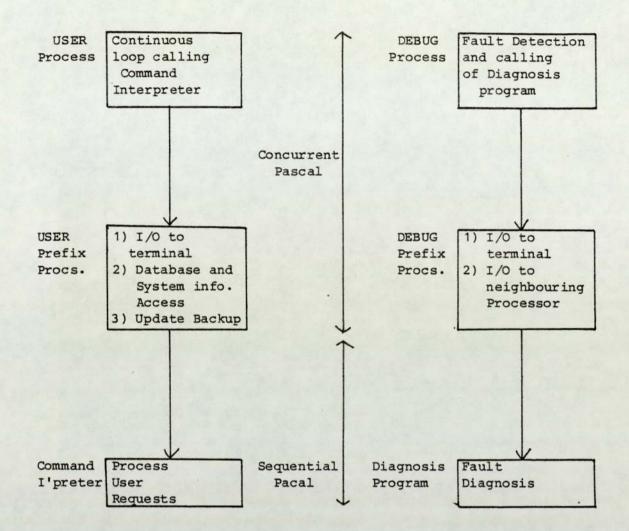

The implementation of Concurrent Pascal is somewhat different to that of conventional sequential programming languages. For example, an ordinary implementation of Pascal would only require some means of executing P-code. This would be performed either using an interpreter, a translator or by direct execution with microcode. in addition, Concurrent Pascal requires a means of However, executing its additional Concurrent P-code instructions. One possible method is to write an interpreter for the Sequential P-code and a Kernel for the Concurrent P-code. This classic approach was adopted in the original implementation and also by most subsequent users of the language [2.12, 2.13]. Brinch Hansen acknowledges that interpretation results in a loss of efficiency which can be eliminated if a firmware implementation is employed. It has already been stated that this method would be adopted on this project. To the author's knowledge this is the first approach of this type which has been attempted, although firmware implementation of ordinary Pascal has been achieved [2.13]. Also, [2.14] did adopt a compromise approach of microcoding frequently used Sequential P-code instructions. Therefore, it is felt that the implementation deserves some mention as it adds an extra element of originality to the project.

The implementation of the Sequential P-code was fairly straightforward although time-consuming and is fully documented in Appendices 7 and 9. The Kernel is the part of the microcode that makes a single processor appear as a multiprocessor with one processing unit for each process. This is done by multiplexing the single available processor between the software processes defined in the high-level program. The Kernel is also responsible for policing Monitor usage, this is done by means of a structure called a Gate (Fig. 2.5). This consists of a boolean variable called OPEN which indicates whether the Monitor is in use and an array in which Processes can be queued. If a Process calls a Monitor the Kernel checks to see if it is in use. If it is, the caller is put in the queue. Whenever a process leaves a Monitor the next one in the queue is allowed to enter the monitor.

The Kernel is also responsible for the real-time facilities such as the Wait directive and must therefore maintain a record of the time. In addition, it is responsible for input and output.

Therefore, it can be seen that the Kernel constitutes the core of an operating system consisting of process scheduling, shared-data access policing, real-time facilities and input/output. The extra operating system features required are overlayed onto this using high-level Concurrent-Pascal code. Since parts of the operating system are written in microcode they are very efficient. The operating system interface between the high-level code and the microcode is by means of P-code instructions (Enter Monitor, Leave Monitor, Initialise process etc.). This notion of having low-level scheduling operations that can be called from a higher level was also adopted in the only other microcode implementation of a scheduler that the author is aware of [2.15].

Fig. 2.3. A Monitor.

Fig. 2.4. An Access Graph of two processes P1 and P2 communicating via a Monitor M.

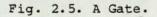

| OPEN  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QUEUE | and the second se |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Therefore, the kernel is (in this case) a microprogrammed implementation of the concurrent aspects of the language. It is the part of the implementation that tends to be altered by new users of the language in order to achieve any changes required [2.10]. It is also, in this case, an unusual approach to writing an operating system by using microcode. A detailed description of the Kernel can be found in Appendices 8 and 9.

# 2.3.3 Adaptability

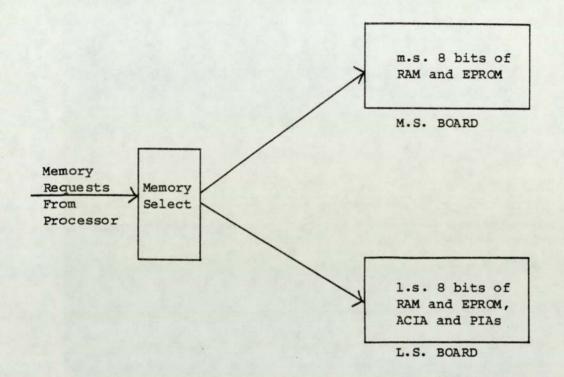

Concurrent Pascal had been originally designed to run on minicomputers with many peripherals such as disc drives, paper and magnetic tape etc. The implementation required here was on a smaller system, as described in Section 3.2, whose only i/o was either to a terminal or to another processor. In addition, it was not possible to store Sequential Pascal programs on disc and read them into memory before execution. All code, both Concurrent and Sequential, was stored on EPROM. These were machine details that were impossible to hide from the software programmer. They affected two areas of the high-level software, namely the "io" command which was responsible for input/output and also the mechanism for calling Sequential Pascal programs. The project already required a diversified knowledge of hardware, firmware and software. Therefore, the author felt that it would not be practical to alter the Concurrent Pascal compiler as well. Fortunately, Concurrent Pascal proved sufficiently flexible to be able to alter machine details without amending the language definition.

The input/output directive, io, is called with three parameters.

As a special case the compiler performs no type checking on these parameters. It merely generates P-code to push them on the stack and make an "io" call on the Kernel. This means that it was only necessary to define the new i/o operations within the Kernel. Meaningful names can be given to the values required as parameters in the high level code using standard Pascal "type" and "const" declarations. This approach was taken from [2.10].

The calling of programs also required no alteration to the language, only its implementation had to be changed. Both of these machine-dependent modifications are defined formally in Appendix 10.

# Bit-Slice Hardware

# 3.1 The principles of a Bit-Slice architecture

The term "Bit-Slice" is derived from the fact that a basic processing element comes in a package with a small bit width. To implement a larger unit of the same description several of these devices would be cascaded together. For example, to construct a 16-bit ALU, 4 X 4-bit sub-units would be used. These devices have various inputs which control such factors as the function to be performed, the data to be operated on and where the results should be stored. For an ALU the functions would include adding, subtracting, shifting right and left and so on. The data to be operated on could come from internal registers or an external source. If the former is chosen then the register number must be specified. The outputs should also be to an internal register or an external destination. Connecting the control inputs of these devices to the microcode memory gives the microcode control unit complete command over the operation of the ALU.

One of the main manafacturers of bit-sliced products is Advanced Micro Devices (AMD) whose components were used in the design of the hardware to be described. The following descriptions draw freely on technical specifications from the Am2900 range of bit-slice devices. Further details of these components are given in [3.1]. A further description of bit-slice principles can be found in [3.2].

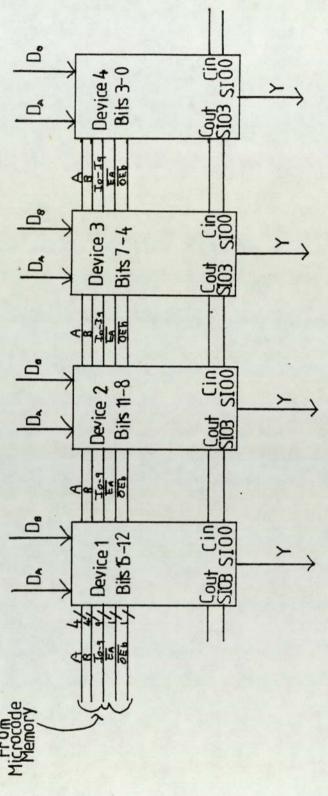

# 3.1.1 Construction of a bit-sliced ALU

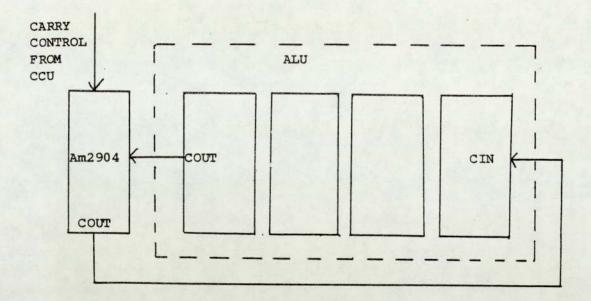

A 16-bit ALU which has been constructed from 4 X Am2903 bit-slice devices is shown in Fig. 3.1. Since the four devices are meant to act as one unit they must perform the same operation on data from the same sources. The Am2903 has 16 internal registers and any two of them can be accessed at a time. Accordingly, the control pins of the Am2903 have 4-bit A and B register select fields which indicate the register to be operated on. In order to make sure that each device operates on the same registers the field select control pins on each chip are connected together. There are 9 ALU function and destination control signals. These are designated I0 to I9 and the corresponding pins on each package are connected together. IO to I4 control the function (add, subtract etc.) and I5 to I8 determine the destination (whether to latch the result into a register, whether to shift it, etc.). All these functions are defined fully in Tables 3.2 and 3.3. The source of data is defined by the Ea OEb and IO signals which are connected together on each device. The sources available are defined fully in Table 3.1, they include an internal ALU register or one of the two external Da or Db inputs. Typically, these would be connected to a source such as the memory data register. Each bit-sliced device would receive 4 bits of this data. Any outputs, as well as being latched into registers, would appear at the Y outputs of these devices. All of the control inputs described above are connected to the microcode instruction register. This gives the microcode complete control over the ALU.

Whenever there is a device boundary two things must happen to make the ALU function correctly :-

1) Any data which overflows in an arithmetic operation in one device must be added on to the value in the next most significant sub-unit. Accordingly, the Carry Out (Cout) output of each device is connected to the Carry In (Cin) input of its most significant neighbour.

2) Any data shifted out of one device must be shifted in to the next one. Accordingly, the shift-out outputs of each sub-unit (SIO3 = Shift Out Left, SIO0 = Shift Out Right) are connected to the shift-in inputs of its neighbour (SIO0 = Shift In Left, SIO3 = Shift In Right). This allows the ALU to perform 16-bit shifts.

The above is a simplistic description of how large units may be constructed from smaller components and how the microcode controls them.

## 3.1.2 A Simple Bit-Slice Architecture

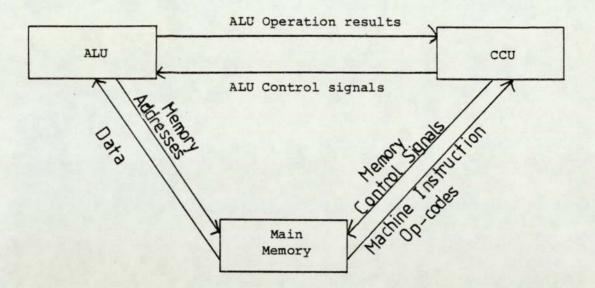

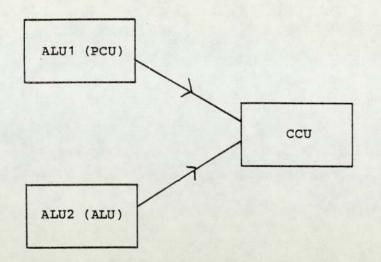

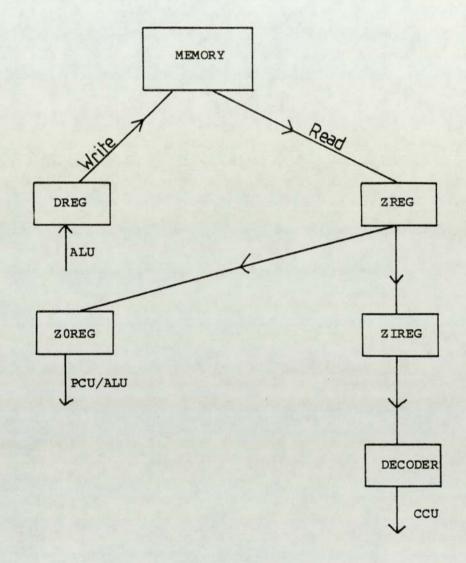

A very simple bit-slice computer will consist of three basic functional units; the Computer Contol Unit (CCU), the Arithmetic and Logic Unit (ALU) and the main memory (Fig. 3.2).

The CCU consists of the microcode which is usually stored in ROM, it is not related to main memory where the machine code is contained. There must also be some means of sequencing the microcode. This entails generating the next microinstruction address, allowing for conditional jumps, subroutines and other transfers of control. The CCU is at the heart of a bit-slice computer. It directs all the other components by means of control

Microinstruction Format

A

8

Io - I.

GB

B

| Ea | IO | OED | ALU operand R   | ALU Operand S   |

|----|----|-----|-----------------|-----------------|

| L  | L  | L   | A-port Register | B-port Register |

| L  | L  | H   | A-port register | DB              |

| L  | H  | х   | A-port Register | Q Register      |

| H  | L  | L   | DA              | B-port Register |

| H  | L  | H   | DA              | DB              |

| H  | H  | x   | DA              | Q Register      |

Note 1) L = LOW, H = HIGH, X = DON'T CARE.

2) The Q Register is an extra internal scratch register independent of the 16 RAM registers. It can be written to or read from.

Table 3.1. Am2903 Operand Source Control.

| 14 | 13 | 12 | I1 | IO | ALU Functions            |

|----|----|----|----|----|--------------------------|

| L  | L  | L  | L  | L  | Special Functions        |

| L  | L  | L  | L  | H  | Fi = HIGH                |

| L  | L  | L  | H  | x  | F = S - R - 1 + Cin      |

| L  | L  | H  | L  | х  | F = R - S - 1 + Cin      |

| L  | L  | H  | H  | x  | F = R + S + Cin          |

| L  | H  | L  | L  | х  | F = S + Cin              |

| L  | н  | L  | H  | X  | $F = \overline{S} + Cin$ |

| L  | H  | Н  | L  | L  | Reserved                 |

| L  | Н  | Н  | L  | H  | F = R + Cin              |

| L  | H  | H  | H  | L  | Reserved                 |

| L  | Н  | Н  | Н  | Н  | $F = \overline{R} + Cin$ |

| Н  | L  | L  | L  | L  | Reserved                 |

| Н  | L  | L  | L  | H  | Fi = LOW                 |

| H  | L  | L  | H  | х  | Fi = Ri AND Si           |

| н  | L  | H  | L  | x  | Fi = Ri EXCLUSIVE NOR Si |

| H  | L  | H  | H  | x  | Fi = Ri EXCLUSIVE OR Si  |

| H  | H  | L  | L  | х  | Fi = Ri AND Si           |

| H  | Н  | L  | H  | x  | Fi = Ri NOR Si           |

| н  | Н  | H  | L  | x  | Fi = Ri NAND Si          |

| H  | H  | Н  | H  | х  | Fi = Ri OR Si            |

# Note

1) L = LOW, H = HIGH, X = DON'T CARE.

2) i = 0 to 3.

3) ALU Special Function details have been ommitted for the sake of simplicity.

Table. 3.2. Am2903 Function Control

| 18 | 17 | 16 | 15 | Destination                                                  |

|----|----|----|----|--------------------------------------------------------------|

| L  | L  | L  | L  | Arithmetic Shift Right, store result in B-port<br>Register   |

| L  | L  | L  | н  | Logical Shift Right, store result in B-port Re<br>gister     |

| L  | L  | H  | L  | Arithmetic Shift Right, store result in B-port<br>Register * |

| L  | L  | H  | H  | Logical Shift Right, store result in B-port Re<br>gister *   |

| L  | H  | L  | L  | No Shift, store result in B-port Register                    |

| L  | H  | L  | H  | No Shift, result goes to YBUS only *                         |

| L  | H  | H  | L  | No Shift, store result in Q Register                         |

| L  | н  | н  | H  | No Shift, store result in B-port and Q Registe rs            |

| H  | L  | L  | L  | Arithmetic Shift Left, store result in B-port<br>Register    |

| H  | L  | L  | H  | Logical Shift Left, store result in B-port Reg<br>ister      |

| H  | L  | н  | L  | Arithmetic Shift Left, store result in B-port register *     |

| H  | L  | H  | н  | Logical Shift Left, store result in B-port reg<br>ister *    |

| н  | H  | L  | L  | No Shift, result goes to YBUS only                           |

| н  | H  | L  | H  | No Shift, result goes to YBUS only *                         |

| H  | H  | H  | L  | Sign extend, result goes to B-port Register                  |

| н  | H  | H  | H  | No Shift, result goes to B-port Register                     |

Note 1) L = LOW, H = HIGH, X = DON'T CARE

2) Destinations marked '\*' also shift the Q Register independently of the main ALU results. Details have been ommitted for simplicity.

3) Details of the sign extend facility and parity generation have also been ommitted.

4) All results appear on the YBUS regardless of I8 - I5

Table 3.3. Am2903 Destination Control

signals directly connected from the current microinstruction register to the control inputs of the various devices within the processor.

The ALU is responsible for all the various arithmetic operations required. These fall into three categories:-

1) Those that are implicit to a certain machine-code instruction (e.g. "ADD", "SUB" etc.).

2) The generation of addresses for memory read and write operations. This would include incrementing the program counter before fetching the next machine code instruction. Also, incrementing and decrementing the stack pointer.

The generation of any addresses explicit in a machine code instruction.

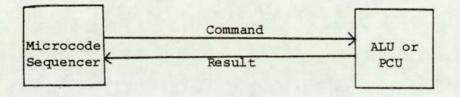

The ALU receives control signals from the CCU such as the operation required (Add, Subtract etc.) and the data sources (memory, internal registers etc.). In return it sends back the result of any operations (>0, <0, =0 etc.). This enables the CCU to make conditional jumps based on these results.

Finally, the main memory is used to store the computer program, consisting of machine code instructions, together with any data that is required. It receives control signals from the CCU (memory request, read/write etc.).

At the start of a power-on sequence the CCU instructs the ALU to generate the address for the first machine-code instruction. After this has been done a memory-read request is made. The first

instruction will then be read from memory. After this, a Decoder in the CCU will translate its op-code into a microcode memory address. This will correspond to the location where the microcode to execute the current machine instruction is stored. After its execution has taken place, the microcode sequencer will jump to the the fetch cycle microcode. Typically, this would consist of incrementing the program counter (a register in the ALU) or generating a jump address, requesting a memory read and decoding the op-code as before. The next instruction would then be executed and control would continue in this manner.

# 3.1.3 An Advanced Bit-Slice Architecture

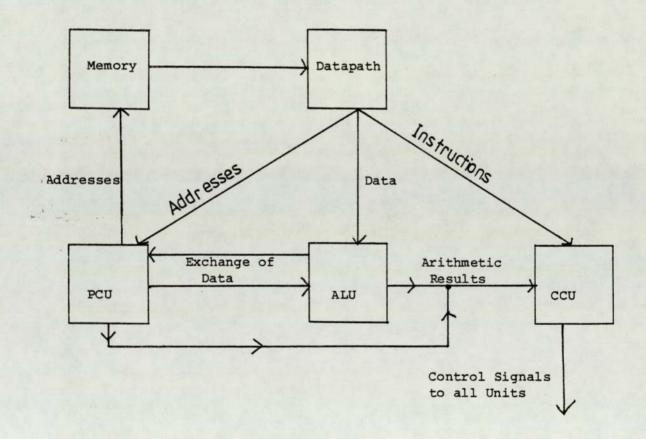

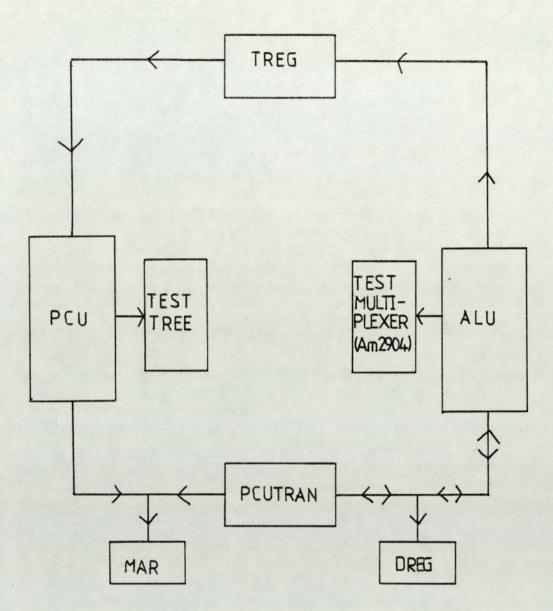

In order to produce a faster and more efficient processor the technique of machine-code pipelining would be adopted in a bit-slice architecture. This is achieved by adding two extra functional sub-systems to the computer; a Program Control Unit (PCU) and a Datapath (Machine Instruction Pipeline) as shown in Fig. 3.3.

The philosophy behind speeding up the processor is quite simple. There are two Arithmetic Units, one generates the program counter addresses and the other one performs the arithmetic operations required by the machine code. This means that there is no need to wait until the current instruction is executed before the next one is fetched. It can be done simultaneously. This notion can be taken even further since there are two steps involved in a fetch cycle; forming the address and then reading the instruction. A pipelined machine will be performing three functions at any one time. It will be executing the current instruction, reading the

Fig. 3.2. A Simple Bit-Slice Computer.

Fig. 3.3. An Advanced Bit-Slice Architecture.

next one and generating the address for the succeeding instruction.

This process clearly speeds up the processor as long as the machine code is reasonably sequential. If there are many jumps at machine-code level then the advantage tends to be lost. This is because the processor is not aware of the jump until the instruction is executed. By this time the next instruction has been fetched and the address for its successor has been generated. Both of these must be discarded. However, a pipelined processor would still be as fast as a non-pipelined machine even if every instruction was a jump.

Because concurrency exists in the processor design another sub-system is required. This would be where data, which has been read from memory and is waiting to be processed, can be stored. To do this the Datapath is introduced. This is merely a series of registers in which values read from memory can be "pipelined" en route to one of the ALUS or the CCU.

# 3.2 The Super Sixteen Processor

## 3.2.1 Origin of the Super Sixteen

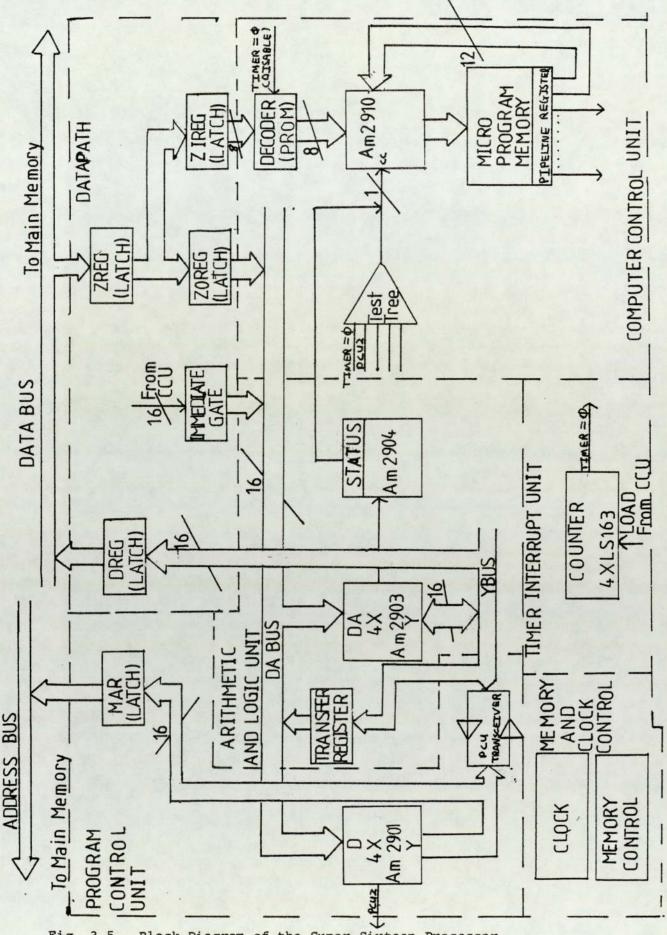

The Super Sixteen processor was obtained from [3.2]. It had been originally designed to demonstrate the principles of a microprogrammed system. In particular, it used appropriate techniques to maximise the processor's throughput. Accordingly, it uses two arithmetic units; the main ALU and the Program Control

Unit (PCU) which generates memory addresses.